# **Tiny Tapeout 04 Datasheet**

Project Repository https://github.com/TinyTapeout/tinytapeout-04

March 25, 2025

Contents

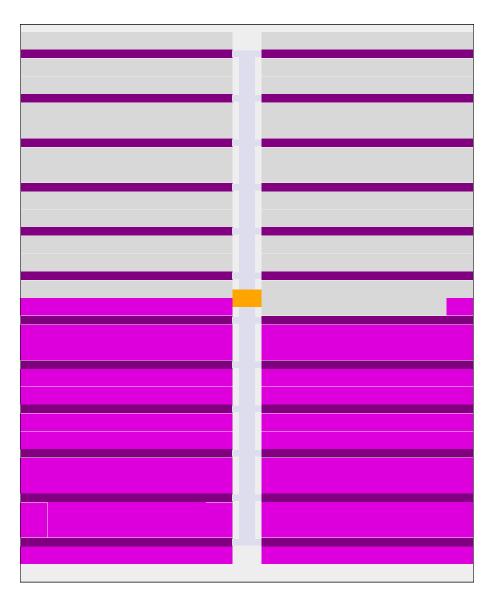

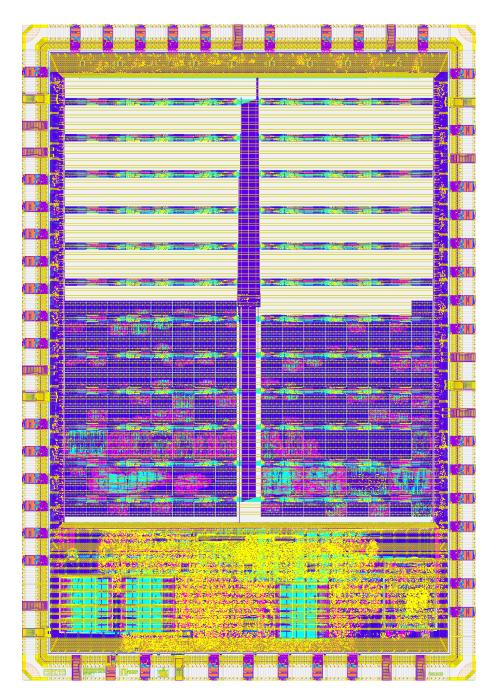

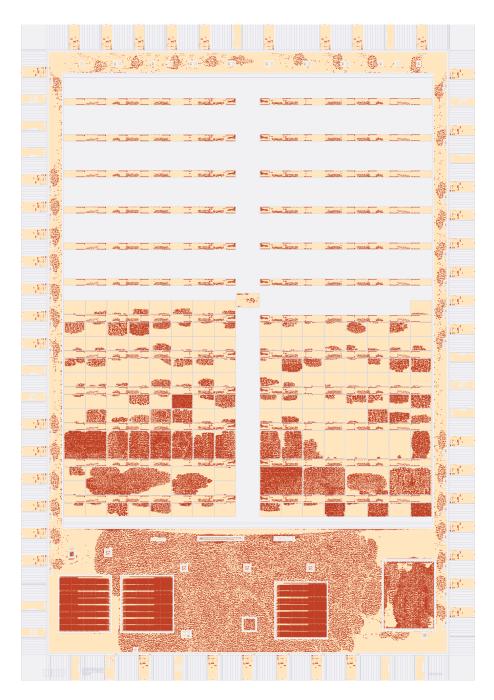

# Chip map

| Projects                                             | 9  |

|------------------------------------------------------|----|

| Chip ROM [0]                                         | 9  |

| TinyTapeout 04 Factory Test [1]                      | 11 |

| VGA clock [2]                                        |    |

| 7 segment seconds [3]                                | 14 |

| Number Factorizer [4]                                | 16 |

| Odd even sorter [5]                                  | 19 |

| The Bulls and Cows game [6]                          |    |

| VGA Output for Arduino [16]                          | 22 |

| Digital Cipher & Interlock System [17]               |    |

| Simon Says game [18]                                 |    |

| YKM 7-seg driver [19]                                |    |

| Configurable PID Block [20]                          |    |

| PWM audio [21]                                       |    |

| 4-bit ALU [22]                                       |    |

| RGB Mixer [23]                                       |    |

| raybox-zero [33]                                     |    |

| ChipTune [37]                                        |    |

| OpenSource PWM Peripheral [48]                       |    |

| Experiment Number Six: Laplace LUT [50]              |    |

| Karplus-Strong String Synthesis [52]                 |    |

| USB Device [54]                                      |    |

| Audio-PWM-Synth [64]                                 |    |

| German Traffic Light [71]                            |    |

| Dandy VGA [96]                                       |    |

| Tiny Breakout [98]                                   |    |

| VC 16-bit CPU [99]                                   |    |

| Risc-V Nano V $\begin{bmatrix} 1\\100 \end{bmatrix}$ |    |

| USB CDC (Serial) [101]                               |    |

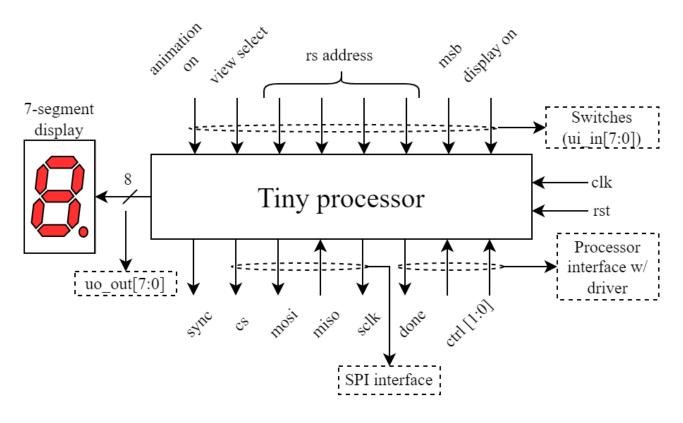

| Tiny processor $102$                                 |    |

| fft-4-tt [103]                                       |    |

| LED Panel Driver [112]                               |    |

| OSU Counter [113]                                    |    |

| Even digits [114]                                    |    |

| Traffic light [115]                                  |    |

| Tutorial4 [116]                                      |    |

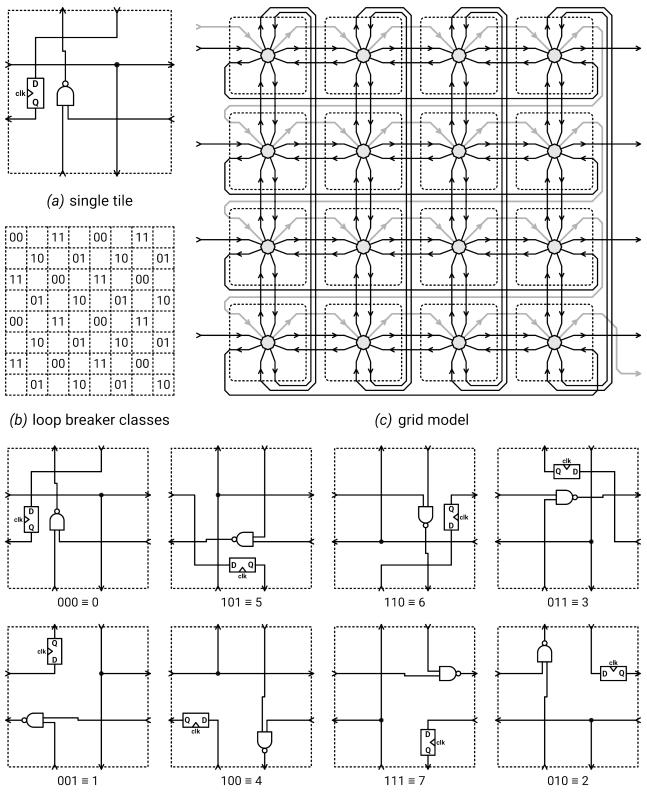

| Grain-Flex-FPGA [117]                                |    |

| BFCPU [118]                                          |    |

| Al Decelerator [119]                                 |    |

| Tiny (3-bit) LFSR [160]                              |    |

6

| Pulsed Plasma Thruster (PPT) Controller [161]                            | 86         |

|--------------------------------------------------------------------------|------------|

| SAP-1 CPU [162]                                                          | 88         |

| Multi-channel pulse counter with serial output, v01a [163]               | 90         |

| Delay Line [164]                                                         | 92         |

| Simple Piano [165]                                                       | 95         |

| Ripple-Carry Adder [166]                                                 | 97         |

| Led Multiplexer Display [167]                                            | 98         |

| LED Matrix Driver [176]                                                  | 99         |

| 8-bit FIFO with depth 16. [177]                                          | 101        |

| Pong [178]                                                               | 103        |

| 8 panel display"" [179]                                                  | 107        |

| Traffic Light [180]                                                      | 108        |

| Model Railway turntable polarity controller [181]                        | 109        |

| Customizable UART string tx [182]                                        | 113        |

| 7-Seg 'Tiny Tapeout' Display [183]                                       | 115        |

| UART character tx [192]                                                  | 117        |

| Padlock [193]                                                            | 119        |

| 8bits Counter by AI [194]                                                | 120        |

| FM Transmitter [195]                                                     | 121        |

| Test 4x4 memory [196]                                                    | 123        |

| ROTFPGA v2 [197]                                                         | 125        |

| Arithmetic logic unit of four operations between two 8-bit numbers [198] | 129        |

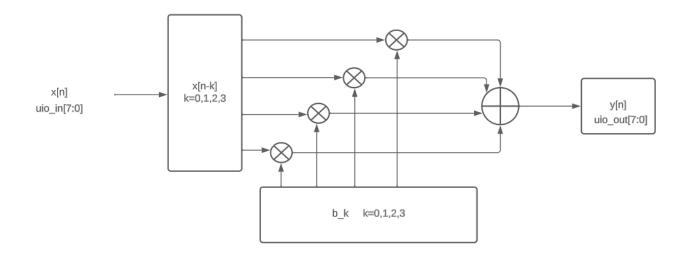

| FIR Filter [199]                                                         | 131        |

| Tamagotchi [208]                                                         | 133        |

| LFMPDM (Lightning Fast Matrix Programmable Design Module) [209]          | 135        |

| 7 SEGMENTS CLOCK [210]                                                   | 136        |

| Multi Pattern LED Sequencer [211]                                        |            |

| Generador de PWM [212]                                                   |            |

| Multi stage path for delay measurements. [213]                           |            |

| ASCII Text Printer Circuit [214]                                         |            |

| Clock synchronizer [215]                                                 |            |

| Simple PWM Generator [224]                                               |            |

| CLK Frequency Divider [225]                                              |            |

| UIS Traffic Light [226]                                                  |            |

| 4 bit adder [227]                                                        |            |

| 8-bit ALU [228]                                                          |            |

| Collatz Conjecture [229]                                                 |            |

|                                                                          |            |

| 8 bit 4 data sorting network [230]                                       | 156        |

| 8 bit 4 data sorting network [230]                                       |            |

| BCD to 7 segments [231]                                                  | 157        |

|                                                                          | 157<br>158 |

| BCD to 7 segments [231]                                                  | 157<br>158 |

| Sumador/Sustractor de 3 bit con acarreo y prestamo [243]    | 162 |

|-------------------------------------------------------------|-----|

| Hardware Lock [244]                                         | 164 |

| Custom falling and rising edge detection [245]              | 165 |

| 4-bit-alu [246]                                             | 166 |

| Angardo's pong [247]                                        | 168 |

| (11,7) hamming code encoder and decoder with UART [256]     | 169 |

| Multi-channel pulse counter with serial output, v01b [257]  | 171 |

| State machine of an impulse counter [258]                   | 173 |

| Logic Circuit 1 [259]                                       | 175 |

| Variable Duty-Cycle TRNG [260]                              | 176 |

| Pseudo Random Number Generator [261]                        |     |

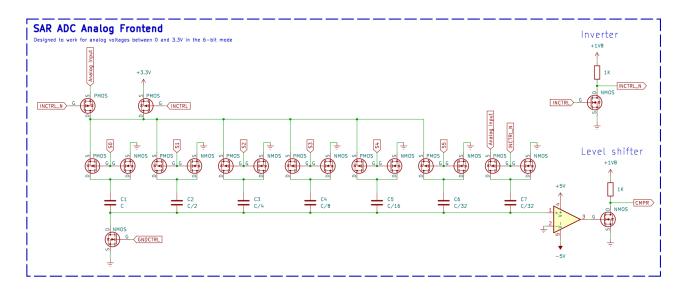

| SAR ADC Backend [262]                                       | 180 |

| FCFM 7-segment display [263]                                | 182 |

| another ring oscillator based temperature sensor [272]      | 183 |

| RO-based temperature sensor with hysteresis [273]           | 185 |

| Microrobotics FSM [274]                                     | 187 |

| MINI ALU [275]                                              | 188 |

| PWM Quisquilloso [276]                                      | 189 |

| CPU 8 bit [277]                                             | 190 |

| A Risc-V Instruction memory i2c programmer [278]            | 191 |

| IFSC 6-bit Locker [279]                                     | 193 |

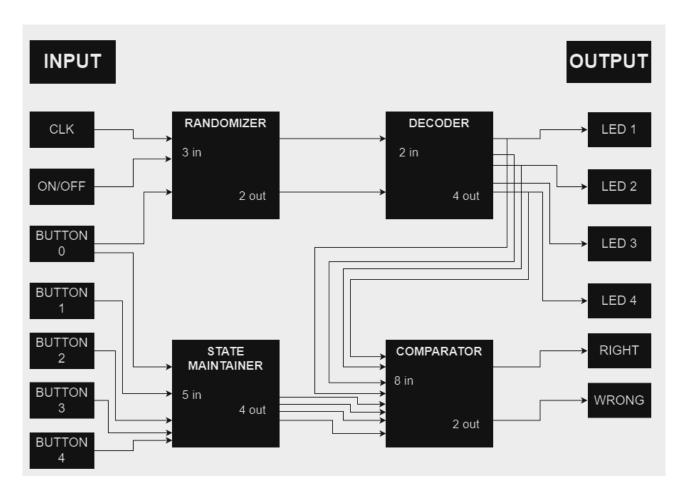

| Randomizer and status checker [288]                         |     |

| Simulador de cruzamento de semáforo [289]                   | 198 |

| Full_adder_carry_juang_garzons [290]                        | 200 |

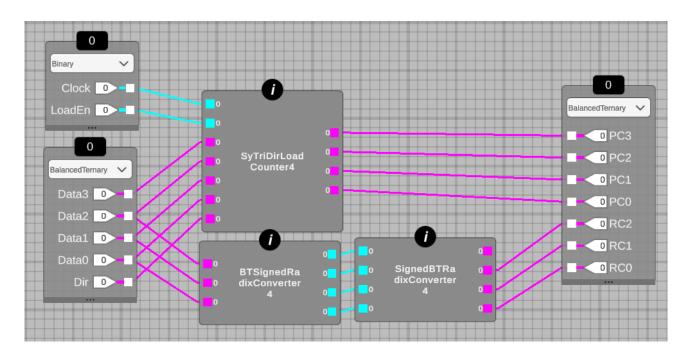

| 4-trit balanced ternary program counter and convertor [291] | 201 |

| uDATAPATH_Collatz [292]                                     | 203 |

| Adder [293]                                                 |     |

| Binary to 7 segment [294]                                   |     |

| Neuron [295]                                                |     |

| Later [304]                                                 |     |

| serializer [305]                                            |     |

| 4-bits 1-channel PWM and ALU 4 bits [306]                   |     |

| up-down counter with parallel load and BCD output [307]     |     |

| Later [308]                                                 |     |

| Contador con carga [309]                                    |     |

| onehot_decoder [310]                                        |     |

| CDMA Transmitter/Receiver [311]                             |     |

|                                                             |     |

| clock divider [320]                                         |     |

| reciprocal [321]                                            |     |

| Later [322]                                                 |     |

| Time Multiplexed Nand-gate [323]                            |     |

| Octal classifier [324]                                      | 222 |

| MULDIV unit (4-bit signed/unsigned) [325] | 223 |

|-------------------------------------------|-----|

| RS Write Decodifier [326]                 |     |

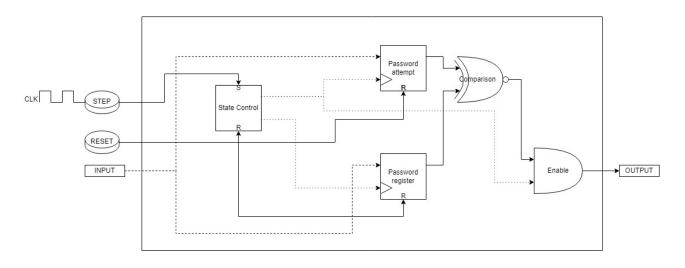

| Password FSM [327]                        |     |

| Priority e [336]                          |     |

| frecuencimeter [337]                      |     |

| Ifsr random number generator [338]        |     |

| i2c_6 bits [339]                          |     |

| Fastest Finger [340]                      |     |

| Fastest Finger (Clocked) [341]            | 233 |

| Oscillators II [342]                      |     |

| Simple ALU [343]                          |     |

| TinyTapeout 04 Loopback Test Module [352] |     |

| Adjustable Frequency LED Chaser [353]     |     |

| Simple QSPI DAC [354]                     |     |

| AQALU [355]                               |     |

| Simple TMR [356]                          |     |

| Poor Person's Boundary Scan [357]         |     |

| Probador de lógica básico [358]           | 247 |

| LIF Neuron, Telluride 2023 [359]          |     |

| rusty_adder [368]                         |     |

|                                           |     |

| Pinout                                    | 251 |

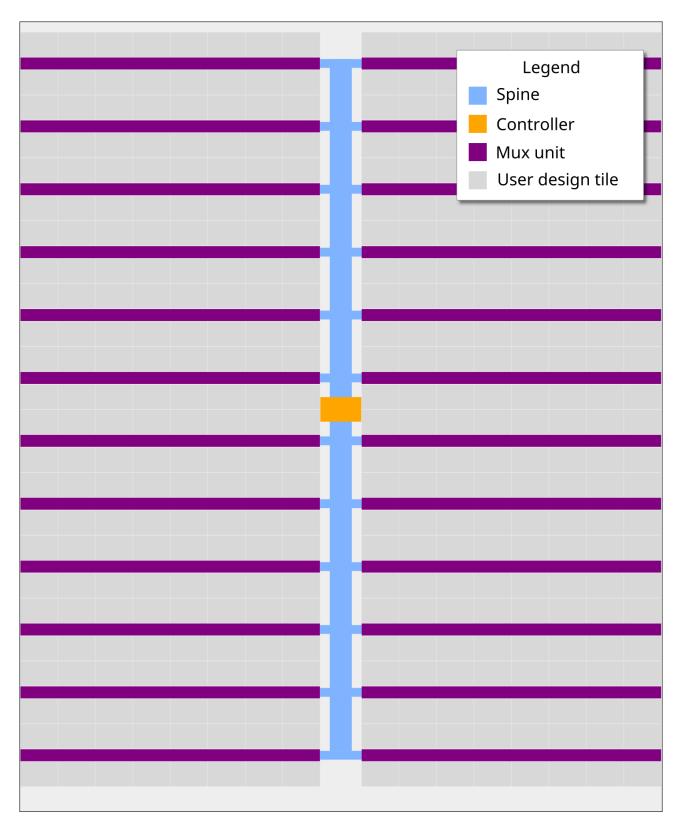

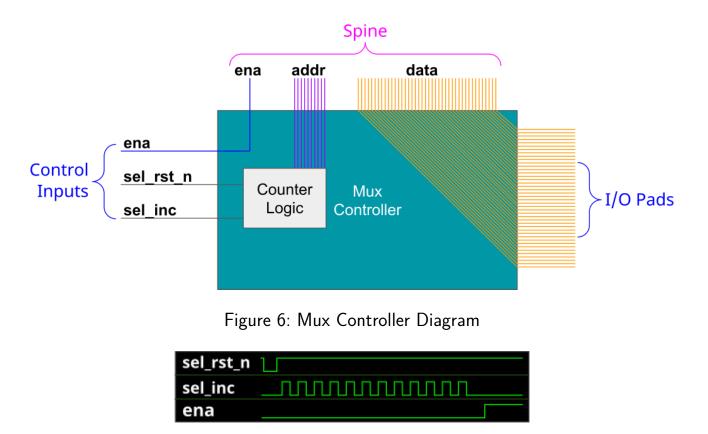

| The Tiny Tapeout Multiplexer              | 252 |

| Overview                                  | 252 |

| Operation                                 | 252 |

| Pinout                                    | 255 |

| Chin Erreto                               | 750 |

| Chip Errata                               | 258 |

| Undefined pin states                      | 258 |

| Sponsored by                              | 259 |

| Team                                      | 259 |

# Chip map

Figure 1: Full chip map

Figure 2: GDS render

Figure 3: Logic density (local interconnect layer)

# Projects

# Chip ROM [0]

- Author: Uri Shaked

- Description: ROM with information about the chip

- GitHub repository

- HDL project

- Mux address: 0

- Extra docs

- Clock: 0 Hz

- External hardware:

### How it works

ROM memory that contains information about the Tiny Tapeout chip. The ROM is 8-bit wide and 128 bytes long.

| The ROM layout | The ROM layout is as follows: |

|----------------|-------------------------------|

|----------------|-------------------------------|

| Address | Length | Encoding  | Description                             |

|---------|--------|-----------|-----------------------------------------|

| 0       | 8      | 7-segment | Shuttle name (e.g. "tt04"), null-padded |

| 32      | 96     | ASCII     | Chip descriptor (see below)             |

**The chip descriptor** The chip descriptor is a simple null-terminated string that describes the chip. Each line is a key-value pair, separated by an equals sign. It contains the following keys:

| Key     | Description                   | Example value              |

|---------|-------------------------------|----------------------------|

| shuttle | The identifier of the shuttle | tt04                       |

| repo    | The name of the repository    | TinyTapeout/tinytapeout-04 |

Future Tiny Tapeout shuttles may add more keys to the chip descriptor.

Here is a complete example of a chip descriptor:

```

shuttle=tt04

repo=TinyTapeout/tinytapeout-04

```

### How to test

Read the ROM contents by setting the address pins and reading the data pins. The first eight bytes of the ROM are 7-segment encoded and contain the shuttle name. You can read them by toggling the first four DIP switches and observing the on-board 7-segment display.

| # | Input   | Output  | Bidirectional |

|---|---------|---------|---------------|

| 0 | addr[0] | data[0] | none          |

| 1 | addr[1] | data[1] | none          |

| 2 | addr[2] | data[2] | none          |

| 3 | addr[3] | data[3] | none          |

| 4 | addr[4] | data[4] | none          |

| 5 | addr[5] | data[5] | none          |

| 6 | addr[6] | data[6] | none          |

| 7 | addr[7] | data[7] | none          |

# TinyTapeout 04 Factory Test [1]

- Author: Sylvain Munaut

- Description: Factory test module

- GitHub repository

- HDL project

- Mux address: 1

- Extra docs

- Clock: 0 Hz

- External hardware:

### How it works

If input 0 is high, then a counter is output on the outputs and the bidirectional outputs. Otherwise the inputs are mirrored to the outputs.

#### How to test

Set input 0 high. Check the outputs are toggling.

| # | Input           | Output                                                      | Bidirectional |

|---|-----------------|-------------------------------------------------------------|---------------|

| 0 | sel / data_i[0] | data_o[0] (when<br>sel=0) /<br>counter_o[0] (when<br>sel=1) | counter_o[0]  |

| 1 | data_i[1]       | data_o[1] (when<br>sel=0) /<br>counter_o[1] (when<br>sel=1) | counter_o[1]  |

| 2 | data_i[2]       | data_o[2] (when<br>sel=0) /<br>counter_o[2] (when<br>sel=1) | counter_o[2]  |

| 3 | data_i[3]       | data_o[3] (when<br>sel=0) /<br>counter_o[3] (when<br>sel=1) | counter_o[3]  |

| # | Input     | Output                                                      | Bidirectional |

|---|-----------|-------------------------------------------------------------|---------------|

| 4 | data_i[4] | data_o[4] (when<br>sel=0) /<br>counter_o[4] (when<br>sel=1) | counter_o[4]  |

| 5 | data_i[5] | data_o[5] (when<br>sel=0) /<br>counter_o[5] (when<br>sel=1) | counter_o[5]  |

| 6 | data_i[6] | data_o[6] (when<br>sel=0) /<br>counter_o[6] (when<br>sel=1) | counter_o[6]  |

| 7 | data_i[7] | data_o[7] (when<br>sel=0) /<br>counter_o[7] (when<br>sel=1) | counter_o[7]  |

# VGA clock [2]

- Author: Matt Venn

- Description: Shows the time on a VGA screen

- GitHub repository

- HDL project

- Mux address: 2

- Extra docs

- Clock: 31500000 Hz

- External hardware: R2R dac for the VGA signals

### How it works

Races the beam! Font is pre generated and loaded into registers. 6 bit colour keeps register count low.

### How to test

Hook up a VGA monitor to the outputs and provide a clock at 31.5 MHz. Connect the 6 bit colour output up with resistors to make a R2R DAC. See the circuit here: https://github.com/mattvenn/6bit-pmod-vga

| # | Input          | Output | Bidirectional |

|---|----------------|--------|---------------|

| 0 | clock          | hsync  | none          |

| 1 | reset          | vsync  | none          |

| 2 | adjust hours   | r0     | none          |

| 3 | adjust minutes | r1     | none          |

| 4 | adjust seconds | g0     | none          |

| 5 | none           | g1     | none          |

| 6 | none           | b0     | none          |

| 7 | none           | b1     | none          |

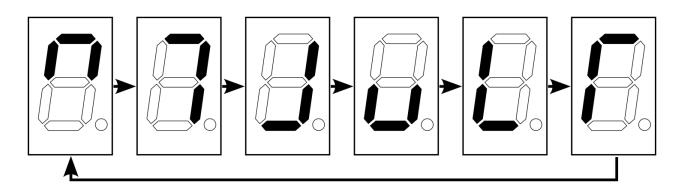

# 7 segment seconds [3]

- Author: Matt Venn

- Description: Count up to 10, one second at a time.

- GitHub repository

- HDL project

- Mux address: 3

- Extra docs

- Clock: 10000000 Hz

- External hardware:

### How it works

Uses a set of registers to divide the clock, and then some combinational logic to convert from binary to decimal for the display.

Puts the bottom 8 bits of the counter on the bidirectional outputs.

With all the inputs set to 0, the internal 24 bit compare is set to 10,000,000. This means the counter will increment by one each second.

If any inputs are non zero, then the input will be used as an bits 11 to 18 of the 24 bit compare register. Example: setting the inputs to 00010000 will program 16384 into the compare register. With a 10MHz clock the counter will increment  $\sim$ 610 times per second.

### How to test

After reset, the counter should increase by one every second with a 10MHz input clock. Experiment by changing the inputs to change the counting speed.

| # | Input          | Output    | Bidirectional          |

|---|----------------|-----------|------------------------|

| 0 | compare bit 11 | segment a | second counter bit 0   |

| 1 | compare bit 12 | segment b | second counter bit $1$ |

| 2 | compare bit 13 | segment c | second counter bit 2   |

| 3 | compare bit 14 | segment d | second counter bit 3   |

| 4 | compare bit 15 | segment e | second counter bit 4   |

| 5 | compare bit 16 | segment f | second counter bit 5   |

| # | Input          | Output    | Bidirectional        |

|---|----------------|-----------|----------------------|

| 6 | compare bit 17 | segment g | second counter bit 6 |

| 7 | compare bit 18 | dot       | second counter bit 7 |

# Number Factorizer [4]

- Author: Marno van der Maas

- Description: Takes the input and computes its factors

- GitHub repository

- HDL project

- Mux address: 4

- Extra docs

- Clock: 1000000 Hz

- External hardware: seven-segment display

#### How it works

This design uses a set of registers to compute the modulo of all factors up to 19 in one or two steps. The modulus of non-trivial numbers is calculated using the following trick:

The values of  $2^x$  % k can be computed ahead of time and are hardcoded in the design. Also we don't actually care about the modulus but rather about when the modulus is equal to zero, because that means that k is a factor. Since the final result of big\_sum is guaranteed to be less than or equal to (k - 1) \* 8, we can exhaustively list all the values for which the modulus is zero by:

Where m is the largest integer for which k \* m & lt; = (k - 1) \* 8.

Factors between 0x1 (decimal 1) and 0xF (decimal 15) are shown in a loop on the seven segment display with a one second delay between each factor. This design uses some combinatorial logic to convert from binary to hexadecimal for the seven segment display. The second delay is achieved by a clock divider logic.

The output pins show the prime factors of the input number. If the input is zero, the output is set to the bottom 8 bits of the counter for debugging purposes.

# How to test

After reset and input set to 0, the counter on the seven segment display should increase by one every second with a 10 MHz input clock from 0x1 to 0xF. The outputs are the lower bits of the internal counter that increases every cycle. The dot on the seven segment display should be off.

For inputs other than 0, the seven segment display shows the factors one by one, cycling back at the end. The factor 1 is displayed for all inputs and only factors up to 15 are shown. For example for 6, the factors 1, 2, 3 and 6 will be shown on the display. For 7, the factors 1 and 7 will be shown on the display. For 23, only the factor 1 will be show on the display. It will also use the output pins to indicate the prime factors, where the least significant bit represents 2 and the most significant bit represents 19. For example for 6, only 2 and 3 are set to 1. For 7, only 7 is set to 1. For 23, all the outputs are zero. The dot on the seven segment display is only on when the input number is prime.

Hexadecimals are displayed using the decimal configurations (without modifications). And then the hexadecimal values specified here.

Please reset the design before giving your input. Also, you can have a look at the testbench for more thorough testing.

| # | Input                          | Output          | Bidirectional   |

|---|--------------------------------|-----------------|-----------------|

| 0 | Fist bit of number to factor   | Segment a (hex) | Is 2 a factor?  |

| 1 | Second bit of number to factor | Segment b (hex) | ls 3 a factor?  |

| 2 | Third bit of number to factor  | Segment c (hex) | ls 5 a factor?  |

| 3 | Fourth bit of number to factor | Segment d (hex) | ls 7 a factor?  |

| 4 | Fifth bit of number to factor  | Segment e (hex) | ls 11 a factor? |

| 5 | Sixth bit of number to factor  | Segment f (hex) | ls 13 a factor? |

| # | Input                           | Output                 | Bidirectional   |

|---|---------------------------------|------------------------|-----------------|

| 6 | Seventh bit of number to factor | Segment g (hex)        | ls 17 a factor? |

| 7 | Eigth bit of number to factor   | Segment dot (is prime) | Is 19 a factor? |

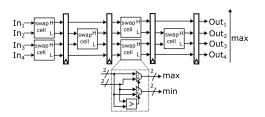

# Odd even sorter [5]

- Author: Vasileios Titopoulos

- Description: An odd even sorter of four 2-bit values

- GitHub repository

- HDL project

- Mux address: 5

- Extra docs

- Clock: 25 000 000 Hz

- External hardware:

#### How it works

The sorter takes the inputs from ui\_in[7:0] signals and rearranges them properly to uo\_out[7:0] signals after they pass from the four internal pipeline registers.

#### How to test

Connect a clock for the internal registers and use the inputs ui\_in[7:0] to assign the values to the design. The sorted values are provided through uo\_out[7:0] signals

| # | Input     | Output               | Bidirectional |

|---|-----------|----------------------|---------------|

| 0 | l0/ln1[0] | O0/Out1[0]/segment a | none          |

| 1 | 11/ln1[1] | O1/Out1[1]/segment b | none          |

| 2 | l2/ln2[0] | O2/Out2[0]/segment c | none          |

| 3 | l3/ln2[1] | O3/Out2[1]/segment d | none          |

| 4 | l4/ln3[0] | O4/Out3[0]/segment e | none          |

| 5 | l5/ln3[1] | O5/Out3[1]/segment f | none          |

| 6 | l6/In4[0] | O6/Out4[0]/segment g | none          |

| 7 | l7/ln4[1] | O7/Out4[1]/dot       | none          |

# The Bulls and Cows game [6]

- Author: Giorgos Dimitrakopoulos

- Description: An implementation of the Bulls and Cows game

- GitHub repository

- HDL project

- Mux address: 6

- Extra docs

- Clock: 25 000 000 Hz

- External hardware:

#### How it works

The bulls and cows is a game where the users try to discover the exact pattern of secret numbers

#### How to test

Firstly, a secret pattern of four 3-bit numbers, which are different with each other, should be set. This is done through the save signal. After the secret number is set, another user tries to find the correct pattern of numbers. In order for the correct pattern to be found, the signals of cows and bulls are pinpointing as to whether the user input had any match with the secret pattern. The cows indication shows as to whether the input matches with any secret number but it is not in the right position. On the other hand, the bulls indication shows as to whether the input matches of the game is for the user to achieve four bulls indications. For the signals of bulls and cows the indications are showed through the seven segment display. In the seven segment display the bulls indication is placed in the top region (0-1-5-6) and the cows indication is placed in the bottom region (2-3-4-7) of the seven segment display.

| # | Input                     | Output                | Bidirectional  |

|---|---------------------------|-----------------------|----------------|

| 0 | I0/Number1[0]             | O0/bulls[1]/segment a | I7/Number3[0]  |

| 1 | 11/Number1[1]             | O1/bulls[2]/segment b | 18/Number3[1]  |

| 2 | I2/Number1[2]             | O2/cows[0]/segment c  | 19/Number3[2]  |

| 3 | I3/Number2[0]             | O3/cows[1]/segment d  | I10/Number4[0] |

| 4 | I4/Number2[1]             | O4/cows[2]/segment e  | I11/Number4[1] |

| 5 | I5/Number2[2]             | O5/bulls[0]/segment f | I12/Number4[2] |

| 6 | I6/Save the secret number | O6/bulls[3]/segment g | none           |

| 7 | none                      | O7/cows[3]/dot        | none           |

# VGA Output for Arduino [16]

- Author: Devin Atkin

- Description: The final goal of this project is to create an arduino VGA driver. Currently it's nothing

- GitHub repository

- HDL project

- Mux address: 16

- Extra docs

- Clock: 25175000 Hz

- External hardware: You're going to need to hook up a VGA output to the chip alongside the clock, to control it you'll need some form of microcontroller

#### How it works

The name is overly ambitious but that's why I'll submit it to future submisisons as I add more features. :)

#### How to test

The design has been simulated and tested with the eric eastwood simulator using the output generated by tb.v. The output will be tested using a Basys 3 board prior to the final sumbission time permitting. The design is currently set up to output a 640x480 60Hz VGA signal. The output is currently set to a random test pattern. The design will have a way to adjust background colour, and draw onto the display using a few basic SPI commands. (Not yet implemented) I'm testing my output using a VGA simulator tool online https://madlittlemods.github.io/vga-simulator/ and will be testing on a Basys 3 board prior to submission.

| # | Input    | Output      | Bidirectional |

|---|----------|-------------|---------------|

| 0 | SPI MOSI | VGA HSync   | SPI MISO      |

| 1 | SPI CLK  | VGA VSync   | none          |

| 2 | SPI CS   | VGA Red 0   | none          |

| 3 | none     | VGA Red 1   | none          |

| 4 | btn_up   | VGA Green 0 | none          |

| 5 | btn_down | VGA Green 1 | none          |

| 6 | none     | VGA Blue 0  | none          |

| 7 | none     | VGA Blue 1  | none          |

|   |          |             |               |

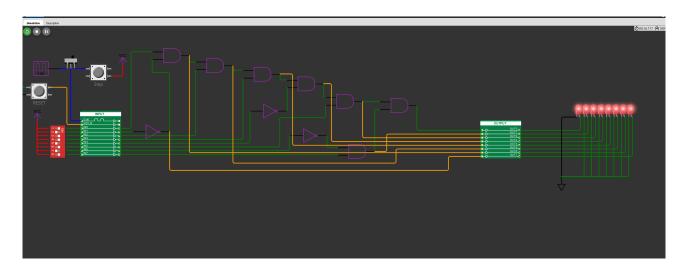

# Digital Cipher & Interlock System [17]

- Author: Eric German MKME Lab

- Description: Digital Cipher with 256 combinations & one solution which sets output to high

- GitHub repository

- Wokwi project

- Mux address: 17

- Extra docs

- Clock: 0 Hz

- External hardware: NA

# How it works

Can be used as a simple puzzle demo or as a safety chain/interlock on equipment. Being hardware interlocks without microcontroller logic it mimics a standalone safety relay function which is used to verify all subsystems are online before allowing machinery to run. The high or low input can be tied to the sensors and switches in the safety chain. Only when all are in the desired state will the output be OKAY/HIGH. NO and NC switches/sensors can be tied to the appropriate pins. Feedback signals are provided from gate outputs by FB1 through FB7

### How to test

Provide below inputs on the required pins to activate output

| # | Input | Output                  | Bidirectional |

|---|-------|-------------------------|---------------|

| 0 | HIGH  | HIGH All Chain Unlocked | none          |

| 1 | LOW   | FB1 Feedback signal     | none          |

| 2 | HIGH  | FB2 Feedback signal     | none          |

| 3 | HIGH  | FB3 Feedback signal     | none          |

| 4 | LOW   | FB4 Feedback signal     | none          |

| 5 | HIGH  | FB5 Feedback signal     | none          |

| 6 | LOW   | FB6 Feedback signal     | none          |

| 7 | HIGH  | FB7 Feedback signal     | none          |

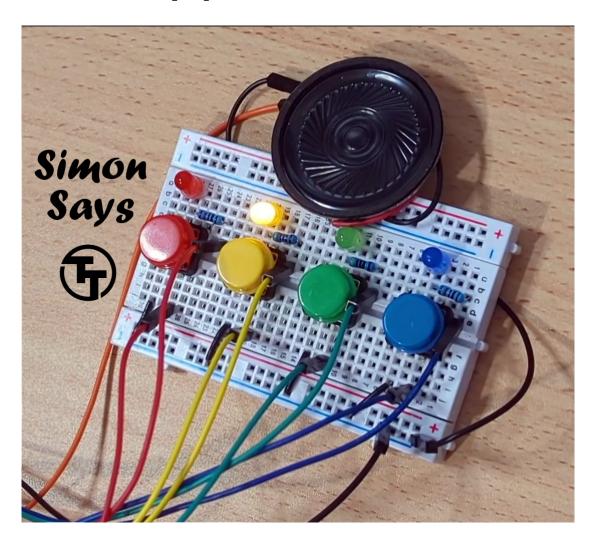

# Simon Says game [18]

- Author: Uri Shaked

- Description: A simple memory game

- GitHub repository

- HDL project

- Mux address: 18

- Extra docs

- Clock: 50000 Hz

- External hardware: Four push buttons (with pull-down resistors), four LEDs, and optionally a speaker/buzzer and two digit 7-segment display

### How it works

Simon says is a simple electronic memory game: the user has to repeat a growing sequence of colors. The sequence is displayed by lighting up the LEDs. Each color also has a corresponding tone.

In each turn, the game will play the sequence, and then wait for the user to repeat the sequence by pressing the buttons according to the color sequence. If the user repeated the sequence correctly, the game will play a "leveling-up" sound, add a new color at the end of the sequence, and move to the next turn.

The game continues until the user has made a mistake. Then a game over sound is played, and the game restarts.

Check out the online simulation at https://wokwi.com/projects/371755521090136065 (including wiring diagram).

# How to test

You need four buttons, four LEDs, resistors, and optionally a speaker/buzzer and a two digit 7-segment display for the score.

Ideally, you want to use 4 different colors for the buttons/LEDs (red, green, blue, yellow).

- 1. Connect the buttons to pins btn1, btn2, btn3, and btn4, and also connect each button to a pull down resistor.

- 2. Connect the LEDs to pins led1, led2, led3, and led4, matching the colors of the buttons (so led1 and btn1 have the same color, etc.)

- 3. Connect the speaker to the speaker pin.

- 4. Connect the seven segment display as follows: seg\_a through sev\_g to individual segments, dig1 to the common pin of the tens digit, dig2 to the common pin of the ones digit. Set seginv according to the type of 7 segment display you have: high for common anode, low for common cathode.

- 5. Reset the game, and then press any button to start it. Enjoy!

Note: the game requires 50KHz clock input.

| # | Input  | Output  | Bidirectional |

|---|--------|---------|---------------|

| 0 | btn1   | led1    | seg_a         |

| 1 | btn2   | led2    | seg_b         |

| 2 | btn3   | led3    | seg_c         |

| 3 | btn4   | led4    | seg_d         |

| 4 | seginv | speaker | seg_e         |

| 5 | none   | dig1    | seg_f         |

| 6 | none   | dig2    | seg_g         |

|   |        |         |               |

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 7 | none  | none   | none          |

# YKM 7-seg driver [19]

- Author: Yeo Kheng Meng

- Description: Shows the string ykM\_1St\_CHIP character by character

- GitHub repository

- Wokwi project

- Mux address: 19

- Extra docs

- Clock: 0.5 Hz

- External hardware: 7-segment LCD

#### How it works

The string is shown by individual characters to the 7-segment LCD. By default with all pins except Clock being Low, the chip will cycle through all the characters depending on clock speed. To display individual characters manually, set HIGH to counter pin and BCD. Then select the bits 0-3 manually.

#### How to test

See how\_it\_works.

| # | Input                                                    | Output      | Bidirectional |

|---|----------------------------------------------------------|-------------|---------------|

| 0 | clock                                                    | 7-segment a | none          |

| 1 | none                                                     | 7-segment b | none          |

| 2 | none                                                     | 7-segment c | none          |

| 3 | none                                                     | 7-segment d | none          |

| 4 | Disable counter. This is active-high.                    | 7-segment e | none          |

| 5 | Driven by BCD or counter. High for BCD, Low for counter. | 7-segment f | none          |

| 6 | BCD bit 3                                                | 7-segment g | none          |

| 7 | BCD bit 2                                                | none        | none          |

# Configurable PID Block [20]

- Author: Maxim Vasic

- Description: It was meant to be a final project, but that was undercut.

- GitHub repository

- HDL project

- Mux address: 20

- Extra docs

- Clock: 0 Hz

- External hardware:

#### How it works

It's a PID block to be configured with I2C. GPIOs 7 through 2 are for error/control, and GPIOs 1 and 0 are SDA and SCL.

#### How to test

Configure with the I2C frame, see the I2C files for the "addresses". See the I2C test file for an example.

| # | Input | Output    | Bidirectional |

|---|-------|-----------|---------------|

| 0 | none  | segment a | Error/Control |

| 1 | none  | segment b | Error/Control |

| 2 | none  | segment c | Error/Control |

| 3 | none  | segment d | Error/Control |

| 4 | none  | segment e | Error/Control |

| 5 | none  | segment f | Error/Control |

| 6 | none  | segment g | SDA           |

| 7 | none  | dot       | SCL           |

# PWM audio [21]

- Author: Yeo Kheng Meng

- Description: Takes in 8-bit audio over a parallel (port) interface then generates an analog audio signal like a Covox Speech Thing.

- GitHub repository

- HDL project

- Mux address: 21

- Extra docs

- Clock: 10000000 Hz

- External hardware: A 0.1uF capacitor to ground is recommended on the 2 audio output pins

### How it works

This is meant as a parallel port sound card like a Covox Speech Thing. Instead of R-2R resistors, the chip will generate the analog audio output using PWM and First-order sigma-delta modulator.

#### How to test

No particular test required.

| # | Input                           | Output                          | Bidirectional       |

|---|---------------------------------|---------------------------------|---------------------|

| 0 | Bit 0 of Parallel port<br>(LSB) | Standard PWM<br>audio output    | Direct from input 0 |

| 1 | Bit 1 of Parallel port          | Sigma-delta<br>modulator output | Direct from input 1 |

| 2 | Bit 2 of Parallel port          | From ena pin                    | Direct from input 2 |

| 3 | Bit 3 of Parallel port          | From clk pin                    | Direct from input 3 |

| 4 | Bit 4 of Parallel port          | From rst_n pin                  | Direct from input 4 |

| 5 | Bit 5 of Parallel port          | Static 1                        | Direct from input 5 |

| 6 | Bit 6 of Parallel port          | Static 0                        | Direct from input 6 |

| 7 | Bit 7 of Parallel port<br>(MSB) | Static 1                        | Direct from input 7 |

# 4-bit ALU [22]

- Author: David Bertuch

- Description:

- GitHub repository

- HDL project

- Mux address: 22

- Extra docs

- Clock: 10000000 Hz

- External hardware:

### How it works

Uses a set of registers to divide the clock, and then some combinational logic to convert from binary to decimal for the display.

Puts the bottom 8 bits of the counter on the bidirectional outputs.

With all the inputs set to 0, the internal 24 bit compare is set to 10,000,000. This means the counter will increment by one each second.

If any inputs are non zero, then the input will be used as an bits 11 to 18 of the 24 bit compare register. Example: setting the inputs to 00010000 will program 16384 into the compare register. With a 10MHz clock the counter will increment  $\sim$ 610 times per second.

### How to test

After reset, the counter should increase by one every second with a 10MHz input clock. Experiment by changing the inputs to change the counting speed.

| # | Input          | Output    | Bidirectional          |

|---|----------------|-----------|------------------------|

| 0 | compare bit 11 | segment a | second counter bit 0   |

| 1 | compare bit 12 | segment b | second counter bit $1$ |

| 2 | compare bit 13 | segment c | second counter bit 2   |

| 3 | compare bit 14 | segment d | second counter bit 3   |

| 4 | compare bit 15 | segment e | second counter bit 4   |

| 5 | compare bit 16 | segment f | second counter bit 5   |

| # | Input          | Output    | Bidirectional        |

|---|----------------|-----------|----------------------|

| 6 | compare bit 17 | segment g | second counter bit 6 |

| 7 | compare bit 18 | dot       | second counter bit 7 |

# RGB Mixer [23]

- Author: Matt Venn

- Description: Use 3 rotary encoder to control 3 PWM generators

- GitHub repository

- HDL project

- Mux address: 23

- Extra docs

- Clock: 1000000 Hz

- External hardware:

### How it works

3 PWM generators are fed by 3 debounced encoder peripherals.

### How to test

Connect 3 digital rotary encoders to the first 6 inputs. Changing the encoders will change the PWM outputs on the first 3 outputs.

| # | Input           | Output | Bidirectional |

|---|-----------------|--------|---------------|

| 0 | encoder 0 pin a | pwm 0  | n/a           |

| 1 | encoder 0 pin b | pwm 1  | n/a           |

| 2 | encoder 1 pin a | pwm 2  | n/a           |

| 3 | encoder 1 pin b | n/a    | n/a           |

| 4 | encoder 2 pin a | n/a    | n/a           |

| 5 | encoder 2 pin b | n/a    | n/a           |

| 6 | n/a             | n/a    | n/a           |

| 7 | n/a             | n/a    | n/a           |

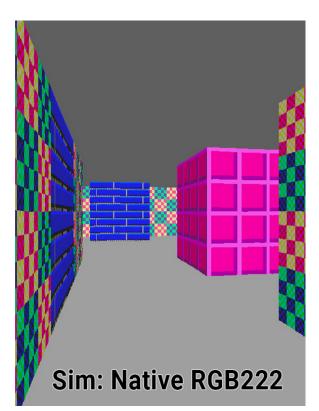

# raybox-zero [33]

- Author: algofoogle (Anton Maurovic)

- Description: Simple VGA ray caster game demo

- GitHub repository

- HDL project

- Mux address: 33

- Extra docs

- Clock: 25000000 Hz

- External hardware: VGA connector with RGB222 DAC

# How it works

NOTE: Expect updates after the TT04 datasheet is made. Check tt04-raybox-zero's README (https://github.com/algofoogle/tt04-raybox-zero) for latest info.

This framebuffer-less VGA display generator is 'racing the beam' to yield a simple realtime "3D"-like render of a game map using ray casting. It's inspired by Wolf3D and based on Lode's Raycasting tutorial (https://lodev.org/cgtutor/raycasting.html). Think of it as a primitive 'GPU' using a grid map of wall blocks, with basic texture mapping and flat-coloured floor/ceiling. No doors or sprites – but maybe in TT05? In TT04's 130nm process we use 4x2 tiles (~0.16mm<sup>2</sup>) at ~48% density.

Without a framebuffer, rendering/animation occurs at full speed. Registers store the 'POV' (Point of View) to render. It's expected that a host controller implements game/motion logic and calculates the POV, then sending it to the chip via SPI ( $ss_n/sclk/mosi$ ). An MCU or low-spec CPU should do. I've been bit-banging SPI with a Raspberry Pi Pico.

At reset the POV registers are set to an angled view of the inbuilt 16x16 grid map.

NOTE: "FPS games" like Wolf3D use a landscape display, i.e. normal desktop monitor orientation. I designed this as a portrait display (rotated 90° clockwise) for silicon area optimisations that come with rendering by scanline instead of by column. If you don't want a sideways monitor, design a game/demo using this different perspective. For example, image Mario's 1st-person view of his 2D platform world...

### Features

- 640x480 VGA display at ~60Hz from 25MHz clock (25.175MHz ideal)

- Registered and unregistered digital VGA outputs: RGB222 and H/VSYNC

- Portrait "FPS" orientation

- Hard-coded 16x16 map with 3 textures: light- and dark-side variations

- SPI interface to set POV with debug option to see POV register bits

- 'SPI2' interface to set ceiling colour, floor colour, or floor 'leak'

- Reset loads an interesting POV. Optional 'demo mode' inputs can vary it.

- HBLANK and VBLANK outputs as optional interrupt requests

A warning about turning your screen on its side

As stated, this is designed to drive a display with a *portrait* orientation when used as a "first person shooter" but BEWARE: The backlights failed on *two* old flat panel VGA displays (from circa 2003) not long after I turned them on their sides. Coincidence? Age? A CCFL failure mode? Not sure. I'm using a monitor from 2008 now.

# How to test

Attach a VGA connector's HSYNC and VSYNC to the chip's respective outs with (say) inline 100R resistors for protection. Connect at least red[1], green[1], blue[1] with inline 270R resistors, or better yet use an R2R DAC on each colour output *pair*. Make sure VGA GND is connected, of course.

Pull up reg to select 'registered outputs'. Without this, you will get the unregistered versions, which might be murky or have some timing issues – I included this option for testing purposes. In the actual ASIC version of this, I expect the registered outputs will be much cleaner, but we'll see.

Supply a 25MHz clock (or ideally 25.175MHz), and assert the reset signal, and you should get a clockwise-90°-rotated display of textured walls with dark grey ceiling (right-hand side) and light grey floor (left-hand side).

Pull up the debug input and you should see little squares show up in the corner of the screen that represent the current state of the POV registers.

Pull up either/both of inc\_px/py and the view should drift along slowly. This is 'demo mode'. Don't be alarmed when it goes through walls, or for periods when you see half the screen is just grey and the other half is flickering different colours – this just means you're moving *through* a wall block.

Changing POV: https://github.com/algofoogle/tt04-raybox-zero#write-pov-via-spi

| # | Input        | Output   | Bidirectional     |

|---|--------------|----------|-------------------|

| 0 | SPI in: sclk | hsync_n  | Out: o_hblank     |

| 1 | SPI in: mosi | vsync_n  | Out: o_vblank     |

| 2 | SPI in: ss_n | red[0]   | SPI2 in: reg_sclk |

| 3 | debug        | red[1]   | SPI2 in: reg_mosi |

| 4 | inc_px       | green[0] | SPI2 in: reg_ss_n |

| 5 | inc_py       | green[1] | none              |

| 6 | reg          | blue[0]  | none              |

| 7 | none         | blue[1]  | none              |

|   |              |          |                   |

# ChipTune [37]

- Author: Wallace Everest

- Description: Vintage 8-bit sound generator

- GitHub repository

- HDL project

- Mux address: 37

- Extra docs

- Clock: 1789773 Hz

- External hardware: Computer COM port

#### How it works

ChipTune implements an 8-bit Programmable Sound Generator (PSG). Input is from a serial UART interface. Output is PWM audio.

**Overview** This project replicates the Audio Processing Unit (APU) of vintage video games.

## Statistics

- Tiles: 2x2

- DFF: 417

- Total Cells: 2549

- Utilization: 32%

TinyTapeout 4 Configuration

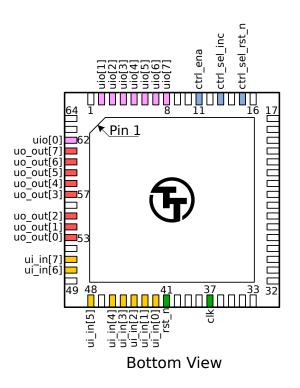

TT04 devices from the eFabless Multi-Project Wafer (MPW) shuttle are delivered in QFN-64 packages, mounted on a daughterboard for breakout.

Based on data from:

- https://github.com/efabless/caravel\_board/blob/main/hardware/breakout/caravel-M.2-card-QFN/caravel-M.2-card-QFN.pdf

- https://github.com/TinyTapeout/tt-multiplexer/blob/main/docs/INFO.md

- https://open-source-silicon.slack.com/archives/C016N88BX44/p1688915892223379

MPRJ\_IO Pin Assignments

| Signal      | Name      | Dir | QFN | PCB |

|-------------|-----------|-----|-----|-----|

|             | jtag      | in  | 31  |     |

| mprj_io[1]  | sdo       | out | 32  |     |

| mprj_io[2]  | sdi       | in  | 33  |     |

| mprj_io[3]  | csb       | in  | 34  |     |

| mprj_io[4]  | sck       | in  | 35  |     |

| mprj_io[5]  | user_clk  | out | 36  |     |

| mprj_io[6]  | clk       | in  | 37  |     |

| mprj_io[7]  | rst_n     | in  | 41  |     |

| mprj_io[8]  | ui_in[0]  | in  | 42  |     |

| mprj_io[9]  | ui_in[1]  | in  | 43  |     |

| mprj_io[10] | ui_in[2]  | in  | 44  |     |

| mprj_io[11] | ui_in[3]  | in  | 45  |     |

| mprj_io[12] | ui_in[4]  | in  | 46  |     |

| mprj_io[13] | ui_in[5]  | in  | 48  |     |

| mprj_io[14] | ui_in[6]  | in  | 50  |     |

| mprj_io[15] | ui_in[7]  | in  | 51  |     |

| mprj_io[16] | uo_out[0] | out | 53  |     |

| mprj_io[17] | uo_out[1] | out | 54  |     |

| mprj_io[18] | uo_out[2] | out | 55  |     |

| mprj_io[19] | uo_out[3] | out | 57  |     |

| mprj_io[20] | uo_out[4] | out | 58  |     |

| mprj_io[21] | uo_out[5] | out | 59  |     |

|             |           |     |     |     |

| Signal      | Name      | Dir | QFN | PCB |

|-------------|-----------|-----|-----|-----|

| mprj_io[22] | uo_out[6] | out | 60  |     |

| mprj_io[23] | uo_out[7] | out | 61  |     |

| mprj_io[24] | uio[0]    | bid | 62  |     |

| mprj_io[25] | uio[1]    | bid | 2   |     |

| mprj_io[26] | uio[2]    | bid | 3   |     |

| mprj_io[27] | uio[3]    | bid | 4   |     |

| mprj_io[28] | uio[4]    | bid | 5   |     |

| mprj_io[29] | uio[5]    | bid | 6   |     |

| mprj_io[30] | uio[6]    | bid | 7   |     |

| mprj_io[31] | uio[7]    | bid | 8   |     |

| mprj_io[32] | sel_ena   | in  | 11  |     |

| mprj_io[33] | spare     |     | 12  |     |

| mprj_io[34] | sel_inc   | in  | 13  |     |

| mprj_io[35] | spare     |     | 14  |     |

| mprj_io[36] | sel_rst_n | in  | 15  |     |

| mprj_io[37] | spare     |     | 16  |     |

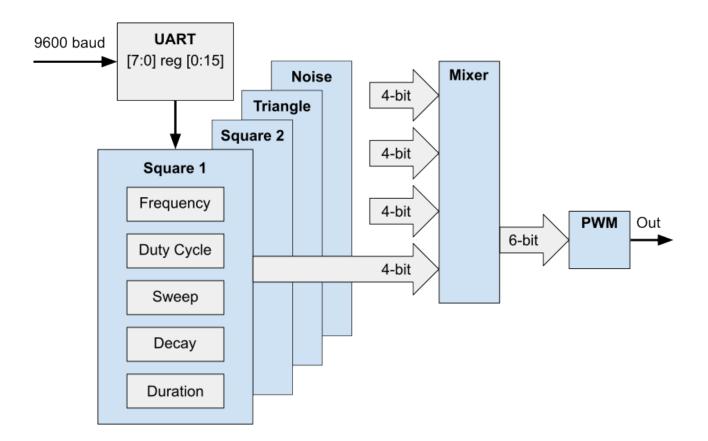

## APU Operation

The audio portion of the project consists of two rectangular pulse generators, a triangle wave generator, and a noise generator. Each module is controlled by four 8-bit registers. Configurable parameters are the frequency, duty cycle, sweep, decay, and note duration.

An explanation of register functions can be found on the NESDEV website. Only the lower 4-bits of the address are decoded.

https://www.nesdev.org/wiki/APU

## UART Operation

- A register address and data are recovered from two consecutive serial bytes.

- A byte with the msb=0 is considered the first byte with 7-bits of data.

- A byte with msb=1 is considered the second byte with the remaining 1-bit of data and a 6-bit address.

- A ready flag is generated after receiving the second byte.

| Byte 3 | 1  |    |    |    |    |    |    |   |      | Byte 2 | 2  |    |    |    |    |    |    |   |      |

|--------|----|----|----|----|----|----|----|---|------|--------|----|----|----|----|----|----|----|---|------|

| Start  | DO | D1 | D2 | DЗ | D4 | D5 | D6 | 0 | Stop | Start  | D7 | AO | A1 | A2 | AЗ | A4 | Α5 | 1 | Stop |

#### Pin Assignments

| Signal      | Name   | Signal       | Name     |

|-------------|--------|--------------|----------|

| clk         | 12 MHz | ena          | spare    |

| rst_n       | spare  | uio_oe[7:0]  | spare    |

| ui_in[0]    | spare  | uo_out[0]    | blink    |

| ui_in[1]    | spare  | uo_out[1]    | link     |

| ui_in[2]    | rx     | uo_out[2]    | tx       |

| ui_in[3]    | spare  | uo_out[3]    | pwm      |

| ui_in[4]    | spare  | uo_out[4]    | square1  |

| ui_in[5]    | spare  | uo_out[5]    | square2  |

| ui_in[6]    | spare  | uo_out[6]    | triangle |

| ui_in[7]    | spare  | uo_out[7]    | noise    |

| uio_in[7:0] | spare  | uio_out[7:0] | spare    |

- CLK is a 1.789733 MHz clock

- BLINK is an LED status indicator with a 1 Hz rate

- LINK is an LED activity indicator of the RX signal

- PWM is the pulse-width modulated audio output

- RX is a UART input (9600,8,N,1)

- TX generates a frame synchonization character (0x80)

#### How to test

The ChipTune project can be interfaced to a computer COM port (9600,n,8,1). An analog PWM filter and audio driver are needed for the test rig.

The following serial strings will activate example functions:

```

# Square 1

08 82 30 80 00 84 00 86 #Clear

27 83 02 81 7E 85 08 86 #PlaySmallJump

27 83 02 81 7C 84 09 86 #PlayBigJump

13 83 1E 81 3A 84 0A 86 #PlayBump

19 83 1E 81 0A 84 08 86 #PlayFireballThrow

4B 83 1F 81 6F 85 08 86 #PlaySmackEnemy

1C 83 1E 81 7E 85 08 86 #PlaySwimStomp

08 82 3F 81 17 84 01 86 #400Hz

# Square 2

30 88 08 8A 00 8C 00 8E #Clear

18 89 7F 8A 71 8C 08 8E #PlayTimerTick

```

OD 89 7F 8A 71 8C 08 8E #PlayCoinGrab 1F 89 14 8B 79 8D 0A 8E #PlayBlast 7F 88 5D 8A 71 8C 08 8E #PlayPowerUpGrab 3F 89 08 8A 17 8C 01 8E #400Hz # Triangle 00 91 00 92 00 94 00 96 #Clear 00 92 0B 95 00 96 40 91 #400Hz # Noise 30 98 00 9A 00 9C 00 9E #Clear 00 9A 00 9E 05 9D 3F 98 #300Hz

| # | Input | Output   | Bidirectional |

|---|-------|----------|---------------|

| 0 | None  | Blink    | None          |

| 1 | None  | Link     | None          |

| 2 | RX    | ТΧ       | None          |

| 3 | None  | PWM      | None          |

| 4 | None  | Square1  | None          |

| 5 | None  | Square2  | None          |

| 6 | None  | Triangle | None          |

| 7 | None  | Noise    | None          |

## **OpenSource PWM Peripheral [48]**

- Author: Medinceanu Paul-Catalin

- Description: The purpose of this project is to develop an Opensource PWM Peripheral with advanced functions and configurations. These capabilities are needed mostly in Power Electronics, where fine tuning of the control signals is crucial. The two standout functions that I have implemented are the deadband and the synchronization between counters.

- GitHub repository

- HDL project

- Mux address: 48

- Extra docs

- Clock: 10000000 Hz

- External hardware:

#### How it works

The peripheral contains 3 counters, each of them with 2 comparators and 2 deadband generators. The counter is set to go to a value, the comparator is wired to the registers of the counter and decides when to set or clear the squarewave signal. By setting the counter to switch at different values, any duty cycle can be achieved. The project can be configured to generate specific PWM signals by writing the desired configuration at the right address in the register file. The register map can be found in the 'doc' folder of the repo.

#### How to test

To test the project, it should be tied through the input and bidirectional pins to a microcontroller. A C code(for a specific microcontroller) will be available on the repo to configure the peripheral through the serial terminal. After the setup is done, the PWM signals will be visible at the output pins. An alternative way to configure the peripheral is through the onboard switches. The write enable is held high, the address is set next on the input pins and finally the data is set at the bidirectional pins. The process is repeated for each register of the PWM module in use.

| # | Input        | Output | Bidirectional |

|---|--------------|--------|---------------|

| 0 | i_address[5] | unused | io_data[7]    |

| # | Input        | Output  | Bidirectional |

|---|--------------|---------|---------------|

| 1 | i_address[4] | unused  | io_data[6]    |

| 2 | i_address[3] | o_pwm1A | io_data[5]    |

| 3 | i_address[2] | o_pwm1B | io_data[4]    |

| 4 | i_address[1] | o_pwm2A | io_data[3]    |

| 5 | i_address[0] | o_pwm2B | io_data[2]    |

| 6 | unused       | o_pwm3A | io_data[1]    |

| 7 | i_write_en   | o_pwm3B | io_data[0]    |

**Experiment Number Six: Laplace LUT [50]**

20.  $1/(s^2(s^2+w^2)), (1/w^3)(wt-\sin wt)$ 21.  $1/((s^2+w^2)^2), (1/2w^3)(\sin wt - wt \cos wt)$ 22.  $s/(s^2+w^2)^2, (1/2w)\sin wt$ 23.  $s^{2}/((s^{2}+w^{2})^{2}), (1/2w)(\sin wt + wt \cos wt)$ 24.  $s/((s^2 + a^2)(s^2 + b^2)), (1/(b^2 - a^2))(\cos at - \cos bt)$ 25.  $1/(s^4 + 4k^4), (1/4k^3)(\sin kt \cos kt - \cos kt \sinh kt)$ 26.  $s/(s^4+4k^4), (1/2k^2)\sin kt\sinh kt$ 27.  $1/(s^4 - k^4), (1/2k^3)(\sinh kt - \sin kt)$

- Author: Paul Hansel

- Description: ASCII ROM encoding the LaTeX characters needed to typeset the Laplace transforms of a few specialized functions.

- GitHub repository

- HDL project

- Mux address: 50

- Extra docs

- Clock: 1 Hz

- External hardware:

#### How it works

This project provides an ASCII encoding of the LaTeX code to typeset a few dozen Laplace transforms of common functions. When the user sets the lower ui\_in pins to a number, asserts reset and then asserts ui\_in 6 high, the project will begin clocking out the transform char-by-char, with uio\_out showing  $F(s) = L{f(t)}$  and uo\_out

showing f(t) itself. If either one is shorter than the other for a particular transform, empty space characters are appended. It uses two different address spaces to do this: mem\_addr, which maps each pair of concatenated ASCII characters (function, transformed function) from all transforms back-to-back as 16-bit values to a linear 10-bit address space, and pointer\_addr, which maps the concatenated start address and length of each row (within mem\_addr space) as 20-bit values to that row's line number in an 8-bit address space (with only 6 bits used). The read-only Verilog containing the actual ASCII data is generated by a python script that reads the LaTeX source directly. Verification is achieved in the same way.

#### How to test

Program a number onto ui\_in[5:0] between 0 and 43. Toggle reset\_n (high/low/high), then toggle ui\_in[6] high to start printing. Watch uo\_out and uio\_out for the resulting ASCII characters. The input address bus accepts a number (0-45) corresponding to an arbitrary Laplace tranform encoding; it must be set before asserting start. The active-high character output enable signal must be high to start or continue character output. The clock divider disable input must be high to run at full speed or low to run at 1 character per  $5 \times 10^7$  clocks.

| # | Input                   | Output    | Bidirectional |

|---|-------------------------|-----------|---------------|

| 0 | Address bit 0           | RHS_BIT_0 | LHS_BIT_0     |

| 1 | Address bit 1           | RHS_BIT_1 | LHS_BIT_1     |

| 2 | Address bit 2           | RHS_BIT_2 | LHS_BIT_2     |

| 3 | Address bit 3           | RHS_BIT_3 | LHS_BIT_3     |

| 4 | Address bit 4           | RHS_BIT_4 | LHS_BIT_4     |

| 5 | Address bit 5           | RHS_BIT_5 | LHS_BIT_5     |

| 6 | Character output enable | RHS_BIT_6 | LHS_BIT_6     |

| 7 | Clock divider disable   | RHS_BIT_7 | LHS_BIT_7     |

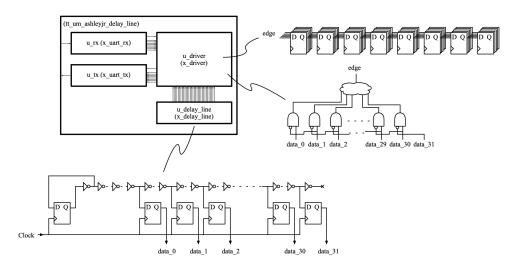

## Karplus-Strong String Synthesis [52]

- Author: Chinmay Patil

- Description: Plucked string sound synthesizer

- GitHub repository

- HDL project

- Mux address: 52

- Extra docs

- Clock: 256000 Hz

- External hardware:

## How it works

This is simplified implementation of Karplus-Strong (KS) string synthesis based on papers, Digital Synthesis of Plucked-String and Drum Timbres and Extensions of the Karplus-Strong Plucked-String Algorithm.

A register map controls and configures the KS synthesis module. This register map is accessed through a SPI interface. Synthesized sound samples can be accessed through the I2S transmitter interface.

SPI Frame

SPI Mode: CPOL = 0, CPHA = 1

The 16-bit SPI frame is defined as,

$\textRead/\overline\textMathaddress[6:0] \textData[7:0]$

## Register Map

The Register Map has 16 Registers of 8-bits each. It is divided into configuration and status registers,

Complete register map is described in the repository at https://github.com/pyamnih c/tt04-um-ks-pyamnihc.

## I2S Transmitter

The 8-bit signed sound samples can be read out at  $f_sck = 256$  kHz through this interface.

#### How to test

Connect a clock with frequency  $f_clk = 256$  kHz and apply a reset cycle to initialize the design, this sets the audio sample rate at fs = 16 kHz. Use the spi register map or the ui\_in to further configure the design. The synthesized samples are sent continuously on the I2S transmitter interface.

| # | Input                         | Output    | Bidirectional |

|---|-------------------------------|-----------|---------------|

| 0 | ~rst_n_prbs_15, ~rst_n_prbs_7 | segment a | sck_i         |

| 1 | load_prbs_15, load_prbs_7     | segment b | sdi_i         |

| 2 | freeze_prbs_15                | segment c | sdo_o         |

| 3 | freeze_prbs_7                 | segment d | cs_ni         |

| 4 | i2s_noise_sel                 | segment e | i2s_sck_o     |

| 5 | ~rst_n_ks_string              | segment f | i2s_ws_o      |

| 6 | pluck                         | segment g | i2s_sd_o      |

| 7 | NOT CONNECTED                 | dot       | prbs_15       |

# USB Device [54]

- Author: Darryl Miles

- Description: USB FullSpeed/LowSpeed device (proof-of-concept)

- GitHub repository

- HDL project

- Mux address: 54

- Extra docs

- Clock: 48000000 Hz

- External hardware: USB Connector, 2 x 68 ohm resistors, 1k5 ohm resistor

## How it works

This text will be updated nearer the scheduled TT04 redistribution time (early 2024) along with the project github README.md and gh-pages documentation. Please regenerate your documentation.

This is a hardware implementation of a USB device end hardware interface, should be compliant with USB1.1 FS/LS (not HS).

It is designed to be driven and commanded by a CPU over a native bus (such as WishBone). Due to the limited IO ports with TinyTapeout there is a TT2WB WishBone driver that provides the ability to perform WishBone 32bit data-path transactions inside the module over the narrower TT IO ports. The hardware design is capable of being any kind of USB device, this includes (and it not limited to) CDC, HID, audio, storage as the CPU sets the identity of the device in software to the host.

While I intend to drive the TT IC with an FPGA development board myself, it should be possible for the RP2040 providing a 48MHz clock to this project to achieve some kind of hello world over USB. The controller clock uses the global CLK pin (this is expected to be 48MHz but may well work at a range of other clock rates), the PHY interface uses BIDI port 3 (this must be 48MHz to provide timing in both full-speed and low-speed modes).

You can fire WishBone commands at the TT2WB interface, this maps to most of the ports IN/OUT/BIDI. This is currently abstracted away (via API) for testbench purposes and it is intended this also be the case for the FPGA/RP2040 programming interfaces. At this time the best documentation around this is to look at the TT2WB.py and tt04\_to\_wishbone.v in the project.

The configuration options were reduced to squeeze something to demonstrate a working endpoint into a 2x2 tile space, this is possible because SpinalHDL is good a generating hardware designs based on complex parametrization that allow features to be turned

on-off easily. The limited 2x2 tile space (ideally it wanted 2x4) has resulted in some limitations:

- the total number of endpoints is reduced from the full 16 down to 4 (numbered 0 to 3)

- the total buffer space available is reduced to just 52 bytes (this may be only enough space for a single active endpoint to operate, a standard serial CDC ideally need 3 endpoints working). The buffer space is provided by DFF registers and has a particular layout for control information and headers, this results in a total of 52 bytes only allowing a single endpoint to operate with a MaxPack-etLen=8. If a 2x3 tile were possible 96-108 bytes of buffer would be possible which would allow 3 endpoints to operate all at MPL=8 or a single endpoint at upto MPL=64 or some combination in between.

It is necessary to create a suitable USB cable to connect to the BIDI port0 and port1, this is expected to be the same cable and pinout scheme as the tt04-usbcbc project that is also present in TT04. This recommends a 68ohm series resistor for each of the Data+ and Data- lines, along with a pull-up resistor 1k5. The single pull-up resistor needs to be positioned appropriately for full-speed (on Data+) and low-speed (on Data-) modes.

## How to test

This text will be updated nearer the scheduled TT04 redistribution time (early 2024) along with the project github README.md and gh-pages documentation. Please regenerate your documentation.

The original bus interface documentation can be found at https://spinalhdl.github.io/SpinalDoc-RTD/master/SpinalHDL/Libraries/Com/usb\_device.html

The original source can be found at https://github.com/SpinalHDL/SpinalHDL/tree/dev/lib/src/

This hardware was originally designed for FPGA so some modifications were made in the areas of:

- Improving USB specification (a couple of potential bugs/out-of-spec items)

- Use of combinational logic versions of CRC5/CRC16 function blocks.

- Fixing features that seemed 95 percent written and present in the code but obviously not working or tested (support dual full-speed and low-speed in same hardware stack)

- Running on ASIC (clocks/resets)

- Optimizing for ASIC (UsbTimer counter widths, DFF buffer reduction squeeze, endpoint reduction squeeze)

- Encapsulating WishBone bus inside a TinyTapeout User project.

More items I've already forgotten on the way (but can document from code walk later)

The cocotb tests cover a significant number of the features and provide VCD output demonstrating almost everything possible with this hardware.

The Verilator/coverage showed the 2 main areas I do not exercise host suspend/resume and device resumelt support. Plus a number of error scenarios and a few non-critial minor features of the hardware.

I hope by early 2024 to have available some FPGA and some RP2040 application code to assist demonstration.

| # | Input            | Output            | Bidirectional                       |

|---|------------------|-------------------|-------------------------------------|

| 0 | tt2wb input bit0 | tt2wb output bit0 | USB D+ (bidi)                       |

| 1 | tt2wb input bit1 | tt2wb output bit1 | USB D- (bidi)                       |

| 2 | tt2wb input bit2 | tt2wb output bit2 | Interrupt (output only)             |

| 3 | tt2wb input bit3 | tt2wb output bit3 | Phy Clock 48MHz (input only)        |

| 4 | tt2wb input bit4 | tt2wb output bit4 | tt2wb control ACK (output only)     |

| 5 | tt2wb input bit5 | tt2wb output bit5 | tt2wb control CMD bit0 (input only) |

| 6 | tt2wb input bit6 | tt2wb output bit6 | tt2wb control CMD bit1 (input only) |

| 7 | tt2wb input bit7 | tt2wb output bit7 | tt2wb control CMD bit2 (input only) |

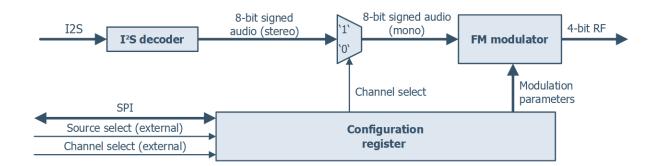

## Audio-PWM-Synth [64]

- Author: Thorsten Knoll

- Description: Generate Audio with a PWM output.

- GitHub repository

- HDL project

- Mux address: 64

- Extra docs

- Clock: 12MHz Hz

- External hardware:

### How it works

Explain how your project works

#### How to test

Explain how to test your project

| # | Input | Output         | Bidirectional |

|---|-------|----------------|---------------|

| 0 | none  | pwm_audio_low  | none          |

| 1 | none  | pwm_audio_high | none          |

| 2 | none  | none           | none          |

| 3 | none  | none           | none          |

| 4 | none  | none           | none          |

| 5 | none  | none           | none          |

| 6 | none  | none           | none          |

| 7 | none  | none           | none          |

## German Traffic Light [71]

- Author: Paul Knoll

- Description: Simulation of a german traffic light

- GitHub repository

- Wokwi project

- Mux address: 71

- Extra docs

- Clock: 0 Hz

- External hardware:

## How it works

Explain how your project works

#### How to test

Explain how to test your project

| # | Input | Output     | Bidirectional |

|---|-------|------------|---------------|

| 0 | none  | red LED    | none          |

| 1 | none  | yellow LED | none          |

| 2 | none  | green LED  | none          |

| 3 | none  | none       | none          |

| 4 | none  | none       | none          |

| 5 | none  | none       | none          |

| 6 | none  | none       | none          |

| 7 | none  | none       | none          |

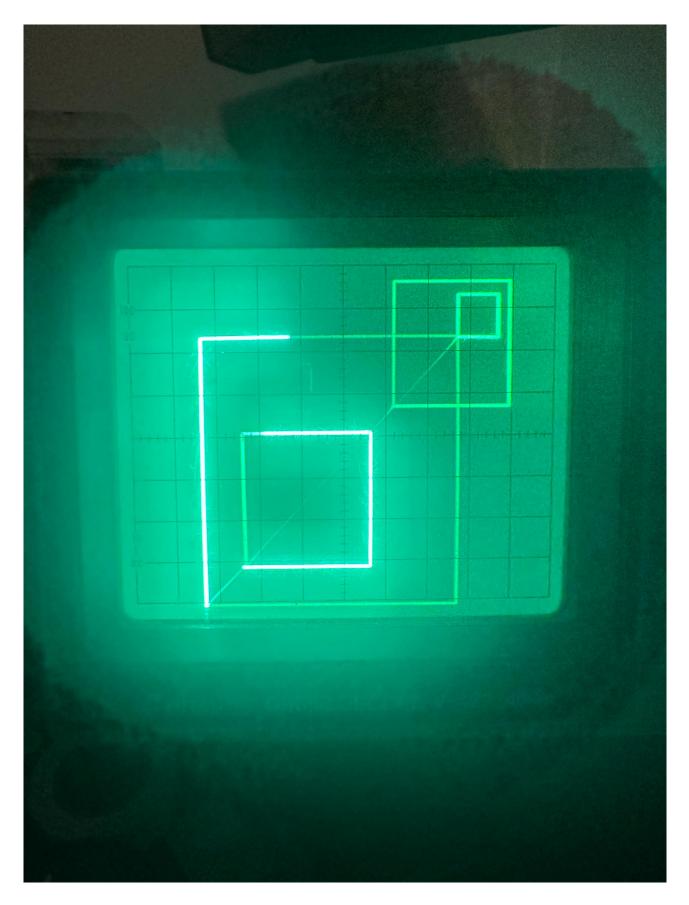

# Dandy VGA [96]

• Author: Blaise Saunders

- Description: Serial vector graphics adapter

- GitHub repository

- HDL project

- Mux address: 96

- Extra docs

- Clock: 10000000 Hz

- External hardware: 2 DACs, vector graphics display, fastish UART input

#### How it works

This module is a serial vector graphics adapter [ or VGA for short ;  $\hat{}$  ] it has a small set of state machine based primitive instructions that can be programmed over serial and animated etc. It does a nice job of drawing squares and I'm hoping 3D graphics can be achieved with use of the line primitive. There are 16 instruction registers that can be programmed and updated live over serial.

#### How to test

The device outputs 8 bits on the bidirectional IO and 8 bits on the output pins, one is for X and the other is for Y display on a vector graphics display, most oscilloscopes with XY mode should work well. Can convert to analog with a simple R2R resistor ladder or whatever method you like best :). You can find some test code that can be flashed a Teensy or similar and hook it up to pin 1 on the input to send some primitives to be drawn: https://github.com/DavidoRotho/tt04-davidroth-dandy-vga

| # | Input                                                                       | Output                        | Bidirectional              |

|---|-----------------------------------------------------------------------------|-------------------------------|----------------------------|

| 0 | UART RX input,<br>921600 baud input.<br>Tested with Teensy<br>4.1           | binary X axis output<br>[7:0] | binary Y axis output [7:0] |

| 1 | Safe/Unsafe mode<br>toggle, unsafe high.<br>Whether or not to<br>wait while | n/a                           | n/a                        |

| # | Input                                                                      | Output | Bidirectional |

|---|----------------------------------------------------------------------------|--------|---------------|

| 2 | binary graphics clock<br>divider for<br>compensating for<br>slow DAC drive | n/a    | n/a           |

|   | speed [2:7]                                                                |        |               |

| 3 | n/a                                                                        | n/a    | n/a           |

| 4 | n/a                                                                        | n/a    | n/a           |

| 5 | n/a                                                                        | n/a    | n/a           |

| 6 | n/a                                                                        | n/a    | n/a           |

| 7 | n/a                                                                        | n/a    | n/a           |

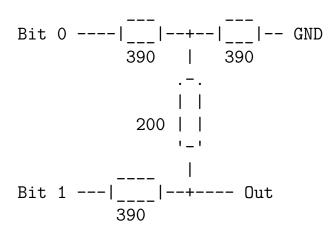

## Tiny Breakout [98]

- Author: Robbert-Jan de Jager

- Description: This is a small breakout game implemented in HDL. It uses a VGA connector to output the video signal. The game is controlled by 3 buttons. The left button moves the paddle to the left, the right button moves the paddle to the right and the action button starts the game. The game is over when all blocks are destroyed or when the ball hits the bottom of the screen.

- GitHub repository

- HDL project

- Mux address: 98

- Extra docs

- Clock: 25175000 Hz

- External hardware: 3x 2bit DAC for the red, green and blue video signals. VGA connector. 3 buttons.

#### How it works

**Basic operation** The core of the design is the vga\_timing module. This module generates all the required timing signals. Some of these signals like hsync and vsync are used to generate the video signal, while others like the horizontal and vertical position

are used to generate the graphics. The horizontal and vertical sync signals are also used for the game logic.

Before outputting the video signal the video mux selects the correct input color to display. It does so based on the highest priority component that wants to output a color.

We have multiple painter modules. These generate from the current game state and the current horizontal and vertical position the correct color to display. Ideally the painters would not contribute to the game logic, but for optimization reasons they do.

While drawing a frame the game logic keeps track of collisions. It does so by checking if multiple painters want to draw at the same position. If so it will latch a collision, which will be processed after drawing the frame.

At the end of each frame the game logic will calculate the next ball position, taking collisions into account. The collision with the paddle is special. To have an entertaining game that does not play the same every time the ball will bounce off the paddle at a different angle depending on where it hits. This is done by splitting the paddle into multiple segments and checking for collisions with these segments. The game logic will look at the segment when a paddle collision was registered. An exception to the end of frame gamestate update is the breaking of blocks. It would require too much memory to keep the updated state for the next frame. Instead we will update the row of blocks that was just finished drawing.

We can display a grid of 13x16 blocks. This requires 208 bits of memory. This is a lot of memory for such a small design and takes up a lot of space. To reduce the number of connections the state has been put into a shift register that outputs one row at a time. This shift register is rotated 13 bits when we reach the end of drawing a row of blocks. Also we can write to the shift register the new block state if a block has been broken. This is done one clock cycle before shifting to the next row. 1 clock cycle after shifting to the next row we load the current row into a buffer which will be used to update the state.

#### How to test

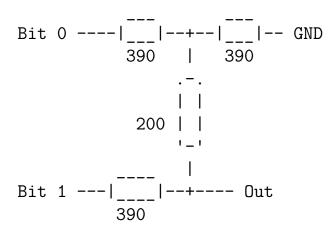

This is a small breakout game implemented in HDL. It uses a VGA connector to output the video signal. The game is controlled by 3 buttons. The left button moves the paddle to the left, the right button moves the paddle to the right and the action button starts the game. The game is over when all blocks are destroyed or when the ball hits the bottom of the screen.

**Required hardware** This project requires a VGA monitor and a VGA DAC. An easy way to create the VGA DAC is to use 3 2-bit R2R DACs. The 2-bit R2R DACs can be created using 2 resistors per bit. The resistors should be 2000hm and 3900hm. For the 3.3V power supply.

What has not been verified is the current sourcing capability of the ASIC, If it can not at least source 10mA through each pin and 30mA through the power supply pins you should add a buffer before the DAC.

The VGA DAC should be connected as follows:

Every color should have an identical copy of this DAC. The red DAC should be connected to the red VGA pin, the green DAC to the green VGA pin and the blue DAC to the blue VGA pin. The outputs of the DACs should be connected to the VGA connector. The HSync and VSync pins should also be connected to the VGA connector. The following connections need to be made to the VGA connector:

- Red DAC output to VGA connector pin 1

- Green DAC output to VGA connector pin 2

- Blue DAC output to VGA connector pin 3

- HSync to VGA connector pin 13

- VSync to VGA connector pin 14

- GND to VGA connector pin 5, 6, 7, 8

**SPI interface** For changing the game state externally you can use the SPI interface. The SPI interface returns the current game state when reading and accepts a few commands when writing. The SPI interface uses 16 bit words.

The returned state is as follows:

bit 0-12: The block state of the current row. Use HBlank and VBlank to determine which row is currently being drawn.

- bit 13: right button state

- bit 14: left button state

- bit 15: action button state

- bit 16: collision state. This bit is set when a collision has been detected.

- bit 17: ball out of bounds. This bit is set when the ball is off screen.

- bit 18: game state: 0 = game idle, 1 = game running

- bit 19-20: remaining lives

When writing the first word is the command word, the following words are the data words for the command. Command words:

- 0x0000: Do nothing. Usefull when you want to read the state.

- 0x0001: Write a row state. This will shift the state to the next row. Be sure to only use this during the VBlank and call this with 15 words to completely draw the screen.

- 0x0002: Send control word. The next word is the control word. The control word is as follows:

- bit[0]: Send the stop game command.

**Board configuration** The ASIC requires an input clock of 25.175MHz. The 7-Segment display is not used.

| # | Input         | Output             | Bidirectional                                      |

|---|---------------|--------------------|----------------------------------------------------|

| 0 | MOSI          | HSync              | MISO                                               |

| 1 | SCK           | VSync              | HBlank                                             |

| 2 | slave select  | Red output bit 0   | VBlank                                             |

| 3 | none          | Red output bit 1   | sound output. Connect to a speaker with amplifier. |

| 4 | none          | Green output bit 0 | none                                               |

| 5 | Button left   | Green output bit 1 | none                                               |

| 6 | Button right  | Blue output bit 0  | none                                               |

| 7 | Button action | Blue output bit 1  | none                                               |

# VC 16-bit CPU [99]

- Author: Paul Campbell

- Description: VC 16-bit CPU RISV-C cpu

- GitHub repository

- HDL project

- Mux address: 99

- Extra docs

- Clock: 10000000 Hz

- External hardware:

#### How it works

See the README.MD for more info

#### How to test

Included is an assembler and a memory image for executing

| # | Input     | Output       | Bidirectional  |

|---|-----------|--------------|----------------|

| 0 | ReadData0 | AddressData0 | AddressLSB     |

| 1 | ReadData1 | AddressData1 | WriteStrobe    |

| 2 | ReadData2 | AddressData2 | AddressLatchHi |

| 3 | ReadData3 | AddressData3 | AddressLatchLo |

| 4 | ReadData4 | AddressData4 | unused4        |

| 5 | ReadData5 | AddressData5 | unused5        |

| 6 | ReadData6 | AddressData6 | unused6        |

| 7 | ReadData7 | AddressData7 | InterruptIn    |

# Risc-V Nano V [100]

- Author: Michael Bell

- Description: RV32E bit serial processor

- GitHub repository

- HDL project

- Mux address: 100

- Extra docs

- Clock: 0 Hz

- External hardware:

## How it works

A minimal RV32E processor using an SPI RAM for instructions and data.

The SPI RAM and a UART are connected to the bidi IOs. The SPI RAM is clocked at the same speed as the input clock.

The CPU has no instruction or data cache and effectively runs at clock speed / 32. More details can be found in the nanoV repo.

Restrictions/unimplemented parts of RV32E:

- register x3/gp is hardcoded to 0x00001000 (this allows data in the low 6KB of RAM to be accessed cheaply).

- register x4/tp is hardcoded to 0x10000000 (this allows the GPIO and UART to be accessed cheaply)

- The ebreak instruction (and interrupts in general) are not implemented.