# **Tiny Tapeout 05 Datasheet**

Project Repository https://github.com/TinyTapeout/tinytapeout-05

August 2, 2024

Contents

### Chip map

| Projects                                                  | 10 |

|-----------------------------------------------------------|----|

| Chip ROM [0]                                              | 10 |

| TinyTapeout 05 Factory Test 1                             | 12 |

| TinyTapeout 05 Loopback Test Module 2                     | 13 |

| Leaky Integrate and Fire Neuron Model [3]                 | 14 |

| Time Multiplexed Neuron Ckt [4]                           | 16 |

| SAP-1 Computer [5]                                        | 17 |

| Current Based Leaky Integrate and Fire Model [6]          | 19 |

| TickTockTokens [7]                                        | 20 |

| Spiking LSTM Network [8]                                  | 22 |

| Integrate-and-Fire Neuron. [9]                            | 24 |

| Neural network on chip $\begin{bmatrix} 10 \end{bmatrix}$ | 26 |

| Simple Leaky Integrate and Fire (LIF) Neuron [11]         | 27 |

| e Spigot [12]                                             | 28 |

| Continued Fraction Calculator [13]                        | 30 |

| Water Pump Controller [14]                                | 32 |

| Event Denoising Circuit [15]                              | 35 |

| 7 segment seconds (Verilog Demo) [32]                     | 37 |

| Frequency Encoder/Decoder [33]                            | 39 |

| UART Greeter with RNN Module [34]                         | 41 |

| WS2812B LED strip driver [35]                             | 43 |

| Tiny Tapeout 5 Workshop [36]                              | 45 |

| Tiny Tapeout 1 [37]                                       | 46 |

| Supercon Workshop [38]                                    | 47 |

| Matrix Multiplier [39]                                    | 48 |

| Clock Divider [40]                                        | 50 |

| Binary Counter [41]                                       | 51 |

| ring osc test [42]                                        | 52 |

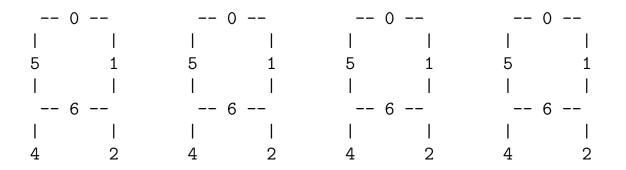

| 7 segment clock with 4 digits [43]                        | 53 |

| test001 [44]                                              | 55 |

| Hodgkin-Huxley Chip Design [45]                           | 56 |

| Character Selector [46]                                   | 58 |

| Intructouction to PRBS [47]                               | 59 |

| tto5 Supercon Project [64]                                | 60 |

| Delta Modulation Spike Encoding [65]                      | 61 |

| GameOfLife [66]                                           | 63 |

| Reflex Game [67]                                          | 64 |

| Logic Gates Tapeout [68]                                  | 65 |

| Stream Cipher w/ LSR (8 bit key) [69] $\ldots$            | 66 |

| tt5modifyd [70]                                           | 68 |

7

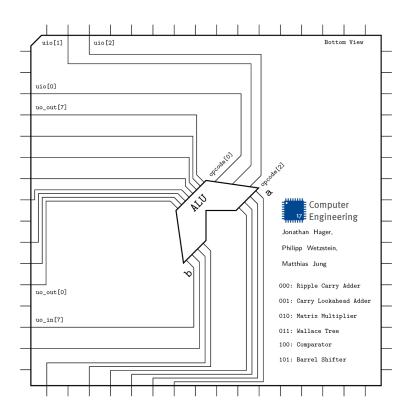

| ALU Chip [71]                                                  | . 69  |

|----------------------------------------------------------------|-------|

| Tapeout Test [72]                                              |       |

| Calculator chip [73]                                           | . 71  |

| Shifty Snakey [74]                                             | . 72  |

| Synth [75]                                                     | . 73  |

| Sawtooth Generator [76]                                        | . 74  |

| Blinking A [77]                                                |       |

| Supercon 2023 [78]                                             | . 77  |

| Sparsity Aware Matrix Vector Multiplication [79]               |       |

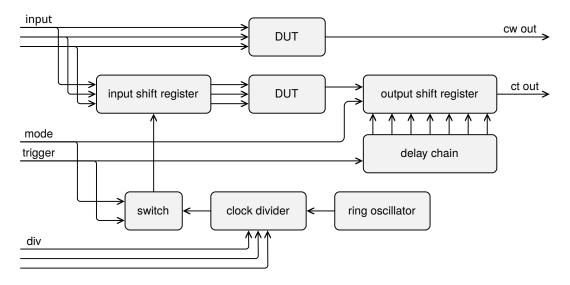

| Ring Oscillator and Clock Source Switch [96]                   | . 80  |

| Matrix Vector Multiplication (Verilog Demo) [97]               | . 81  |

| IDK WHAT TO DO [98]                                            |       |

| 7-segment display logic system [99]                            | . 83  |

| Hardware Trojan Example [100]                                  |       |

| Analog Clock [101]                                             |       |

| 7 segment display [102]                                        |       |

| W_Li_10/28 [103]                                               | . 88  |

| Supecon Gate Play [104]                                        |       |

| ECE 183 - Integrate and Fire Network Chip Design [105]         |       |

| tto5 [106]                                                     |       |

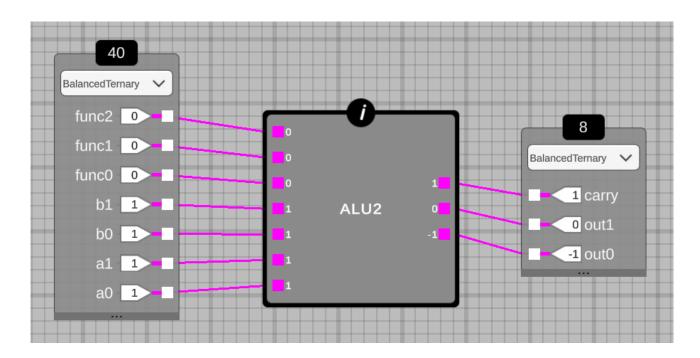

| REBEL-2 Balanced Ternary ALU [107]                             | . 93  |

| Stochastic Multiplier [108]                                    | . 95  |

| 7 segment seconds - count down [109]                           | . 96  |

| TT05 Submission [110]                                          | . 98  |

| Leaky Integrate-and-Fire Neuron [111]                          |       |

| Count via LFSR [128]                                           |       |

| I2C BERT [130]                                                 |       |

| tt05-loopback tile with input skew measurement [132]           |       |

| Flappy VGA [134]                                               |       |

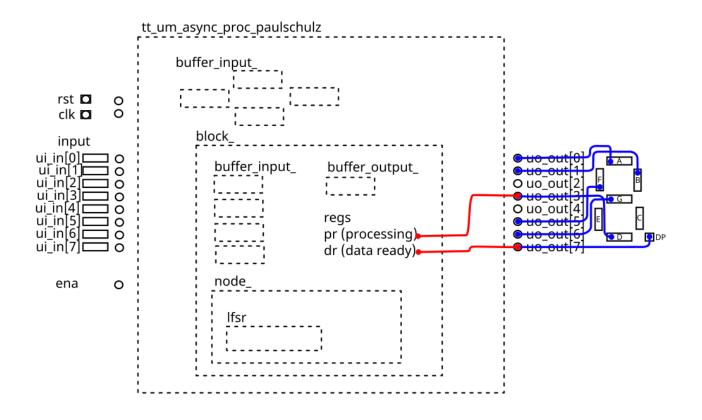

| Asynchronous Parallel Processor Demonstrator [136]             |       |

| Hex Countdown [138]                                            | . 108 |

| Matrix multiply coprocessor (8x8 1bit) [140]                   |       |

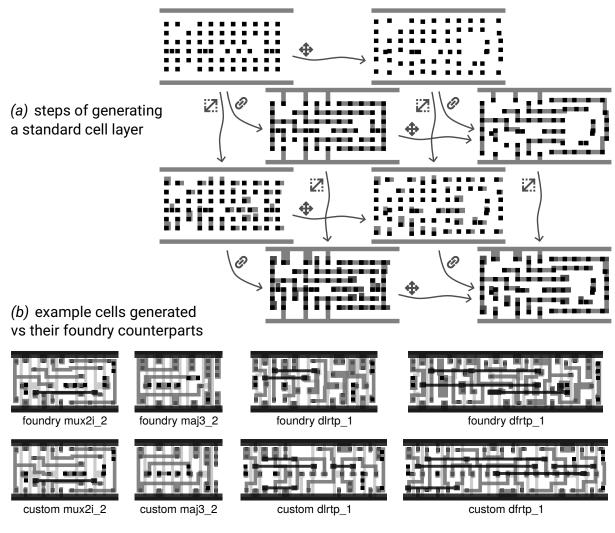

| Standard cell generator and tester [142]                       | 110   |

| Winner-Take-All Network (Verilog Demo) [160]                   |       |

| Lion cage [161]                                                |       |

| Brain Inspired Random Dropout Circuit [162]                    |       |

| Event-Based Denoising Circuit [163]                            |       |

| RAM cell test [164]                                            |       |

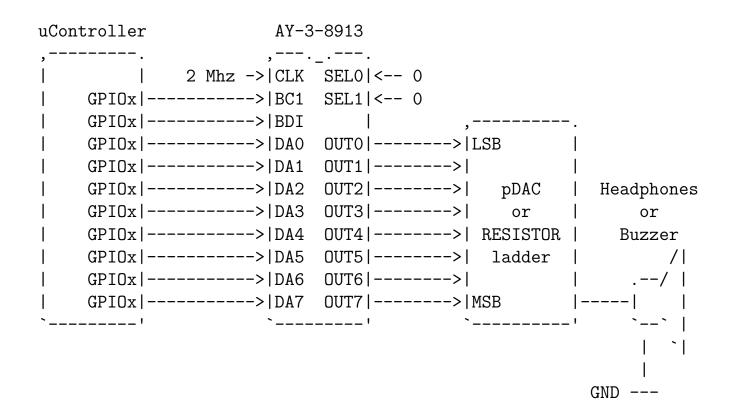

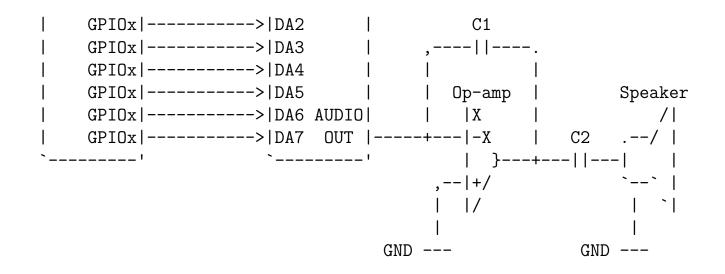

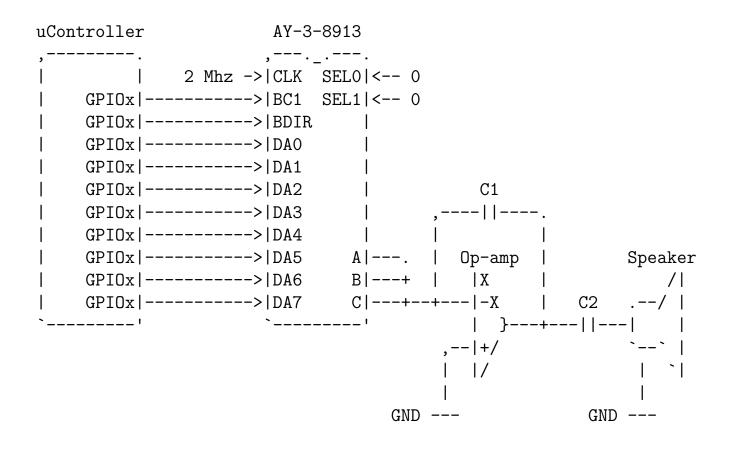

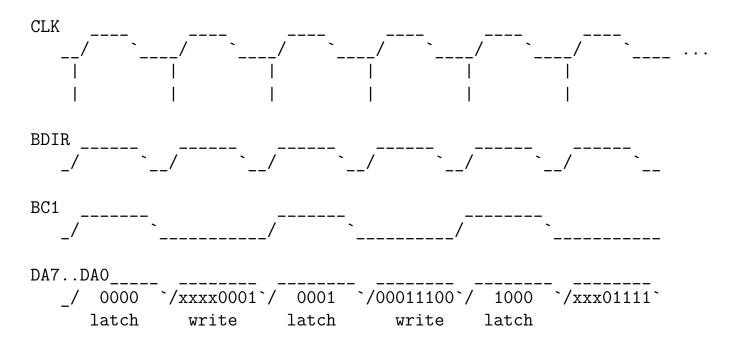

| Classic 8-bit era Programmable Sound Generator AY-3-8913 [165] |       |

| RNN (Demo) [166]                                               |       |

| STDP Neuron [167]                                              |       |

| Basic Spiking Neural Network [168]                             |       |

|                                                                |       |

| 8 bit floating point adder [169]                              | 133 |

|---------------------------------------------------------------|-----|

| Perceptron Hardcoded [170]                                    |     |

| Cheap and quick STDP [171]                                    |     |

| Brain-Inspired Oscillatory Network [172]                      | 138 |

| UART uwuifier [173]                                           |     |

| Perceptron and basic binary neural network [174]              |     |

| Leaky Integrate-and-Fire Neuron [175]                         | 141 |

| 7 segment seconds [192]                                       | 144 |

| UABC-ELECTRONICA [194]                                        |     |

| bytebeat [196]                                                | 147 |

| Super Mario Tune on A Piezo Speaker [197]                     | 149 |

| Byte Computer [198]                                           |     |

| 7 segment seconds (VHDL Demo) [199]                           | 153 |

| 4-Bit ALU [200]                                               |     |

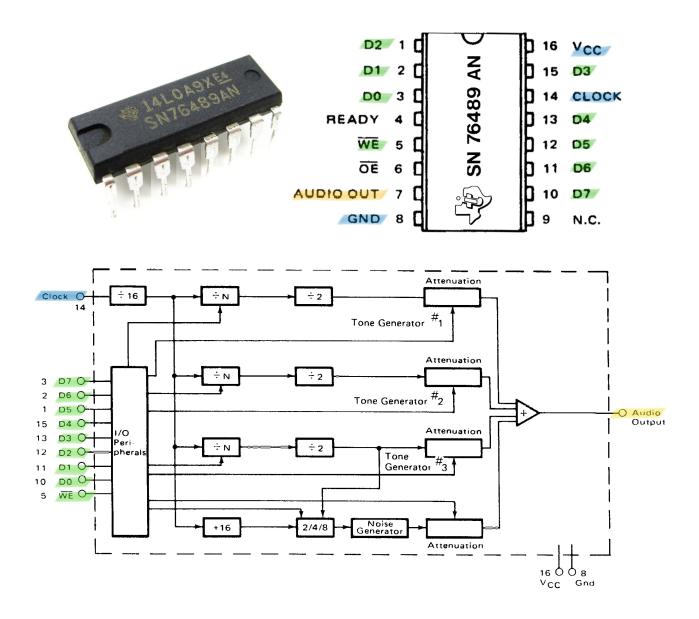

| Classic 8-bit era Programmable Sound Generator SN76489 [201]  | 157 |

| Miniature Programmable Interrupt Timer [202]                  | 166 |

| 7-segment Name Display [203]                                  | 167 |

| Tetris [204]                                                  | 169 |

| Simple_Timer-MBA [205]                                        |     |

| UART Transceiver [206]                                        | 171 |

| AGL CorticoNeuro-1 [207]                                      | 173 |

| Leaky-Integrated Fire Neuron [224]                            | 175 |

| MyUART [225]                                                  |     |

| UART test [226]                                               | 178 |

| Heart Rhythm Analyzer [227]                                   | 179 |

| Spike-timing dependent plasticity (Verilog Demo) [228]        |     |

| Tiny Tapeout 5 TM project1 [229]                              | 182 |

| Thermocouple-to-temperature converter (digital backend) [230] | 183 |

| Naive 8-bit Binary Counter [231]                              | 185 |

| tinyscanchain Test Design [232]                               | 186 |

| 6 digit chronometer. [233]                                    |     |

| Convolutional Network Circuit Chip Design [234]               | 188 |

| Matrix Vector Multiplication Accelerator [235]                | 189 |

| Perceptron (Neuromeme) [236]                                  |     |

| 4 Bit ALU [237]                                               |     |

| Binary Neural Network (Verilog Demo) [238]                    | 194 |

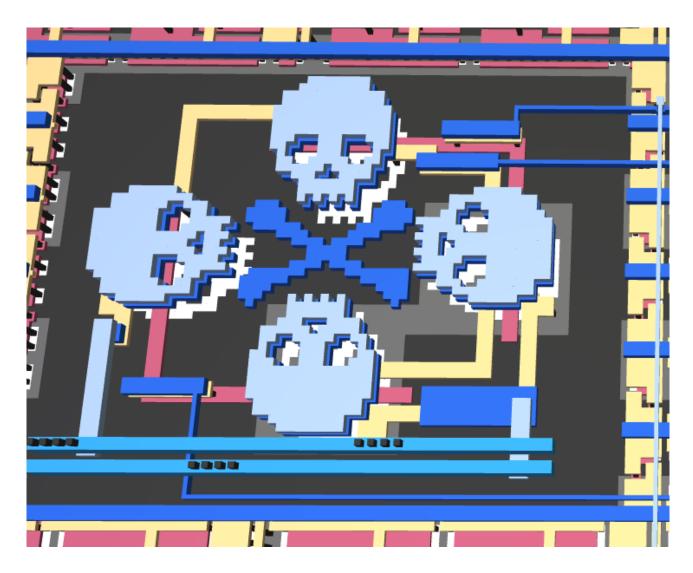

| SkullFET [239]                                                | 196 |

| Wavetable Sound Generator [256]                               | 198 |

| PWM signal generation with Winner-Take-All selection [258]    | 200 |

| Multimode Modem [260]                                         | 202 |

| Analog emulation monosynth [262]                              | 204 |

| Tiny Game of Life [264]                                       | 208 |

| Stack Machine [266]                                                         | 210 |

|-----------------------------------------------------------------------------|-----|

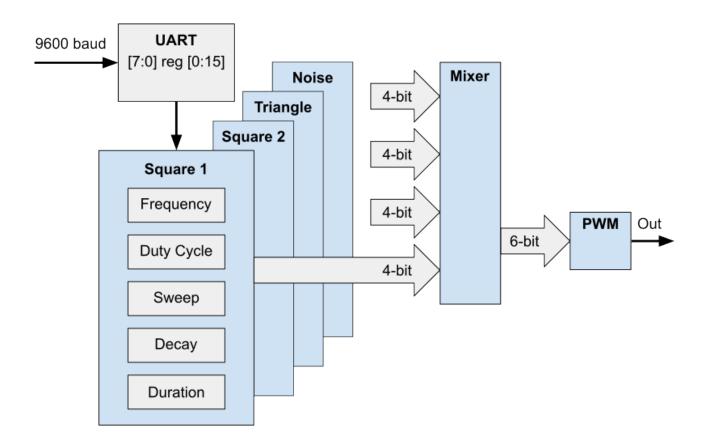

| ChipTune [268]                                                              | 211 |

| Game of Life 8x8 (siLife) [270]                                             |     |

| TT05 Analog Testmacro (Ringo, DAC) [271]                                    |     |

| RBUART [290]                                                                |     |

| 8-bit Floating-Point Adder [292]                                            |     |

| 6 bit Counter and Piano Music created by Chip Inventor [294]                | 219 |

| 4 Bit Pipelined Multiplier [296]                                            |     |

| 2-Bit ALU + Dice [298]                                                      | 221 |

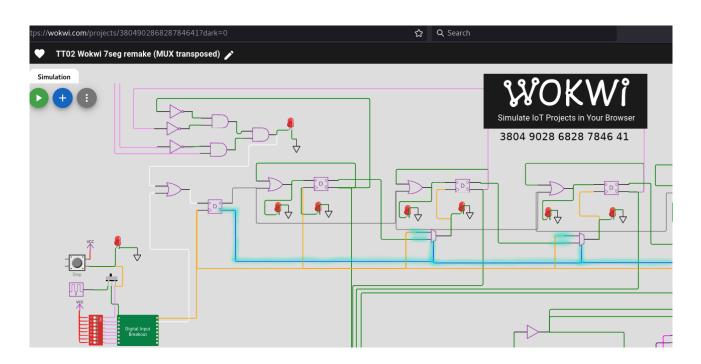

| TT02 Wokwi 7seg remake [300]                                                | 223 |

| ping pong asic [302]                                                        | 225 |

| A Boolean function based pseudo random number generator (PRNG) [320] .      | 228 |

| Digital Desk Clock [322]                                                    | 232 |

| 4-bit FIFO/LIFO [324]                                                       |     |

| One Sprite Pony [326]                                                       |     |

| 4 bit Sync Gray Code Counter [328]                                          | 237 |

| Clock and Random Number Gen [330]                                           |     |

| TT05 Analog Test [332]                                                      |     |

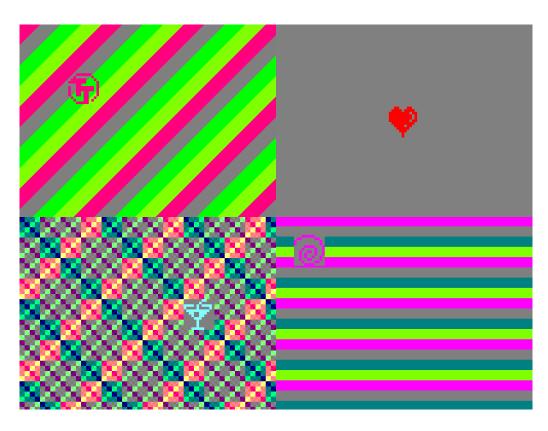

| VGA Experiments [334]                                                       |     |

| Rule110 cell automata [384]                                                 |     |

| No Time for Squares [390]                                                   |     |

| Game of Life 8x32 (siLife) [396]                                            |     |

| TROS [398]                                                                  |     |

| ChatGPT designed Spiking Neural Network [450]                               |     |

| Karplus-Strong String Synthesis [454]                                       |     |

| VGA Dino Game [458]                                                         |     |

| Dual Compute Unit [460]                                                     |     |

| Collatz conjecture brute-forcer [462]                                       |     |

| Field Programmable Neural Array [518]                                       |     |

| DFFRAM Example (128 bytes) [526]                                            |     |

| Chonky Spiking Neural Net [582]                                             | 267 |

| Hodgkin-Huxley Neuron [590]                                                 |     |

| PRBS Generator [641]                                                        |     |

| Stop Watch [643]                                                            | 276 |

| vga_spi_rom [645]                                                           |     |

| RO and counter [647]                                                        |     |

| 8-Bit Shift Register with Output Latches 74HC595 [649]                      |     |

| Neptune guitar tuner (proportional window, version b, debug output on bidir |     |

| pins, larger set of frequencies) [651]                                      | 284 |

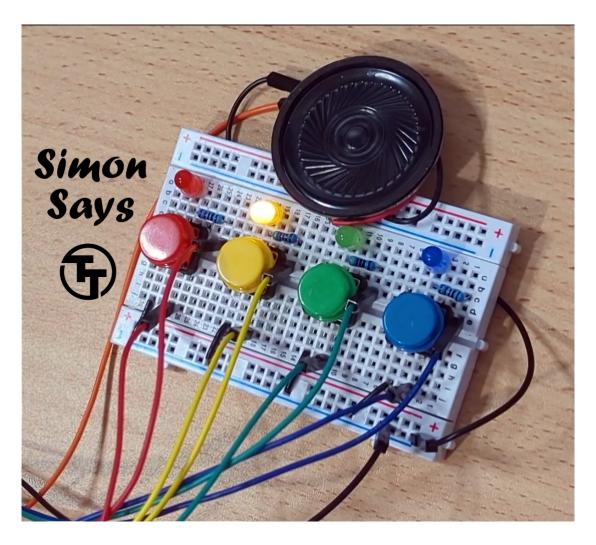

| Simon Says game [653]                                                       |     |

| KianV uLinux SoC [654]                                                      |     |

| Ring oscillator with counter [655]                                          |     |

| cpu_8bit [705]                                                                                | . 292                        |

|-----------------------------------------------------------------------------------------------|------------------------------|

| VGA clock [707]                                                                               |                              |

| 7 segment seconds (Verilog Demo) [709]                                                        | . 295                        |

| Frequency counter [711]                                                                       | . 297                        |

| RGB Mixer [713]                                                                               | . 299                        |

| SPI Peripheral [715]                                                                          | . 300                        |

| Multiplexed clock [717]                                                                       | . 302                        |

| Shaman: SHA-256 hasher [718]                                                                  | . 305                        |

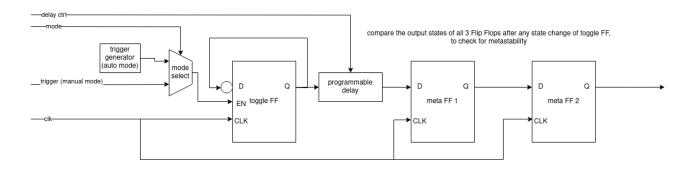

| metastability experiment [719]                                                                | . 309                        |

|                                                                                               |                              |

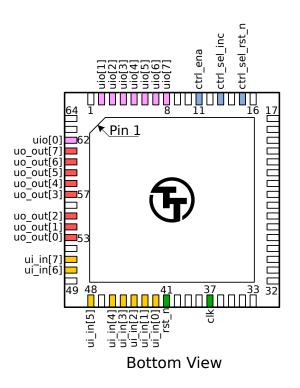

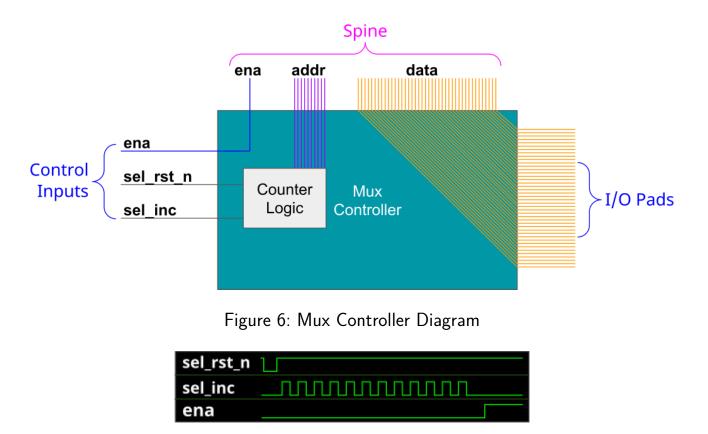

| Pinout                                                                                        | 311                          |

| Pinout<br>The Tiny Tapeout Multiplexer                                                        | 311<br>312                   |

|                                                                                               | 312                          |

| The Tiny Tapeout Multiplexer                                                                  | <b>312</b><br>. 312          |

| The Tiny Tapeout Multiplexer<br>Overview                                                      | <b>312</b><br>. 312<br>. 312 |

| The Tiny Tapeout Multiplexer         Overview       Overview         Operation       Overview | <b>312</b><br>. 312<br>. 312 |

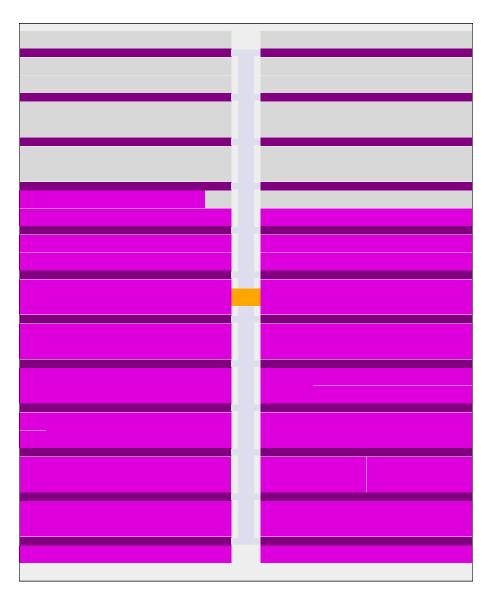

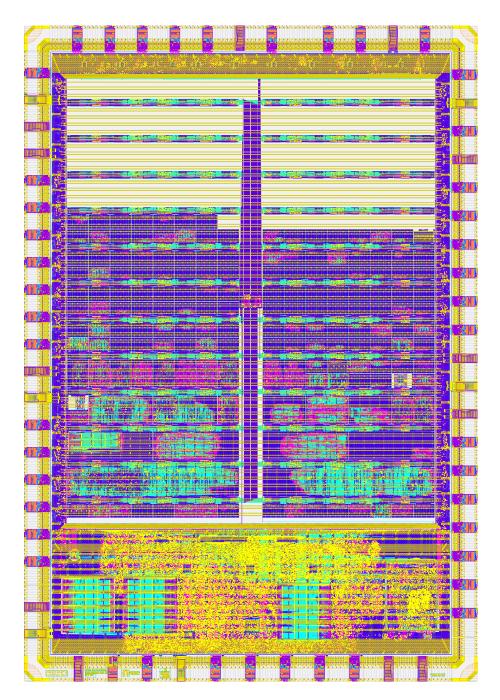

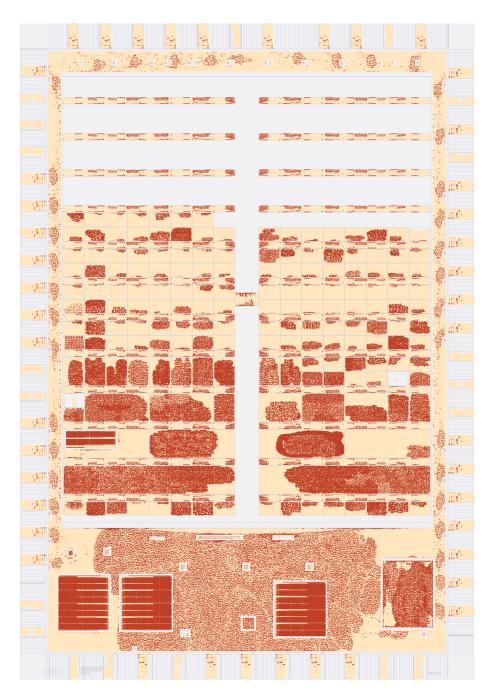

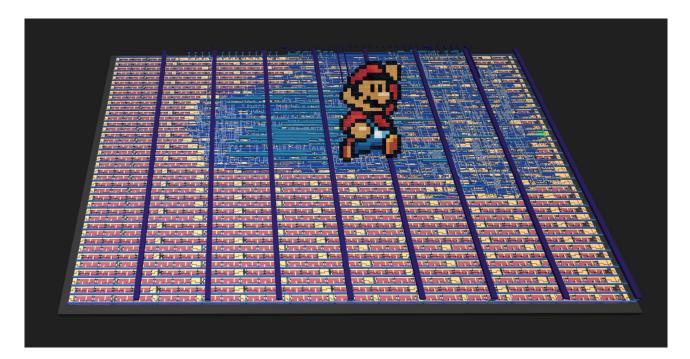

# Chip map

Figure 1: Full chip map

Figure 2: GDS render

Figure 3: Logic density (local interconnect layer)

# **Projects**

## Chip ROM [0]

- Author: Uri Shaked

- Description: ROM with information about the chip

- GitHub repository

- HDL project

- Mux address: 0

- Extra docs

- Clock: 0 Hz

- External hardware:

#### How it works

ROM memory that contains information about the Tiny Tapeout chip. The ROM is 8-bit wide and 128 bytes long.

| Address | Length | Encoding  | Description                             |

|---------|--------|-----------|-----------------------------------------|

| 0       | 8      | 7-segment | Shuttle name (e.g. "tt05"), null-padded |

| 8       | 8      | 7-segment | Git commit hash                         |

| 32      | 96     | ASCII     | Chip descriptor (see below)             |

**The ROM layout** The ROM layout is as follows:

**The chip descriptor** The chip descriptor is a simple null-terminated string that describes the chip. Each line is a key-value pair, separated by an equals sign. It contains the following keys:

| Key  | Description                                                                      | Example value                                  |

|------|----------------------------------------------------------------------------------|------------------------------------------------|

| repo | The identifier of the shuttle<br>The name of the repository<br>The commit hash * | tt05<br>TinyTapeout/tinytapeout-05<br>a1b2c3d4 |

• The commit hash is only included for Tiny Tapeout 5 and later.

Here is a complete example of a chip descriptor:

```

shuttle=tt05

repo=TinyTapeout/tinytapeout-05

commit=a1b2c3d4

```

**How the ROM is generated** The ROM is automatically generated by tt-supporttools while building the final GDS file of the chip. Look at the rom.py file in the repository for more details.

#### How to test

Read the ROM contents by setting the address pins and reading the data pins. The first 16 bytes of the ROM are 7-segment encoded and contain the shuttle name and commit hash. You can read them by toggling the first four DIP switches and observing the on-board 7-segment display.

| # | Input               | Output              | Bidirectional |

|---|---------------------|---------------------|---------------|

| 0 | addr[0]             | data[0]             | none          |

| 1 | addr1               | data1               | none          |

| 2 | addr <mark>2</mark> | data <mark>2</mark> | none          |

| 3 | addr[3]             | data[3]             | none          |

| 4 | addr[4]             | data[4]             | none          |

| 5 | addr[5]             | data[5]             | none          |

| 6 | addr[6]             | data[6]             | none          |

| 7 | addr[7]             | data[7]             | none          |

### TinyTapeout 05 Factory Test 1

- Author: Sylvain Munaut

- Description: Factory test module

- GitHub repository

- HDL project

- Mux address: 1

- Extra docs

- Clock: 0 Hz

- External hardware:

#### How it works

If sel is high, then a counter is output on the output pins and the bidirectional pins (data\_o = counter\_o = counter). If sel is low, the bidirectional pins are mirrored to the output pins (data\_o = data\_i).

#### How to test

Set sel high and observe that the counter is output on the output pins (data\_o) and the bidirectional pins (counter o).

Set sel low and observe that the bidirectional pins are mirrored to the output pins  $(data_o = data_i)$ .

| # | Input | Output                | Bidirectional            |

|---|-------|-----------------------|--------------------------|

| 0 | sel   | data_o[0]             | data_i[0] / counter_o[0] |

| 1 | none  | data_o1               | data_i1 / counter_o1     |

| 2 | none  | data_o <mark>2</mark> | data_i2 / counter_o2     |

| 3 | none  | data_o[3]             | data_i[3] / counter_o[3] |

| 4 | none  | data_o[4]             | data_i[4] / counter_o[4] |

| 5 | none  | data_o[5]             | data_i[5] / counter_o[5] |

| 6 | none  | data_o[6]             | data_i[6] / counter_o[6] |

| 7 | none  | data_o[7]             | data_i[7] / counter_o[7] |

### TinyTapeout 05 Loopback Test Module 2

- Author: Sylvain Munaut

- Description: Loopback test module

- GitHub repository

- HDL project

- Mux address: 2

- Extra docs

- Clock: 0 Hz

- External hardware:

#### How it works

Input 0 goes to output 0 through 6. Output 7 is input4 & input5 & input6 & input7

#### How to test

Toggle input 0, measure the time for output 0 to change.

| # | Input | Output                             | Bidirectional |

|---|-------|------------------------------------|---------------|

| 0 | in0   | mirrors in0                        | none          |

| 1 | none  | mirrors in0                        | none          |

| 2 | none  | mirrors in0                        | none          |

| 3 | none  | mirrors in0                        | none          |

| 4 | in4   | mirrors in0                        | none          |

| 5 | in5   | mirrors in0                        | none          |

| 6 | in6   | mirrors in0                        | none          |

| 7 | in7   | the value of in4 & in5 & in6 & in7 | none          |

### Leaky Integrate and Fire Neuron Model [3]

- Author: Miles Segal

- Description: Models the functionality of a leaky integrate and fire neuron, of the style tipically found in spiking neural networks

- GitHub repository

- HDL project

- Mux address: 3

- Extra docs

- Clock: 10000000 Hz

- External hardware:

#### How it works

Uses a set of registers to divide the clock, and then some combinational logic to convert from binary to decimal for the display.

Puts the bottom 8 bits of the counter on the bidirectional outputs.

With all the inputs set to 0, the internal 24 bit compare is set to 10,000,000. This means the counter will increment by one each second.

If any inputs are non zero, then the input will be used as an bits 11 to 18 of the 24 bit compare register. Example: setting the inputs to 00010000 will program 16384 into the compare register. With a 10MHz clock the counter will increment  $\sim$ 610 times per second.

#### How to test

After reset, the counter should increase by one every second with a 10MHz input clock. Experiment by changing the inputs to change the counting speed.

| # | Input          | Output    | Bidirectional          |

|---|----------------|-----------|------------------------|

| 0 | compare bit 11 | segment a | second counter bit 0   |

| 1 | compare bit 12 | segment b | second counter bit $1$ |

| 2 | compare bit 13 | segment c | second counter bit 2   |

| 3 | compare bit 14 | segment d | second counter bit 3   |

| 4 | compare bit 15 | segment e | second counter bit 4   |

| # | Input | Output    | Bidirectional                                                        |

|---|-------|-----------|----------------------------------------------------------------------|

| 6 | •     | segment g | second counter bit 5<br>second counter bit 6<br>second counter bit 7 |

### Time Multiplexed Neuron Ckt [4]

- Author: Karina Aguilar

- Description: Utilize leaky-integrate-and-fire neurons to make multiple neurons

- GitHub repository

- HDL project

- Mux address: 4

- Extra docs

- Clock: 10000000 Hz

- External hardware:

#### How it works

Apply an input current to the LIF neurons through the switches.

This will add to the membrane potential that decays over time. If the membrane potential exceeds the threshold, then a spike is triggered.

#### How to test

After reset, the membrane potential will be set to 0.

Then change the inputs to change the current. A higher current should trigger a higher firing rate.

| # | Input          | Output                   | Bidirectional |

|---|----------------|--------------------------|---------------|

| 0 | current bit 11 | membrane potential bit a | spike bit 1   |

| 1 | current bit 12 | membrane potential bit b | spike bit 2   |

| 2 | current bit 13 | membrane potential bit c | spike bit 3   |

| 3 | current bit 14 | membrane potential bit d | spike bit 4   |

| 4 | current bit 15 | membrane potential bit e | spike bit 5   |

| 5 | current bit 16 | membrane potential bit f | unspecified   |

| 6 | current bit 17 | membrane potential bit g | unspecified   |

| 7 | current bit 18 | membrane potential bit h | unspecified   |

### SAP-1 Computer [5]

- Author: Brandon Cruz

- Description: Simple as Possible computer into ASIC

- GitHub repository

- HDL project

- Mux address: 5

- Extra docs

- Clock: 10000000 Hz

- External hardware: Oscilloscope

#### How it works

Originally, Malvino and Brown presented the SAP-1 architecture in a book called Digital Computer Electronics. The design gained massive popularity when it was build as a bread board computer by Ben Eater on a series of YouTube videos. The architecture contains various modules, including the instruction execution set gives the SAP-1 a total of six stages from 0 to 5, repeating all over again.

- Clock

- Program Counter

- Register A

- Register B

- Adder

- Memory

- Instruction Register

- Bus

- Controller This design doesn't have inputs, it is dependent only on the clock that coordinates sequence of the computer's operation. Its operation consists on the communication that that bus provides between modules; the signal load dumps information into a module and the enable signal allows the bus to receive a signal. The bus is 8-bit width since it is an 8 bit computer, and the registers are also 8-bit registers. The computer can only perform addition, whether it is positive numbers or negative numbers (substraction). The signals information is stored within the memory module. There bus operations are coordinated with a series of multiplexers and

The more important module is the controller. It controlls the assertion execution according to the stimuli from the stages. The stages 3 to 5 five depend on the instructions of the operation codes.

#### How to test

Design Output Reading Section The design is engineered to read the output signal generated from the bus, which contains the information of the add and subtract operations executed by the design. Currently, the only method to read the signals is through an oscilloscope. However, a significant enhancement would be the implementation of a state machine controlling a 3 7-segment display to show the numbers on the 8-bit bus (up to 255).

| # | Input | Output             | Bidirectional |

|---|-------|--------------------|---------------|

| 0 | n/a   | bus[0]             | n/a           |

| 1 | n/a   | bus1               | n/a           |

| 2 | n/a   | bus <mark>2</mark> | n/a           |

| 3 | n/a   | bus[3]             | n/a           |

| 4 | n/a   | bus[4]             | n/a           |

| 5 | n/a   | bus[5]             | n/a           |

| 6 | n/a   | bus[6]             | n/a           |

| 7 | n/a   | bus[7]             | n/a           |

### Current Based Leaky Integrate and Fire Model [6]

- Author: Shatoparba Banerjee

- Description: Implement a current based LIF neuron

- GitHub repository

- HDL project

- Mux address: 6

- Extra docs

- Clock: 10000000 Hz

- External hardware:

#### How it works

Current-based LIF neurons are a simplified abstraction of the behavior of real neurons, and they are often used in large-scale neural network simulations due to their computational efficiency. These models are useful for studying the dynamics of spiking neurons and their role in information processing in the brain.

#### How to test

To test the current-based LIF project, follow these steps: Connect the LIF module to the input switches, 7-segment display, and clock source as specified in the Verilog module. Use input switches to control the input current, and observe the 7-segment display for spike detection, while ensuring the clock signal is appropriately set to provide the desired clock frequency for the simulation.

| # | Input          | Output                   | Bidirectional |

|---|----------------|--------------------------|---------------|

| 0 | current bit 11 | membrane potential bit a | spike bit 0   |

| 1 | current bit 12 | membrane potential bit b | unspecified   |

| 2 | current bit 13 | membrane potential bit c | unspecified   |

| 3 | current bit 14 | membrane potential bit d | unspecified   |

| 4 | current bit 15 | membrane potential bit e | unspecified   |

| 5 | current bit 16 | membrane potential bit f | unspecified   |

| 6 | current bit 17 | membrane potential bit g | unspecified   |

| 7 | current bit 18 | membrane potential bit h | unspecified   |

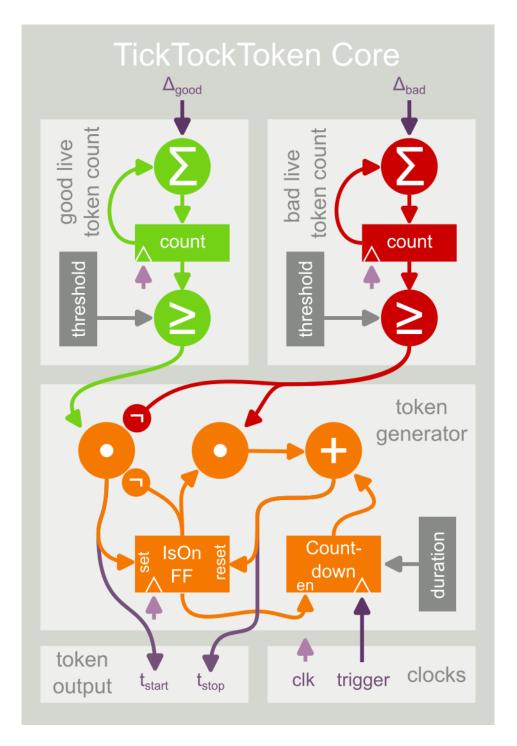

### TickTockTokens [7]

- Author: Johannes Leugering

- Description: Implementation of a processor that uses Tick Tock Tokens for event-based computation.

- GitHub repository

- HDL project

- Mux address: 7

- Extra docs

- Clock: 10000000 Hz

• External hardware: arduino to generate I/O

#### How it works

Each TickTockToken (ttt) is indicated by two messages, a start and an end event. A ttt-Processor uses these tokens to perform event-based computations in a fashion inspired by Time Petri Nets.

#### How to test

If I didn't get lazy half-way though, the test-script provided in the repo should run a test model successfully, and the documentation should provide a more through explanation.

| # | Input             | Output     | Bidirectional    |

|---|-------------------|------------|------------------|

| 0 | instruction bit 0 | data bit 0 | token start flag |

| 1 | instruction bit 1 | data bit 1 | token stop flag  |

| 2 | instruction bit 2 | data bit 2 | data bit 2       |

| 3 | instruction bit 3 | data bit 3 | data bit 3       |

| 4 | (reserved)        | data bit 4 | data bit 4       |

| 5 | (reserved)        | data bit 5 | data bit 5       |

| 6 | (reserved)        | data bit 6 | data bit 6       |

| 7 | (reserved)        | data bit 7 | data bit 7       |

### Spiking LSTM Network [8]

- Author: Skye Gunasekaran

- Description: A leaky integrate and fire neuron with adaptive threshold.

- GitHub repository

- HDL project

- Mux address: 8

- Extra docs

- Clock: None Hz

- External hardware: None

#### How it works

A Leaky Integrate-and-Fire (LIF) neuron is a simple mathematical model used in neuroscience and computational neuroscience to describe the behavior of individual neurons. It provides a simplified yet effective way to simulate the behavior of real neurons. In the neuron, there are two key elements: the current and the threshold. If the current surpasses the threshold, a spike is emitted, otherwise, the spike is 0 (resting). In this spiking LSTM implementation, the neuron's threshold is adaptive, and will increase when the threshold is passed. When the neuron fails to reach the threshold, it will slowy decay back to the initial threshold.

#### How to test

After applying the reset, the variables should be initialized, and a current can be applied. The testbench will record the current, threshold, and spiking behavior of the neuron. When a higher current is applied, you can see how the threshold increases, and vice versa when a spike is not emitted.

| # | Input                 | Output              | Bidirectional     |

|---|-----------------------|---------------------|-------------------|

| 0 | clk Clock input       | uo_out Spike output | uio_in Unused     |

| 1 | rst_n Reset signal    | n/a                 | uio_out Threshold |

| 2 | ui_in Voltage current | n/a                 | uio_oe Unused     |

| 3 | ena Unused            | n/a                 | n/a               |

| 4 | n/a                   | n/a                 | n/a               |

| 5 | n/a                   | n/a                 | n/a               |

| 6 | n/a                   | n/a                 | n/a               |

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 7 | n/a   | n/a    | n/a           |

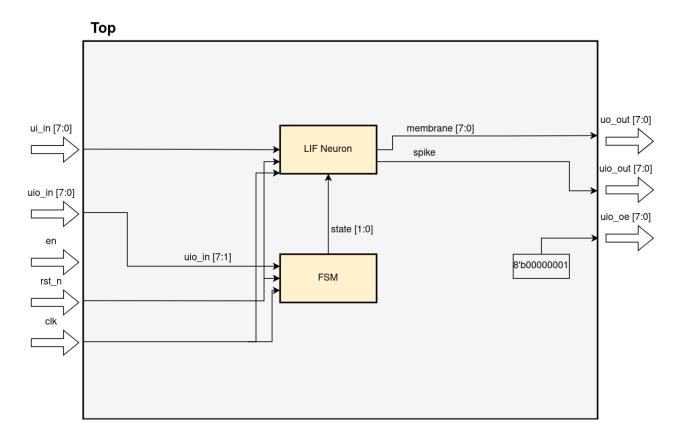

### Integrate-and-Fire Neuron. [9]

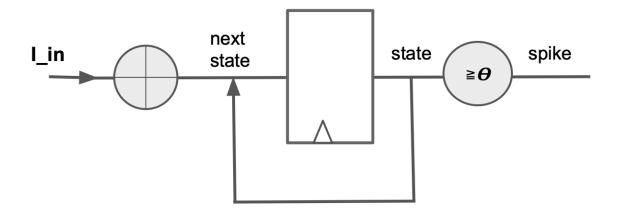

Figure 1: Top-level diagram of the Integrate-and-Fire neuron model.

- Author: Kembay Assel

- Description: Implement an IF neuron in silicon.

- GitHub repository

- HDL project

- Mux address: 9

- Extra docs

- Clock: 10000000 Hz

- External hardware:

#### How it works

Apply an input current injection to the IF neuron using switches. This gets added to a membrane potential. If the membrane potential exceeds the threshold, then it triggers a spike.

#### How to test

An 8-bit input current is applied to the IF neuron through the designated input (i.e., uio\_in). The membrane potential of the IF neuron will respond to the applied input current. Larger currents will lead to a higher membrane potential. The neuron is designed to generate a spike when the membrane potential exceeds a certain threshold.

| # | Input          | Output                   | Bidirectional |

|---|----------------|--------------------------|---------------|

| 0 | current bit 11 | membrane potential bit a | spike bit 0   |

| 1 | current bit 12 | membrane potential bit b | unspecified   |

| 2 | current bit 13 | membrane potential bit c | unspecified   |

| 3 | current bit 14 | membrane potential bit d | unspecified   |

| 4 | current bit 15 | membrane potential bit e | unspecified   |

| 5 | current bit 16 | membrane potential bit f | unspecified   |

| 6 | current bit 17 | membrane potential bit g | unspecified   |

| 7 | current bit 18 | membrane potential bit h | unspecified   |

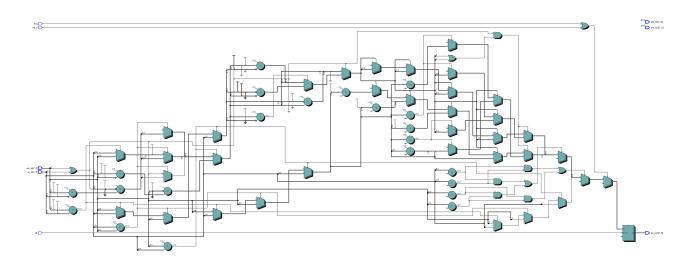

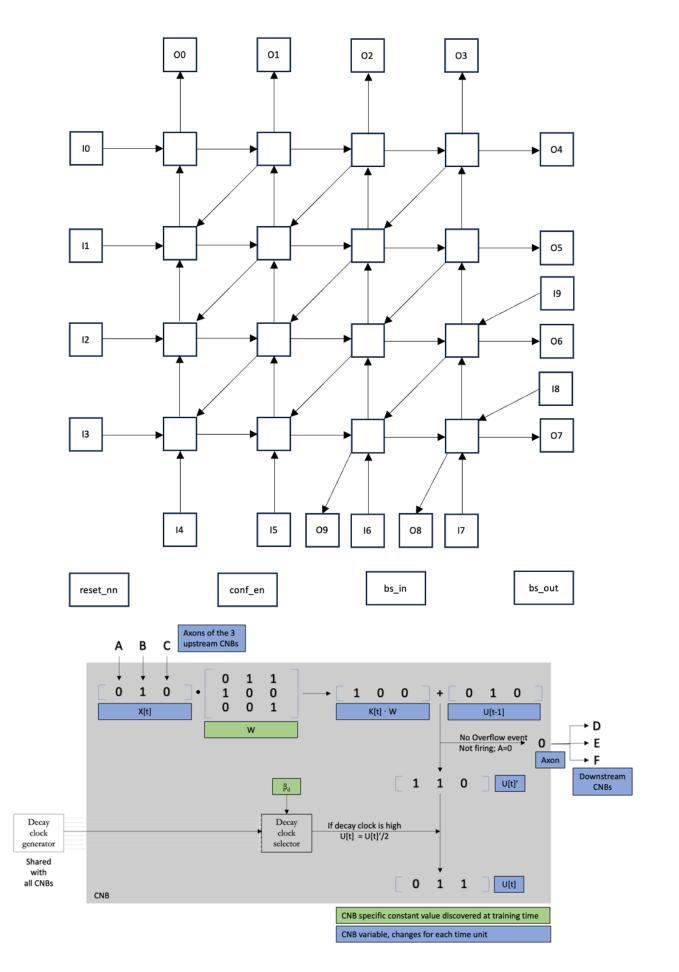

### Neural network on chip [10]

- Author: Faculty of Technical Sciences Cacak, University of Kragujevac

- Description: Neural network built out of perceptrons

- GitHub repository

- HDL project

- Mux address: 10

- Extra docs

- Clock: 50 000 000 Hz

- External hardware:

#### How it works

Network calculates output based on user provided input and predefined weight parameters of neural network

#### How to test

Drive inputs to [7:0] ui\_in and result of computation of neural network can be obesrved on [7:0] uo\_out

| # | Input    | Output                | Bidirectional |

|---|----------|-----------------------|---------------|

| 0 | ui_in[0] | uo_out[0]             | none          |

| 1 | ui_in1   | uo_out1               | none          |

| 2 | ui_in2   | uo_out <mark>2</mark> | none          |

| 3 | ui_in[3] | uo_out[3]             | none          |

| 4 | ui_in[4] | uo_out[4]             | none          |

| 5 | ui_in[5] | uo_out[5]             | none          |

| 6 | ui_in[6] | uo_out[6]             | none          |

| 7 | ui_in[7] | uo_out[7]             | none          |

### Simple Leaky Integrate and Fire (LIF) Neuron [11]

- Author: Phillip Marlowe

- Description: Given input current, spike when threshold is reached (also assume any files with the letters LFI should be LIF)

- GitHub repository

- HDL project

- Mux address: 11

- Extra docs

- Clock: 10000000 Hz

- External hardware:

#### How it works

Based on input current, calculation is made using it and previous membrane potential. If current membrane potential is above pre-set threshold then spike!

#### How to test

After reset, input some current and see what happens. Should see an increase on output and possibly a spike eventually.

A current input of 100 after 20 cycles should produce a spike.

| # | Input                                                  | Output                                                            | Bidirectional                             |

|---|--------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------|

| 0 | clk_i is the clock                                     | nu_o is the next<br>membrane potential                            | msb bit of uio_oe is connected to spike_o |

| 1 | current_i is the<br>current input to the<br>LFI neuron | spike_o is the single<br>bit to show when the<br>neuron is firing | n/a                                       |

| 2 | rst_n is for reset                                     | n/a                                                               | n/a                                       |

| 3 | n/a                                                    | n/a                                                               | n/a                                       |

| 4 | n/a                                                    | n/a                                                               | n/a                                       |

| 5 | n/a                                                    | n/a                                                               | n/a                                       |

| 6 | n/a                                                    | n/a                                                               | n/a                                       |

| 7 | n/a                                                    | n/a                                                               | n/a                                       |

### e Spigot [12]

- Author: diadatp

- Description: Spigot algorithm for calculating the digits of e

- GitHub repository

- HDL project

- Mux address: 12

- Extra docs

- Clock: 350 Hz

- External hardware: 4 x 7447 decoders

#### How it works

This project implements a bounded spigot algorithm for calculating the digits (currently 31) of e. While there are many ways to calculate the digits of transcendental numbers like e or pi, this spigot algorithm has much lower memory requirements. It however only produces a single digit at a time, and the number of digits produced is precommited at the time of design. For calculating n digits, the algorithm needs at least (n+1) storage locations. Each digit requires (n+1) calculation steps, repeated (n-1) times producing (n-1) digits (first digit 2 is not counted). Each calculation step requires a constant multiply, an add and a divide with remainder. There are many optimizations needed to fit as many digits as possible into a 1x1 tile. The biggest contributor is the storage elements. Some quick modeling revealed that the storage elements need to be about as wide as log(n). The calculation step hardware is shared across all iterations. The intermediate results are never needed outside each calculation and are never stored in memory. The memory access is such that each location is read and written to before moving on to the next. The memory access pattern removes the need for address decoding, replaced with a massive ring of gated shift registers.

#### How to test

The digits are output on the bidirectional port and the output port in BCD (Binarycoded decimal). A BCD to seven segment decoder will be needed to display the digits. A clock below 500Hz should allow one to see the digits slide across the segment displays.

| # | Input | Output                 | Bidirectional          |

|---|-------|------------------------|------------------------|

| 0 | none  | digit_2[0]             | digit_0[0]             |

| 1 | none  | digit_21               | digit_01               |

| 2 | none  | digit_2 <mark>2</mark> | digit_02               |

| 3 | none  | digit_2[3]             | digit_0[3]             |

| 4 | none  | digit_3[0]             | digit_1[0]             |

| 5 | none  | digit_3 <mark>1</mark> | digit_1 <mark>1</mark> |

| 6 | none  | digit_3 <mark>2</mark> | digit_12               |

| 7 | none  | digit_3[3]             | digit_1[3]             |

### **Continued Fraction Calculator [13]**

- Author: Kevin You

- Description: Calculates the continued fraction of the square root of a natural number

- GitHub repository

- HDL project

- Mux address: 13

- Extra docs

- Clock: 0 Hz

- External hardware:

#### How it works

This continued fraction calculator computes the convergents in the standard manner. It computes the coefficients of the continued fraction, and then recursively computes the convergents. It turns out that when the target is the square of a natural number, one can avoid the need of comparisons or taking the floor (except on the first step) and only use addition, multiplication, and integer division. Still, squeezing the design in roughly 1000 cells proved quite difficult, and various simplifications were necessary (such as changing the output from 7-segment to binary).

This calculator, in conjunction with a mobile phone calculator, or paper and pencil, can be used to calculate the fundumental solution of Pell's equation  $x^2 - Dy^2 = 1$ . To do this, simply enter D, compute convergents, and verify whether the convergents satisfy Pell's equation  $P^2 - DQ^2 = 1$ . The first convergents that satisfy Pell's equation is the fundumental solution. This procedure combines the continued fraction calculator's ability to store various intermediate values and a mobile phone calculator's ability to calculate large numbers.

#### How to test

Enter 14 bit binary number D input via switches, press button 0 to generate the next convergents P and Q, where sqrt(D)  $\sim$  P/Q. Press button 1 to read through the values of P and Q in order of P[15:8], P[7:0], Q[15:8], Q[7:0].

| # | Input  | Output     | Bidirectional |

|---|--------|------------|---------------|

| 0 | button | status LED | switch        |

| 1 | button | status LED | switch        |

| 2 | switch | status LED | switch        |

| 3 | switch | status LED | switch        |

| 4 | switch | status LED | switch        |

| 5 | switch | status LED | switch        |

| 6 | switch | status LED | switch        |

| 7 | switch | status LED | switch        |

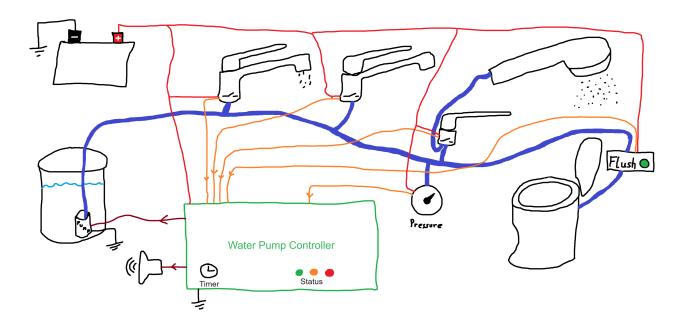

### Water Pump Controller [14]

- Author: Hendrik

- Description: Controller for a camping van water pump with multiple tap switches and timer

- GitHub repository

- Wokwi project

- Mux address: 14

- Extra docs

- Clock: 32768 Hz

- External hardware: 32768Hz clock (does not need to be prcise, actually), power on reset, controlled water supply system (tap switches, pump), optionally LEDs and Buzzer for controller states

#### How it works

The water pump controller is intended to replace the wiring based water pump system of typical camping vans with a bathroom and a kitchen and addresses some problems these systems can have.

In such a system, water taps are usually equipped with switches that signal the need for water as soon as the tap is slightly opened so that a pump can be activated to pressurize the pipes.

The controller has six inputs so that each tap (e.g sink in the kitchen, sink in the bathroom, toilet flushing, shower in bathroom, external shower) can use a dedicated

input. It has another input for a high pressure switch that would turn off the pump if the pressure rises when all taps are actually closed.

The main feature is a timer that can give an reminder using a buzzer when the water is running for an untypically long period and automatically switch off the pump at some point as well. When the switch off time was reached the buzzer signal can help to indicate which switch is still active.

#### How to test

For testing the circuit, the outputs (including the pump output) can be connected to LEDs or as in the test board to a 7-segment display. In the test board the pump output corresponds to the top segment. The inputs can be connected to DIP switches. The clock should be set to 32768 Hz ( $2^{15}$  Hz). The reset signal should provide a power-on reset and optionally a manual reset that might be handy for testing. In the minimal setup, the last three bidirectional I/O pins should be okay as well for a quick test. The pins can be outputs that should only be driven to low in this case, but do not connect them directly to VCC. The other I/O pins can be left open or connected to GND to avoid floating pins. The connection to GND can be done directly or via pull-down resistors to plan ahead for more tests with additional circuitry.

The first test is about enabling the pump while not making use of the timer:

- Keep the input 6 (DIP 7) low to disable the timer

- Keep the input 7 (high pressure switch) low

- Set any combination of tap switches (inputs 0 5) high

- The pump output (top segment) should be on

- The pump LED and ActiveNormal LED (right hand segments) should be on

- With all tap switches off all outputs should be off as well

The second test is to verify the high pressure switch:

- Set input 7 (the high pressure switch) high

- Set any combination of tap switches high

- Select any state for the timer enable pin (input 6)

- The pump output should be off

- The pump LED, ActiveLEDs and buzzer can be on, depending on the state of the controller

A simple test for the timer with default values:

- Set input 6 high to enable the timer feature

- Keep input 7 low to see the pump output

- Set any combination of tap switches (input 0 5) high

- Wait

- After 128s, the LEDs outputs should change from ActiveNormal to ActiveWarning (bottom right to bottom on the 7-segment display) and the RunLong LED (top left for 7-segment display) should be activated

- At the same time the buzzer should be activated every two seconds. LEDs would blink dim (center segment).

- After another 32s, the pump and pump LED should be turned off and the other LEDs should go from ActiveWarning to ActiveHalted (bottom to bottom left segment).

- The buzzer should emit a sequence corresponding to the first active tap input every 16 seconds. Again for LEDs that would be a dim blinking sequence every 16s.

- Set all tap switches to low

- All outputs should be off

- Activate any tap switch

- Pump (and related LEDs) should be on again, buzzer should be off

Testing the configuration feature requires additional external circuits. Please refer to the testing section of the README of the github project (https://github.com/fahek/water-pump-controller-tto5#more-advanced-tests).

| # | Input         | Output           | Bidirectional     |

|---|---------------|------------------|-------------------|

| 0 | TapA          | Pump             | CFG0              |

| 1 | TapB          | PumpEnabled      | CFG1              |

| 2 | TapC          | ActiveNormal     | CFG2              |

| 3 | TapD          | ActiveWarning    | CFG3              |

| 4 | TapE          | ActiveHalted     | CFG4              |

| 5 | TapF          | RunLong          | TimerScaleConfig  |

| 6 | EnableTimeout | Buzzer           | WarningTimeConfig |

| 7 | PressureHigh  | BuzzerHaltedOnly | TimeoutConfig     |

### **Event Denoising Circuit [15]**

- Author: Emily Lee

- Description: Implementing a Denoiser for Event Based Data in Silicon

- GitHub repository

- HDL project

- Mux address: 15

- Extra docs

- Clock: 10000000 Hz

- External hardware:

#### How it works

The 8 switches correspond to the tuple data input (L-R): Switches 1 & 2: Value of x (2 bits) Switches 3 & 4: Value of y '' Switches 5 & 6: Value of p '' Switches 7 & 8: Value of t ''

The denoiser is implemented as a debouncer. A high or low event will only be output if the data remains the same for 5 clock cycles. Due to white/thermal noise in an event camera, a cluster of coordinates that have no movement may incorectly spike high and the result would be a singular bright bit. The debouncing avoids this by first ensuring the event is consistent before outputting.

#### How to test

Switches (L-R) 5 & 6 corresponds to the input value of the polarity of the tuple. If a high event is wanted - switch 5 should be low and switch 6 should be high. If a low event is wanted = switch 5 must be low, and switch 6 must be low. This will cause the chip to output the debounced tuple corresponding to a high or low event.

| # | Input                                      | Output     | Bidirectional |

|---|--------------------------------------------|------------|---------------|

| 0 | bit 1 of x                                 | bit 1 of x | Unused        |

| 1 | bit 0 of x                                 | bit 0 of x | Unused        |

| 2 | bit 1 of y                                 | bit 1 of y | Unused        |

| 3 | bit 0 of y                                 | bit 0 of y | Unused        |

| 4 | bit 1 of p - no real use                   | bit 1 of p | Unused        |

| 5 | toggles event to be passed through if high | bit 0 of p | Unused        |

| # | Input      | Output     | Bidirectional |

|---|------------|------------|---------------|

| 6 | bit 1 of t | bit 1 of t | Unused        |

| 7 | bit 0 of t | bit 0 of t | Unused        |

# 7 segment seconds (Verilog Demo) [32]

- Author: Matt Venn, cloned by Cedric Honnet

- Description: Count up to 10, one second at a time.

- GitHub repository

- HDL project

- Mux address: 32

- Extra docs

- Clock: 10000000 Hz

- External hardware:

#### How it works

Uses a set of registers to divide the clock, and then some combinational logic to convert from binary to decimal for the display.

Puts the bottom 8 bits of the counter on the bidirectional outputs.

With all the inputs set to 0, the internal 24 bit compare is set to 10,000,000. This means the counter will increment by one each second.

If any inputs are non zero, then the input will be used as an bits 11 to 18 of the 24 bit compare register. Example: setting the inputs to 00010000 will program 16384 into the compare register. With a 10MHz clock the counter will increment  $\sim$ 610 times per second.

#### How to test

After reset, the counter should increase by one every second with a 10MHz input clock. Experiment by changing the inputs to change the counting speed.

| - |                |           |                      |

|---|----------------|-----------|----------------------|

| # | Input          | Output    | Bidirectional        |

| 0 | compare bit 11 | segment a | second counter bit 0 |

| 1 | compare bit 12 | segment b | second counter bit 1 |

| 2 | compare bit 13 | segment c | second counter bit 2 |

| 3 | compare bit 14 | segment d | second counter bit 3 |

| 4 | compare bit 15 | segment e | second counter bit 4 |

| 5 | compare bit 16 | segment f | second counter bit 5 |

| # | Input          | Output    | Bidirectional        |

|---|----------------|-----------|----------------------|

| 6 | compare bit 17 | segment g | second counter bit 6 |

| 7 | compare bit 18 | dot       | second counter bit 7 |

# Frequency Encoder/Decoder [33]

- Author: Hannah Cohen-Sandler

- Description: Encodes data into frequency variations and then decodes it back into its original form.

- GitHub repository

- HDL project

- Mux address: 33

- Extra docs

- Clock: 10000000 Hz

- External hardware:

## How it works

Utilizes an array of inputs and outputs to connect to switches, 7-segment displays, and enable bidirectional paths.

The bottom 7 bits of the second counter are linked to the bidirectional output.

The clock is generated using a Phase-Locked Loop.

The Frequency Encoder encodes data input from switches to a pulse output and uses the PLL output to enable the encoding operation.

The Frequency Decoder is connected to bidirectional inputs and decodes the pulse signal based on the PLL output, resulting in a data output.

## How to test

Confirm that the system begins in a reset state with rst\_n set to 0. Transition the system out of reset by setting rst\_n to 1. Set the constant current input signal (ui\_in) to a specific value to simulate different input scenarios. Activate the chip design by setting the ena signal to 1. Alter the clk clock signal frequency value and observe how the changes affect the design's behavior. Experiment with various inputs, clock frequencies, and enabling/disabling operations verify the design and accuracy of the encoding, decoding, and pulse counting.

| # Input Output Bidirectional | Input Out | put Bidirectional |  |

|------------------------------|-----------|-------------------|--|

|------------------------------|-----------|-------------------|--|

| # | Input          | Output    | Bidirectional        |

|---|----------------|-----------|----------------------|

| 0 | current bit 11 | segment a | second counter bit 0 |

| 1 | current bit 12 | segment b | second counter bit 1 |

| 2 | current bit 13 | segment c | second counter bit 2 |

| 3 | current bit 14 | segment d | second counter bit 3 |

| 4 | current bit 15 | segment e | second counter bit 4 |

| 5 | current bit 16 | segment f | second counter bit 5 |

| 6 | current bit 17 | segment g | second counter bit 6 |

| 7 | current bit 18 | segment h | second counter bit 7 |

# **UART** Greeter with RNN Module [34]

- Author: Jonathan Zentgraf

- Description: Sends 'Hello' over UART and fills die space with metastability

- GitHub repository

- Wokwi project

- Mux address: 34

- Extra docs

- Clock: 0 Hz

- External hardware:

### How it works

The UART transmitter is just a shift register with hardcoded initial values. The output of the shift register is fed back into itself in an infinite loop. The "RNN" is a few flip-flops feeding into each other to use up die space. :)

### How to test

Testing UART is simple:

- 1. Connect the UART output to a microcontroller or scope.

- 2. Set load/enable low (load).

- 3. Set output enable high.

- 4. Set load/enable high (enable).

- 5. Observe as the string "Hellon" is sent over UART.

The RNN module is trained on random Wokwi wiring, and might be smarter than a single human neuron. It probably detects something we mortals cannot comprehend, and is tied to inputs 0-3 and outputs 0-3. It may be fun to drive these with a very fast clock.

| # | Input       | Output       | Bidirectional |

|---|-------------|--------------|---------------|

| 0 | RNN input 0 | RNN output 0 | none          |

| 1 | RNN input 1 | RNN output 1 | none          |

| 2 | RNN input 2 | RNN output 2 | none          |

| 3 | RNN input 3 | RNN output 3 | none          |

| # | Input                                     | Output              | Bidirectional |

|---|-------------------------------------------|---------------------|---------------|

| 4 | none                                      | none                | none          |

| 5 | none                                      | none                | none          |

| 6 | Shift register load (low) / enable (high) | UART output enabled | none          |

| 7 | UART output enable                        | UART output         | none          |

# WS2812B LED strip driver [35]

- Author: Ciro Cattuto

- Description: Drives a WS2812B LED strip with random colors for each refresh

- GitHub repository

- Wokwi project

- Mux address: 35

- Extra docs

- Clock: 2000000 Hz

- External hardware: WS2812B strip of arbitrary lengthd

### How it works

This project drives a strip of WS2812B RGB LEDs, periodically updating the strip with random color values. The project consists of three main modules:

- a linear feedback 16-bit shift register to generate a stream of pseudo-random bits

- a 5-bit synchronous increasing counter, wrapping to 0 when the counter reaches 25. WHen driven by a 20 MHz clock source, the counter generates the 1.25 us pulses required by the WS2812B protocol. The duration of the high phase of the pulse is controlled by the random bit stream generated above.

- a 16-bit ripple counter increasing at the end of each pulse, used to divide the pulse frequency and generate the LED strip refresh signal

### How to test

Set the clock frequency to 20 MHz and connect OUT2 to the DIN signal of a WS2812B LED strip. Optionally connect to IN6 the DOUT signal of the last LED of the strip. Press and release the reset button. The strip should light up with random colors, updating at a frequency controllable using the SW3 and SW4 switches.

| # | Input                   | Output                  | Bidirectional |

|---|-------------------------|-------------------------|---------------|

| 0 | clock source selection  | shift register output   | none          |

| 1 | external clock source   | shift register clock    | none          |

| 2 | refresh freq sel (low)  | WS2812B LED strip input | none          |

| 3 | refresh freq sel (high) | LED strip overflow      | none          |

| # | Input                    | Output            | Bidirectional |

|---|--------------------------|-------------------|---------------|

| 4 | none                     | LED strip refresh | none          |

| 5 | none                     | none              | none          |

| 6 | WS2812B LED strip output | none              | none          |

| 7 | shift register input     | none              | none          |

# Tiny Tapeout 5 Workshop [36]

- Author: Rob Campbell KG6HUM

- Description: Tiny Tapeout 5 Workshop

- GitHub repository

- Wokwi project

- Mux address: 36

- Extra docs

- Clock: 0 Hz

- External hardware:

### How it works

First 3 output bits are a binary counter. Can be preset with first 3 input bits. Other input bits pass through to the output.

#### How to test

Explain how to test your project

| # | Input | Output    | Bidirectional |

|---|-------|-----------|---------------|

| 0 | none  | segment a | none          |

| 1 | none  | segment b | none          |

| 2 | none  | segment c | none          |

| 3 | none  | segment d | none          |

| 4 | none  | segment e | none          |

| 5 | none  | segment f | none          |

| 6 | none  | segment g | none          |

| 7 | none  | dot       | none          |

# Tiny Tapeout 1 [37]

- Author: James Bryant

- Description: A description

- GitHub repository

- Wokwi project

- Mux address: 37

- Extra docs

- Clock: 0 Hz

- External hardware:

## How it works

Explain how your project works

#### How to test

Explain how to test your project

| # | Input | Output    | Bidirectional |

|---|-------|-----------|---------------|

| 0 | none  | segment a | none          |

| 1 | none  | segment b | none          |

| 2 | none  | segment c | none          |

| 3 | none  | segment d | none          |

| 4 | none  | segment e | none          |

| 5 | none  | segment f | none          |

| 6 | none  | segment g | none          |

| 7 | none  | dot       | none          |

# Supercon Workshop [38]

- Author: Caleb Hensley

- Description: Example of logic gates: AND, NAND, OR, XOR

- GitHub repository

- Wokwi project

- Mux address: 38

- Extra docs

- Clock: 0 Hz

- External hardware:

### How it works

Input 0 and 1 input to an AND gate and output to output 0. Input 2 and 3 input to a NAND gate and output to output 1. Input 4 and 5 input to a OR gate and output to output 2. Input 6 and 7 input to a XOR gate and output to output 3.

#### How to test

Explain how to test your project

| # | Input | Output    | Bidirectional |

|---|-------|-----------|---------------|

| 0 | none  | segment a | none          |

| 1 | none  | segment b | none          |

| 2 | none  | segment c | none          |

| 3 | none  | segment d | none          |

| 4 | none  | segment e | none          |

| 5 | none  | segment f | none          |

| 6 | none  | segment g | none          |

| 7 | none  | dot       | none          |

# Matrix Multiplier [39]

- Author: Erik Mercado

- Description: Multiple Matrices.

- GitHub repository

- HDL project

- Mux address: 39

- Extra docs

- Clock: 10000000 Hz

- External hardware:

### How it works

tt\_um\_matrix\_multiplier:

This module performs a multiplication of two 2x2 matrices, where each element is an unsigned 2-bit number. The matrices are input via 8-bit wires (ui\_in and uio\_in), where every 2 bits represent an element. Error checking is done to ensure that each element is within the range [0, 2]. If there's an error, the output is set to zero; otherwise, the multiplication result is returned via uo\_out and uio\_out. The module also provides a uio\_oe output signal that serves as an output enable for the resultant matrix.

tb (testbench):

This is the simulation testbench for the tt\_um\_matrix\_multiplier module. It toggles a clock signal, initializes input values, and instantiates the tt\_um\_matrix\_multiplier. The testbench is set up to generate VCD files, allowing for waveform viewing using tools like GTKWave.

test.py:

This Python script uses the cocotb framework to test the matrix multiplication functionality. Helper functions are provided to convert 2x2 matrices to binary representations and vice-versa. A list of test matrices and expected results is present. For each test case, the script inputs matrices, waits for the multiplication result, and checks against the expected result. The test concludes by logging a success message if all test cases pass.

### How to test

Synthesize and Implement: Use an FPGA toolchain to synthesize the Verilog code and implement it on a suitable FPGA. Simulation: Use a simulator compatible with

Verilog (like ModelSim or Icarus Verilog) to run the testbench (tb.v). You can view the generated VCD file with a tool like GTKWave to visualize the waveform.

Cocotb Test: Setup the cocotb environment and necessary dependencies. Use the test.py script to run the cocotb test. Monitor the test output to ensure that all matrix tests pass.

| # | Input          | Output    | Bidirectional        |

|---|----------------|-----------|----------------------|

| 0 | compare bit 11 | segment a | second counter bit 0 |

| 1 | compare bit 12 | segment b | second counter bit 1 |

| 2 | compare bit 13 | segment c | second counter bit 2 |

| 3 | compare bit 14 | segment d | second counter bit 3 |

| 4 | compare bit 15 | segment e | second counter bit 4 |

| 5 | compare bit 16 | segment f | second counter bit 5 |

| 6 | compare bit 17 | segment g | second counter bit 6 |

| 7 | compare bit 18 | dot       | second counter bit 7 |

# Clock Divider [40]

- Author: Joey Castillo

- Description: Divides the clock input eight times, with CLK/2 on OUT7, CLK/4 on OUT6, etc.

- GitHub repository

- Wokwi project

- Mux address: 40

- Extra docs

- Clock: 0 Hz

- External hardware:

### How it works

Explain how your project works

### How to test

Explain how to test your project

| # | Input | Output  | Bidirectional |

|---|-------|---------|---------------|

| 0 | none  | CLK/256 | none          |

| 1 | none  | CLK/128 | none          |

| 2 | none  | CLK/64  | none          |

| 3 | none  | CLK/32  | none          |

| 4 | none  | CLK/16  | none          |

| 5 | none  | CLK/8   | none          |

| 6 | none  | CLK/4   | none          |

| 7 | none  | CLK/2   | none          |

# Binary Counter [41]

- Author: Chinchilla

- Description: The Just Kidding flip flop has been changed to a binary counter

- GitHub repository

- Wokwi project

- Mux address: 41

- Extra docs

- Clock: 10 Hz

- External hardware: none

### How it works

It didn't last time (3). Counts. With 1 and 0.

#### How to test

turn on.

| # | Input | Output    | Bidirectional |

|---|-------|-----------|---------------|

| 0 | none  | segment a | none          |

| 1 | none  | segment b | none          |

| 2 | none  | segment c | none          |

| 3 | none  | segment d | none          |

| 4 | none  | segment e | none          |

| 5 | none  | segment f | none          |

| 6 | none  | segment g | none          |

| 7 | none  | dot       | none          |

# ring osc test [42]

- Author: Bob Poekert

- Description: simple ring oscillator

- GitHub repository

- Wokwi project

- Mux address: 42

- Extra docs

- Clock: 0 Hz

- External hardware:

### How it works

This outputs a square wave at... some frequency on pins 0-3, where the pins are phase shifted by... some frequency.

#### How to test

Just apply power.

| # | Input | Output    | Bidirectional |

|---|-------|-----------|---------------|

| 0 | none  | segment a | none          |

| 1 | none  | segment b | none          |

| 2 | none  | segment c | none          |

| 3 | none  | segment d | none          |

| 4 | none  | segment e | none          |

| 5 | none  | segment f | none          |

| 6 | none  | segment g | none          |

| 7 | none  | dot       | none          |

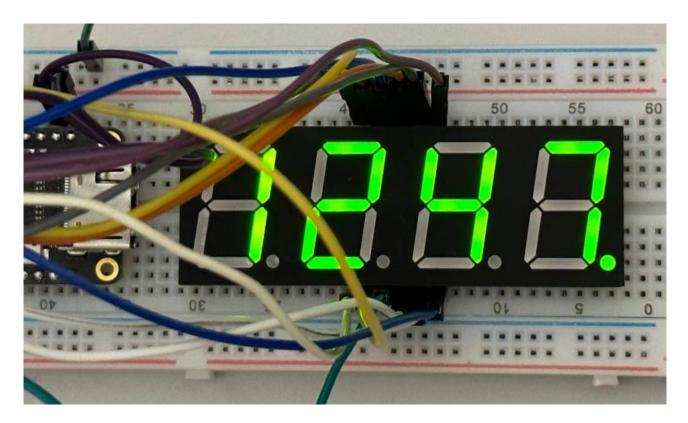

# 7 segment clock with 4 digits [43]

- Author: Kumar Abhishek

- Description: Multi mode clock.

- GitHub repository

- HDL project

- Mux address: 43

- Extra docs

- Clock: 10000000 Hz

- External hardware:

### How it works

Uses a set of registers to divide the clock, and then some combinational logic to convert from binary to decimal for the display.

Puts the bottom 8 bits of the counter on the bidirectional outputs.

With all the inputs set to 0, the internal 24 bit compare is set to 10,000,000. This means the counter will increment by one each second.

If any inputs are non zero, then the input will be used as an bits 11 to 18 of the 24 bit compare register. Example: setting the inputs to 00010000 will program 16384 into the compare register. With a 10MHz clock the counter will increment  $\sim$ 610 times per second.

### How to test

After reset, the counter should increase by one every second with a 10MHz input clock. Experiment by changing the inputs to change the counting speed.

| #InputOutputBidirectional0compare bit 11segment asecond counter bit1compare bit 12segment bsecond counter bit2compare bit 13segment csecond counter bit |   |                |           |                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------|-----------|----------------------|

| <ol> <li>compare bit 12 segment b second counter bit</li> <li>compare bit 13 segment c second counter bit</li> </ol>                                    | # | Input          | Output    | Bidirectional        |

| 2 compare bit 13 segment c second counter bit                                                                                                           | 0 | compare bit 11 | segment a | second counter bit 0 |

|                                                                                                                                                         | 1 | compare bit 12 | segment b | second counter bit 1 |

|                                                                                                                                                         | 2 | compare bit 13 | segment c | second counter bit 2 |

| 3 compare bit 14 segment d second counter bit                                                                                                           | 3 | compare bit 14 | segment d | second counter bit 3 |

| 4 compare bit 15 segment e second counter bit                                                                                                           | 4 | compare bit 15 | segment e | second counter bit 4 |

| 5 compare bit 16 segment f second counter bit                                                                                                           | 5 | compare bit 16 | segment f | second counter bit 5 |

| # | Input          | Output    | Bidirectional        |

|---|----------------|-----------|----------------------|

| 6 | compare bit 17 | segment g | second counter bit 6 |

| 7 | compare bit 18 | dot       | second counter bit 7 |

# test001 [44]

- Author: dmitry

- Description: Just a Test Tiny TapeOut

- GitHub repository

- Wokwi project

- Mux address: 44

- Extra docs

- Clock: 0 Hz

- External hardware:

## How it works

Explain how your project works

#### How to test

Explain how to test your project

| # | Input | Output    | Bidirectional |

|---|-------|-----------|---------------|

| 0 | none  | segment a | none          |

| 1 | none  | segment b | none          |

| 2 | none  | segment c | none          |

| 3 | none  | segment d | none          |

| 4 | none  | segment e | none          |

| 5 | none  | segment f | none          |

| 6 | none  | segment g | none          |

| 7 | none  | dot       | none          |

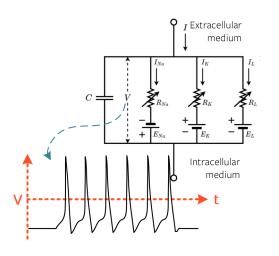

# Hodgkin-Huxley Chip Design [45]

- Author: Ethan Mulle

- Description: Implements the Hodgkin-Huxley model

- GitHub repository

- HDL project

- Mux address: 45

- Extra docs

- Clock: 10000000 Hz

- External hardware:

### How it works

Uses a set of registers to divide the clock, and then some combinational logic to convert from binary to decimal for the display.

Puts the bottom 8 bits of the counter on the bidirectional outputs.

With all the inputs set to 0, the internal 24 bit compare is set to 10,000,000. This means the counter will increment by one each second.

If any inputs are non zero, then the input will be used as an bits 11 to 18 of the 24 bit compare register. Example: setting the inputs to 00010000 will program 16384 into the compare register. With a 10MHz clock the counter will increment  $\sim$ 610 times per second.

### How to test

After reset, the counter should increase by one every second with a 10MHz input clock. Experiment by changing the inputs to change the counting speed.

| #InputOutputBidirectional0compare bit 11segment asecond counter bit1compare bit 12segment bsecond counter bit2compare bit 13segment csecond counter bit |   |                |           |                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------|-----------|----------------------|

| <ol> <li>compare bit 12 segment b second counter bit</li> <li>compare bit 13 segment c second counter bit</li> </ol>                                    | # | Input          | Output    | Bidirectional        |

| 2 compare bit 13 segment c second counter bit                                                                                                           | 0 | compare bit 11 | segment a | second counter bit 0 |

|                                                                                                                                                         | 1 | compare bit 12 | segment b | second counter bit 1 |

|                                                                                                                                                         | 2 | compare bit 13 | segment c | second counter bit 2 |

| 3 compare bit 14 segment d second counter bit                                                                                                           | 3 | compare bit 14 | segment d | second counter bit 3 |

| 4 compare bit 15 segment e second counter bit                                                                                                           | 4 | compare bit 15 | segment e | second counter bit 4 |

| 5 compare bit 16 segment f second counter bit                                                                                                           | 5 | compare bit 16 | segment f | second counter bit 5 |

| # | Input          | Output    | Bidirectional        |

|---|----------------|-----------|----------------------|

| 6 | compare bit 17 | segment g | second counter bit 6 |

| 7 | compare bit 18 | dot       | second counter bit 7 |

## Character Selector [46]

- Author: Dakota W Winslow

- Description: A circuit to output latin characters on a 7-segment display

- GitHub repository

- Wokwi project

- Mux address: 46

- Extra docs

- Clock: 1000 Hz

- External hardware:

#### How it works

This project displays a user-selctable character on the 7-segment display. Input DIPs 1-6 are used to select the character to display. Inputs 7 and 8 are not connected. The display is driven one segment at a time, so a high clock rate is required to see thew character. Characters are a mix of upper and lower case, preferring whichever is more recognizable. See the wikipedia page on 7-segment display representations for reference [https://en.wikipedia.org/wiki/Seven-segment\_display\_character\_representations].

### How to test

Connect the clock line to the ocillator (or press the clock button REALLY fast). Then, use thew DIP switches to enter a 6-digit binary number corresponding to the character to be displayed. 0-25 for a-z, then 26:[space], 27:[\_], 28:[-], 29:[.], 30:[!], 31:["]. If only one segment is displayed, make sure your clock is set properly!

| # | Input         | Output    | Bidirectional |

|---|---------------|-----------|---------------|

| 0 | dip0          | segment a | none          |

| 1 | dip1          | segment b | none          |

| 2 | dip2          | segment c | none          |

| 3 | dip3          | segment d | none          |

| 4 | dip4          | segment e | none          |

| 5 | dip5          | segment f | none          |

| 6 | not connected | segment g | none          |

| 7 | not connected | dot       | none          |

## Intructouction to PRBS [47]

- Author: Chih-Kuan Ho and David Parent

- Description: This is a simple design used to verify the design flow, so that we can teach lower division college studdnts IC desgin.

- GitHub repository

- Wokwi project

- Mux address: 47

- Extra docs

- Clock: 10k Hz

- External hardware:

### How it works

This takes a 4 bit LSFR confugred as a PRBS= $X^{3+X}2+1$  Reset sets four DFF to zero to make sure the osiclation starts. This uses XNOR because there was a synth warning The outpus are for a 7 segment displant and the last out put is for the PRBS

### How to test

Set the clock, pulse reser and it it should givne RBS stream.

| # | Input | Output       | Bidirectional |

|---|-------|--------------|---------------|

| 0 | Clock | segment a    | none          |

| 1 | Reset | segment b    | none          |

| 2 | none  | segment c    | none          |

| 3 | none  | segment d    | none          |

| 4 | none  | segment e    | none          |

| 5 | none  | segment f    | none          |

| 6 | none  | segment g    | none          |

| 7 | none  | segment PRBS | none          |

|   |       |              |               |

# tto5 Supercon Project [64]

- Author: Ryan Young

- Description: quick full adder design

- GitHub repository

- Wokwi project

- Mux address: 64

- Extra docs

- Clock: 0 Hz

- External hardware:

## How it works

Explain how your project works

#### How to test

Explain how to test your project

| # | Input | Output    | Bidirectional |

|---|-------|-----------|---------------|

| 0 | none  | segment a | none          |

| 1 | none  | segment b | none          |

| 2 | none  | segment c | none          |

| 3 | none  | segment d | none          |

| 4 | none  | segment e | none          |

| 5 | none  | segment f | none          |

| 6 | none  | segment g | none          |

| 7 | none  | dot       | none          |

# Delta Modulation Spike Encoding [65]

- Author: John Madden

- Description: Delta Modulation for Spiking Neural Networks (SNN) based on snnTorch's implementation.

- GitHub repository

- HDL project

- Mux address: 65

- Extra docs

- Clock: 10000000 Hz

- External hardware:

## How it works