# **Tiny Tapeout 6 Datasheet**

Project Repository https://github.com/TinyTapeout/tinytapeout-06

February 23, 2025

Contents

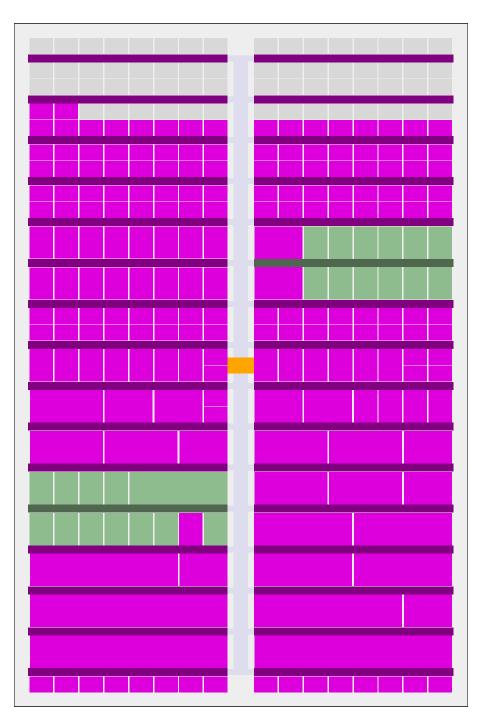

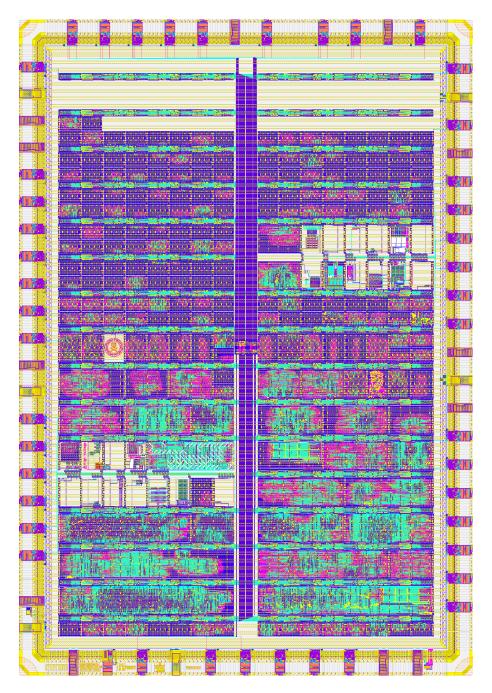

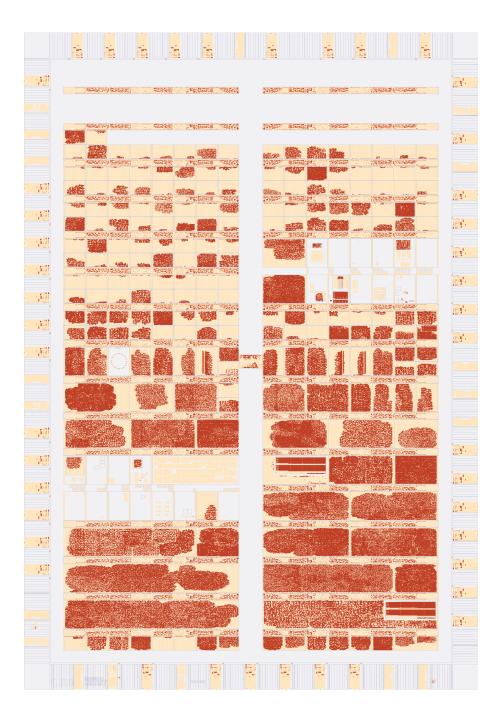

### Chip map

| Chip ROM [0]       11         TinyTapeout 06 Factory Test [1]       13         UCSC HW Systems Collective, TDC [2]       14         Most minimal extension of friend's 'CPU In a Week' in a day [4]       15         SPDIF to I2S decoder [6]       18         Chisel Pong [8]       21         8080 CPU [12]       22         Tiny Zuse [14]       23         7-segment-FUN [32]       27         Asynchronous Down Counter [33]       28         Synthesized Time-to-Digital Converter (TDC) [35]       29         luckyCube [37]       31         playwithnumbers [39]       32         2 Player Game [41]       33         Oscillating Bones [42]       34         drops [43]       37         Flappy Bird [45]       39         4-Bit CPU mit FSM [47]       41         FP4 x 8-bit matrix multiplier [64]       42 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UCSC HW Systems Collective, TDC [2]       14         Most minimal extension of friend's 'CPU In a Week' in a day [4]       15         SPDIF to I2S decoder [6]       18         Chisel Pong [8]       21         8080 CPU [12]       22         Tiny Zuse [14]       23         7-segment-FUN [32]       27         Asynchronous Down Counter [33]       28         Synthesized Time-to-Digital Converter (TDC) [35]       29         luckyCube [37]       31         playwithnumbers [39]       32         2 Player Game [41]       33         Oscillating Bones [42]       34         drops [43]       37         Flappy Bird [45]       39         4-Bit CPU mit FSM [47]       41                                                                                                                                    |

| Most minimal extension of friend's 'CPU In a Week' in a day [4]       15         SPDIF to I2S decoder [6]       18         Chisel Pong [8]       21         8080 CPU [12]       22         Tiny Zuse [14]       23         7-segment-FUN [32]       27         Asynchronous Down Counter [33]       28         Synthesized Time-to-Digital Converter (TDC) [35]       29         luckyCube [37]       31         playwithnumbers [39]       32         2 Player Game [41]       33         Oscillating Bones [42]       34         drops [43]       37         Flappy Bird [45]       39         4-Bit CPU mit FSM [47]       41                                                                                                                                                                                         |

| Most minimal extension of friend's 'CPU In a Week' in a day [4]       15         SPDIF to I2S decoder [6]       18         Chisel Pong [8]       21         8080 CPU [12]       22         Tiny Zuse [14]       23         7-segment-FUN [32]       27         Asynchronous Down Counter [33]       28         Synthesized Time-to-Digital Converter (TDC) [35]       29         luckyCube [37]       31         playwithnumbers [39]       32         2 Player Game [41]       33         Oscillating Bones [42]       34         drops [43]       37         Flappy Bird [45]       39         4-Bit CPU mit FSM [47]       41                                                                                                                                                                                         |

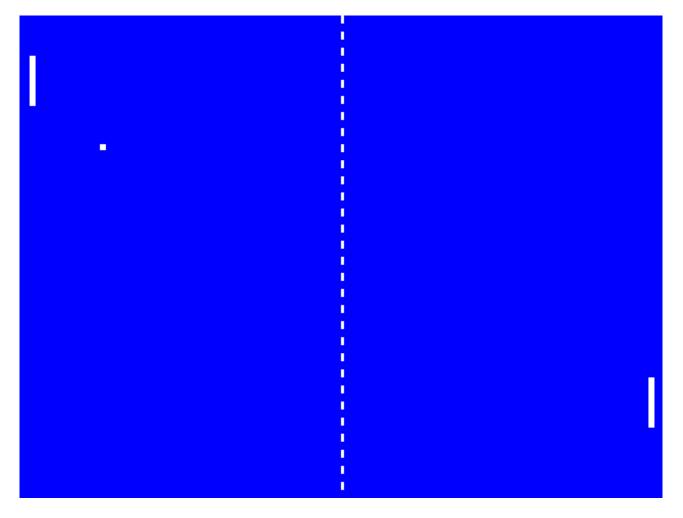

| Chisel Pong [8]       21         8080 CPU [12]       22         Tiny Zuse [14]       23         7-segment-FUN [32]       27         Asynchronous Down Counter [33]       28         Synthesized Time-to-Digital Converter (TDC) [35]       29         luckyCube [37]       31         playwithnumbers [39]       32         2 Player Game [41]       33         Oscillating Bones [42]       34         drops [43]       37         Flappy Bird [45]       39         4-Bit CPU mit FSM [47]       41                                                                                                                                                                                                                                                                                                                    |

| 8080 CPU [12]       22         Tiny Zuse [14]       23         7-segment-FUN [32]       27         Asynchronous Down Counter [33]       28         Synthesized Time-to-Digital Converter (TDC) [35]       29         luckyCube [37]       31         playwithnumbers [39]       32         2 Player Game [41]       33         Oscillating Bones [42]       34         drops [43]       37         Flappy Bird [45]       39         4-Bit CPU mit FSM [47]       41                                                                                                                                                                                                                                                                                                                                                     |

| Tiny Zuse [14]       23         7-segment-FUN [32]       27         Asynchronous Down Counter [33]       28         Synthesized Time-to-Digital Converter (TDC) [35]       29         luckyCube [37]       31         playwithnumbers [39]       32         2 Player Game [41]       33         Oscillating Bones [42]       34         drops [43]       37         Flappy Bird [45]       39         4-Bit CPU mit FSM [47]       41                                                                                                                                                                                                                                                                                                                                                                                    |

| 7-segment-FUN [32]       27         Asynchronous Down Counter [33]       28         Synthesized Time-to-Digital Converter (TDC) [35]       29         luckyCube [37]       31         playwithnumbers [39]       32         2 Player Game [41]       33         Oscillating Bones [42]       34         drops [43]       37         Flappy Bird [45]       39         4-Bit CPU mit FSM [47]       41                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Asynchronous Down Counter [33]       28         Synthesized Time-to-Digital Converter (TDC) [35]       29         luckyCube [37]       31         playwithnumbers [39]       32         2 Player Game [41]       33         Oscillating Bones [42]       34         drops [43]       37         Flappy Bird [45]       39         4-Bit CPU mit FSM [47]       41                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Asynchronous Down Counter [33]       28         Synthesized Time-to-Digital Converter (TDC) [35]       29         luckyCube [37]       31         playwithnumbers [39]       32         2 Player Game [41]       33         Oscillating Bones [42]       34         drops [43]       37         Flappy Bird [45]       39         4-Bit CPU mit FSM [47]       41                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Synthesized Time-to-Digital Converter (TDC) [35]       29         luckyCube [37]       31         playwithnumbers [39]       32         2 Player Game [41]       33         Oscillating Bones [42]       34         drops [43]       37         Flappy Bird [45]       39         4-Bit CPU mit FSM [47]       41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| luckyCube [37]       31         playwithnumbers [39]       32         2 Player Game [41]       33         Oscillating Bones [42]       33         drops [43]       37         Flappy Bird [45]       39         4-Bit CPU mit FSM [47]       41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| playwithnumbers [39]       32         2 Player Game [41]       33         Oscillating Bones [42]       34         drops [43]       37         Flappy Bird [45]       39         4-Bit CPU mit FSM [47]       41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2 Player Game [41]       33         Oscillating Bones [42]       34         drops [43]       37         Flappy Bird [45]       39         4-Bit CPU mit FSM [47]       41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Oscillating Bones [42]       34         drops [43]       37         Flappy Bird [45]       39         4-Bit CPU mit FSM [47]       41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| drops [43]       37         Flappy Bird [45]       39         4-Bit CPU mit FSM [47]       41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Flappy Bird [45]       39         4-Bit CPU mit FSM [47]       41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4-Bit CPU mit FSM [47]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CORA-16 [66]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| kstep [68]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| UCSC HW Systems Collective, TDC - BUF2x1 [70]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| UCSC HW Systems Collective, TDC - MUX2x1 [72]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

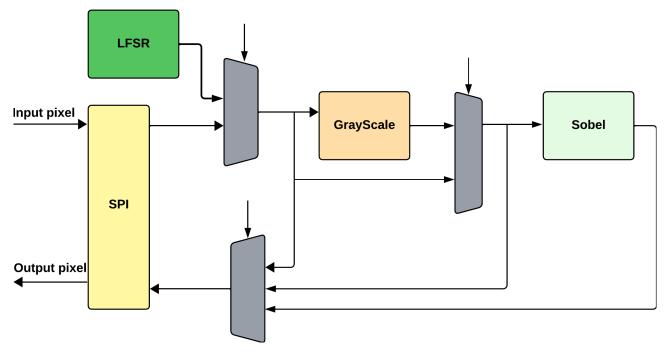

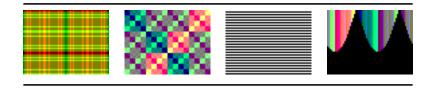

| Gray scale and Sobel filter [74]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RGB Mixer demo [76]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Projekt KEIS Hadner Thomas [78]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

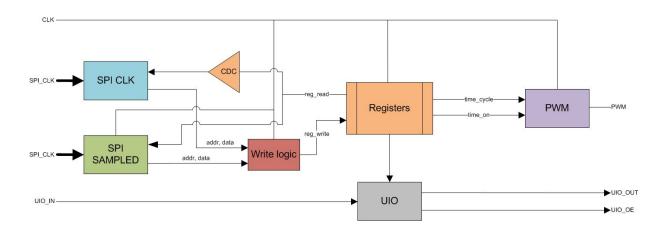

| spi_pwm [97]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| PiMAC [99]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| PILIPINAS [101]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| GOA - grogu on ASIC [103]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TTRPG Dice + simple I2C peripheral [105]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| i4004 for TinyTapeout [107]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Moving average filter [108]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Synthesized Time-to-Digital Converter (TDC) v2 [109]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

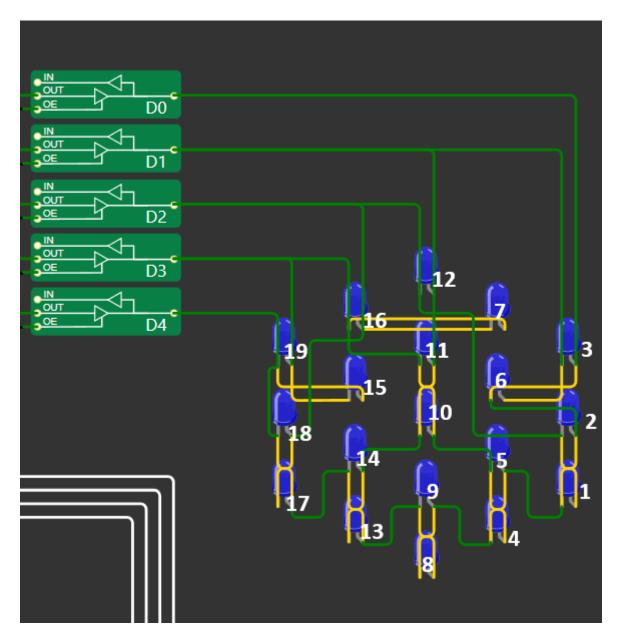

| SPI to RGBLED Decoder/Driver [110]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 8-bit CPU with Debugger (Lite) [111]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| FIR Filter with adaptable coefficients [128]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Karplus-Strong String Synthesis [132]    90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ADPCM Encoder Audio Compressor [136]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Ternary 1.58-bit x 8-bit matrix multiplier [142]                     |     | 94  |

|----------------------------------------------------------------------|-----|-----|

| 32-Bit Fibonacci Linear Feedback Shift Register [160]                |     |     |

| Some_LEDs [161]                                                      |     |     |

| RGB Mixer [162]                                                      |     |     |

| Workshop Hackaday Juli [163]                                         |     |     |

| Animated 7-segment character display [164]                           |     |     |

| Keypad Decoder [165]                                                 |     | 103 |

| Tiny 8-bit CPU [166]                                                 |     | 105 |

| NOT WORKING HP 5082-7500 Decoder [167]                               |     |     |

| LED PWM controller [168]                                             |     |     |

| 8-Bit CPU In a Week [169]                                            |     |     |

| Clock Domain Crossing FIFO [170]                                     |     |     |

| Frequency to digital converters (asynchronous and synchronous) [171] |     |     |

| Die Roller [172]                                                     |     | 118 |

| 4-bit Stochastic Multiplier Compact with Stochastic Resonator [173]  |     | 119 |

| ASG [174]                                                            |     |     |

| Silly 4b CPU v2 [175]                                                |     |     |

| ANS Encoder/Decoder [194]                                            |     |     |

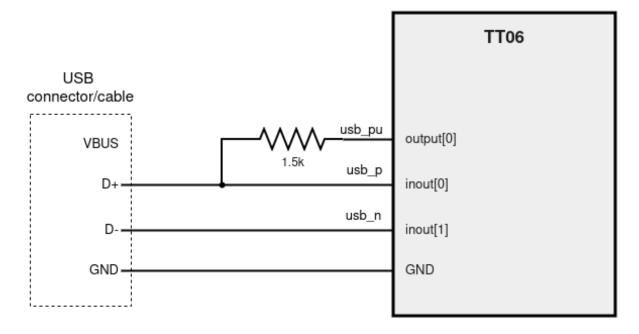

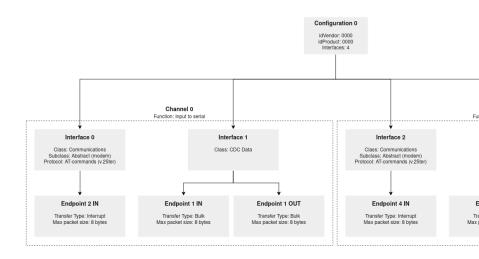

| Two ports USB CDC device [198]                                       |     |     |

| Snake Game [200]                                                     |     |     |

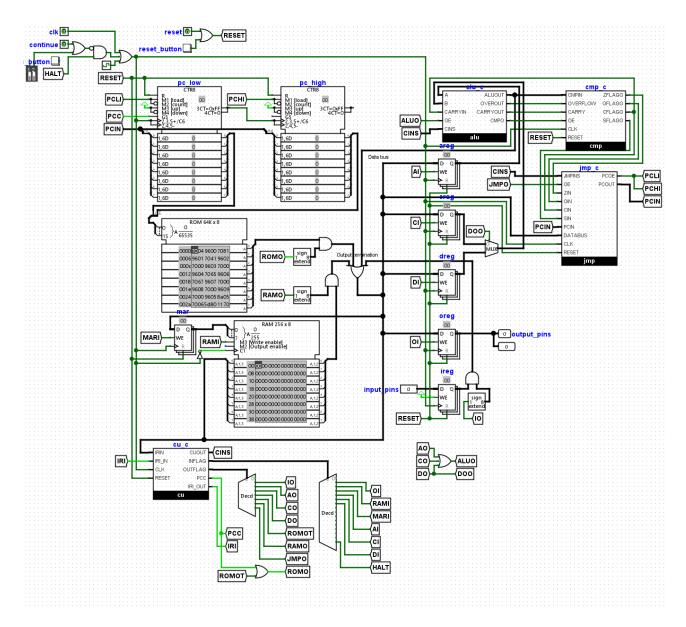

| 8-bit CPU with Debugger [202]                                        |     |     |

| The James Retro Byte 8 computer [204]                                |     |     |

| co processor for precision farming [206]                             |     |     |

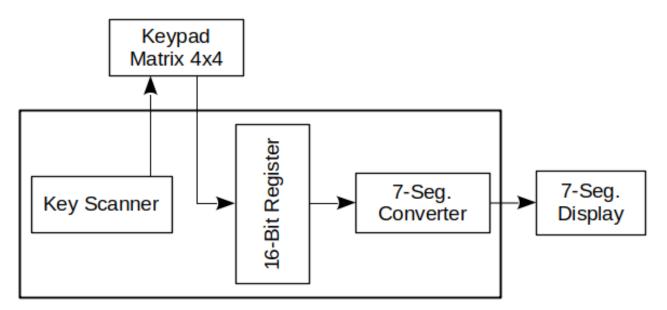

| Keypad controller [224]                                              |     |     |

| multimac [226]                                                       |     |     |

| TinyQV Risc-V SoC [227]                                              |     |     |

| 10-bit Linear feedback shift register [228]                          |     |     |

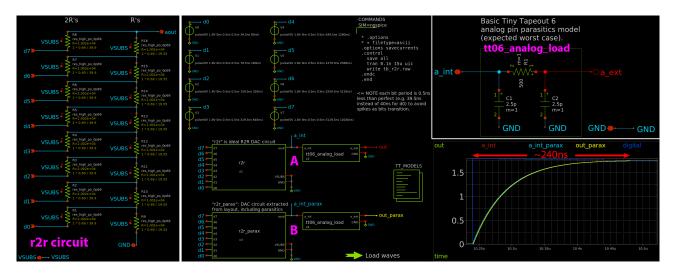

| Analog 8bit R2R DAC [229]                                            |     |     |

| Pulse Width Modulation [230]                                         |     |     |

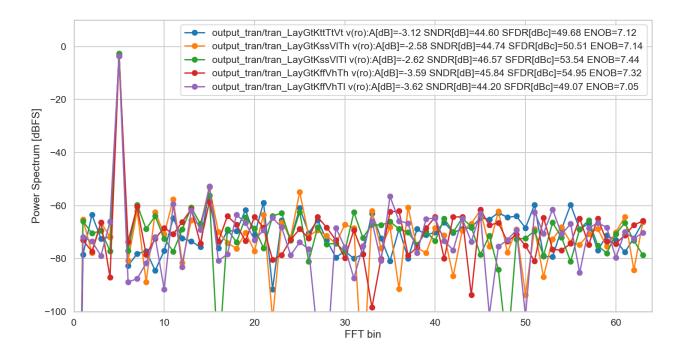

| TT06 8-bit SAR ADC [231]                                             |     |     |

| 4-bit stochastic multiplier traditional [232]                        |     |     |

| VCII [233]                                                           |     |     |

| 8 Bit Digital QIF [234]                                              |     |     |

| Programmable Thing [235]                                             |     |     |

| easy PAL [236]                                                       |     |     |

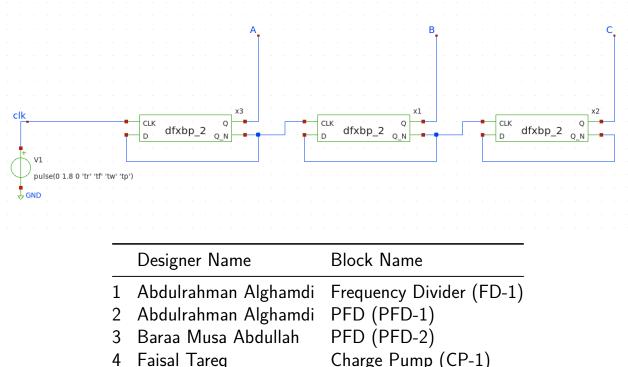

| PLL blocks [237]                                                     |     |     |

| Rule 30 Engine!         [238]                                        |     |     |

| TT06 Analog Factory Test [239]                                       |     |     |

| tt06-RV32E_MinMCU [258]                                              |     |     |

| Crossbar Array [263]                                                 |     |     |

| TinyRV1 CPU [264]                                                    |     |     |

| WoWA [265]                                                           |     |     |

|                                                                      | • • | 197 |

| A 555-Timer Clone for Tiny Tapeout 6 [267]                | 202 |

|-----------------------------------------------------------|-----|

| Dickson Charge Pump [269]                                 | 204 |

| Neurocore [270]                                           |     |

| Tiny Opamp [271]                                          | 210 |

| test for tiny tapeout hackaday [288]                      | 212 |

| Triple Watchdog [289]                                     | 213 |

| 1-Bit ALU 2 [290]                                         | 215 |

| Minibyte CPU [291]                                        | 216 |

| Bestagon LED matrix driver [292]                          |     |

| My Chip [293]                                             | 230 |

| 8-bit PRNG [294]                                          | 231 |

| Tiny Shader [295]                                         |     |

| Workshop_chip [296]                                       |     |

| PCKY's Successive Approximation Game [297]                | 239 |

| Dice [298]                                                | 241 |

| Display test 1 [299]                                      | 242 |

| First TT Project [300]                                    | 243 |

| Tiny_Tapeout_6_Frank [301]                                | 244 |

| Hack a day Tiny Tapeout project [302]                     |     |

| Simple NCO [303]                                          |     |

| SiliconJackets_Systolic_Array [324]                       |     |

| ChatGPT designed Recurrent Spiking Neural Network [330]   | 249 |

| Izhikevich Neuron [334]                                   | 253 |

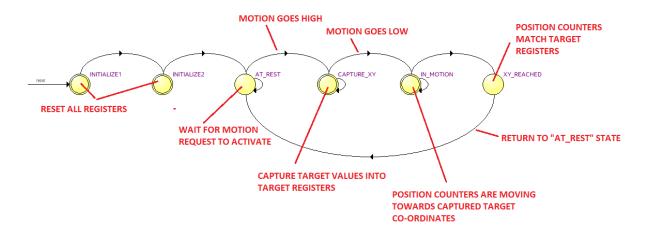

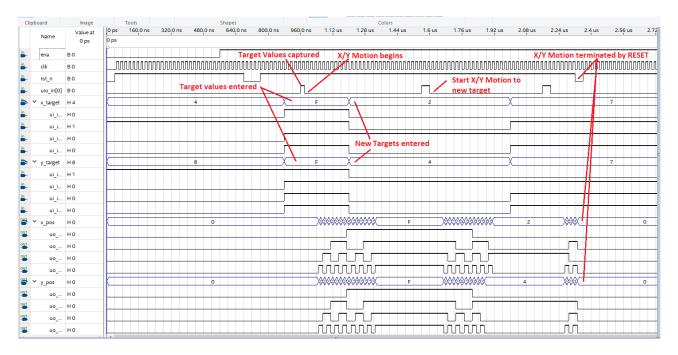

| X/Y Controller [416]                                      | 256 |

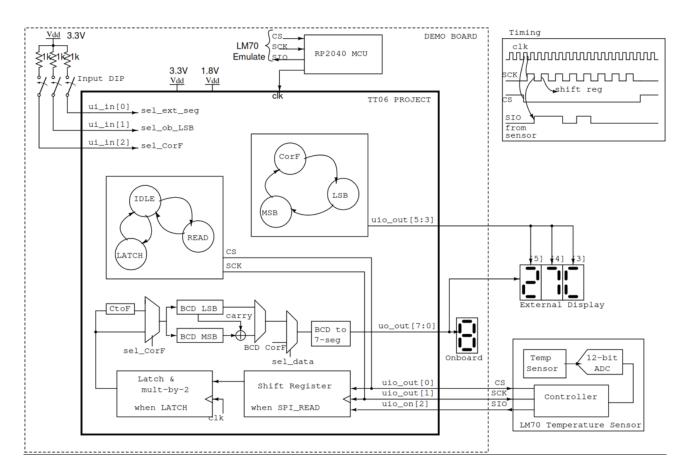

| Digital Temperature Monitor [417]                         | 259 |

| 32-Bit Galois Linear Feedback Shift Register [418]        | 263 |

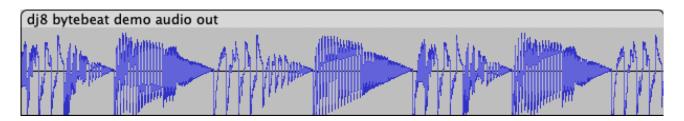

| DJ8 8-bit CPU [419]                                       | 266 |

| Servo Signal Tester [420]                                 | 272 |

| Bivium-B Non-Linear Feedback Shift Register [421]         | 274 |

| Servotester [422]                                         | 277 |

| Cyclic Redundancy Check 8 bit [423]                       | 278 |

| DEFAULT [424]                                             | 280 |

| Anomaly Detection using Isolation trees [425]             | 281 |

| Inverters [426]                                           | 283 |

| Lipsi: Probably the Smallest Processor in the World [427] |     |

| Chisel Hello World [428]                                  | 286 |

| Signed Unsigned multiplyer [429]                          |     |

| EFAB Demo 2 [430]                                         | 290 |

| Dual Deque [431]                                          | 292 |

| DFFRAM Example (128 bytes) [452]                          |     |

| Retro Console [458]                                       |     |

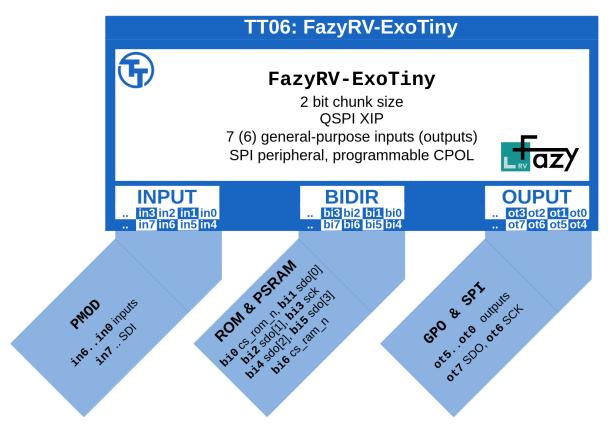

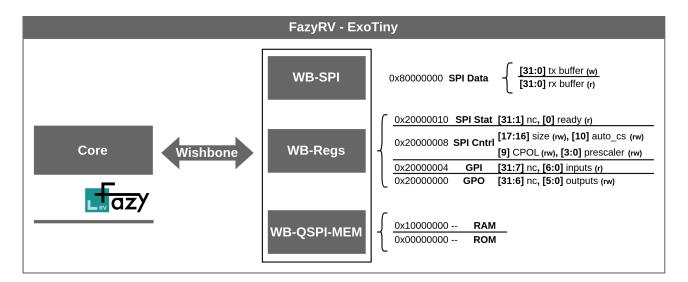

| FazyRV-ExoTiny [462]                                      |     |

|                                                           |     |

| HELP for tinyTapeout [481]                         | 331 |

|----------------------------------------------------|-----|

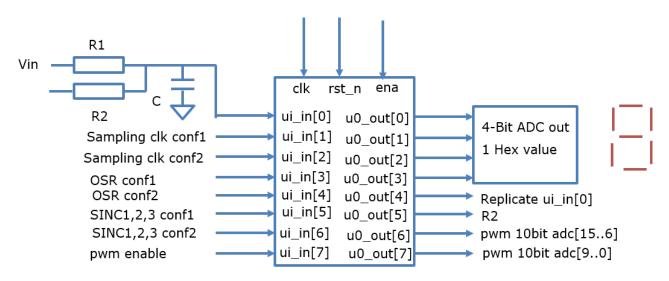

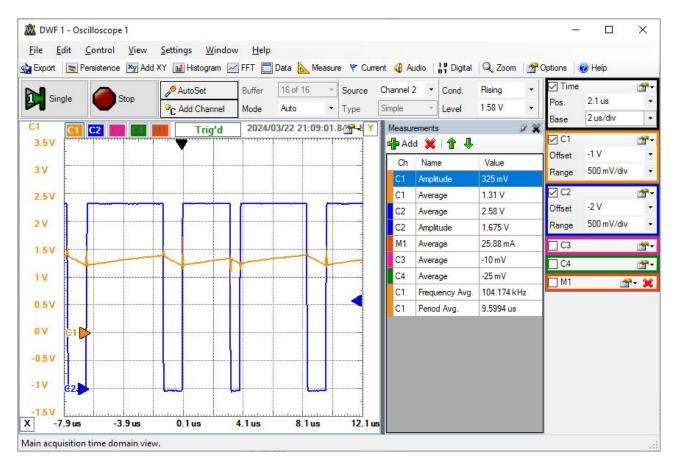

| 1st passive Sigma Delta ADC [482]                  | 332 |

| Parallel / SPI modulation tester [483]             | 336 |

| Flash ADC [484]                                    | 338 |

| CSIT-Luks [485]                                    | 341 |

|                                                    | 343 |

| Trivium Non-Linear Feedback Shift Register [487]   | 345 |

|                                                    | 348 |

| SADdiff_v1 [489]                                   | 350 |

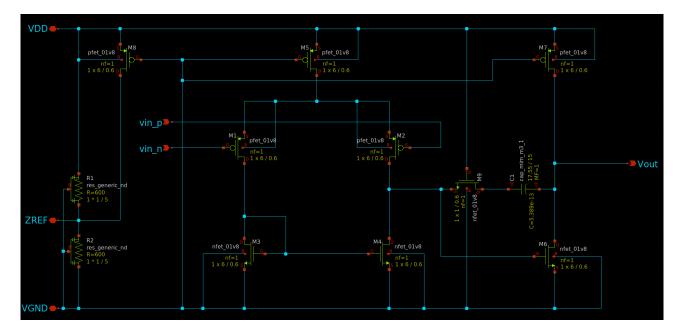

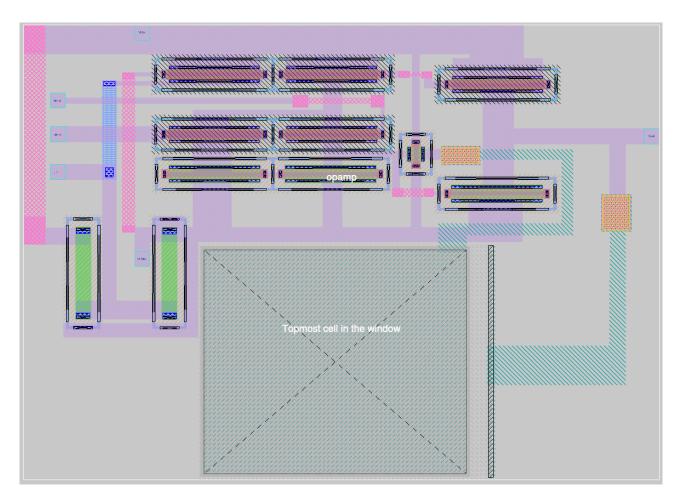

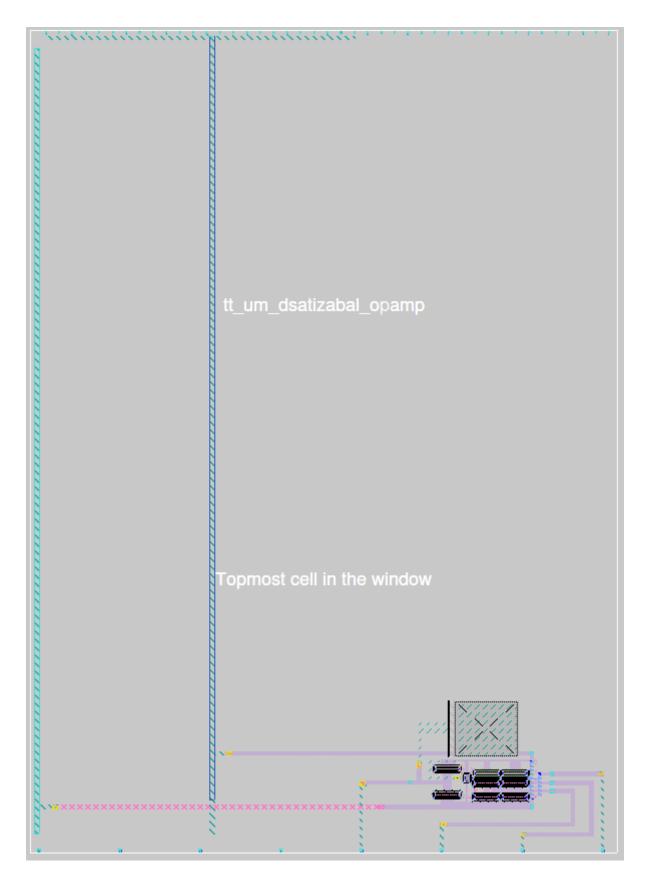

| Simple FET OpAmp with Sky130. [490]                | 351 |

|                                                    | 355 |

|                                                    | 358 |

| It's Alive [493]                                   | 364 |

|                                                    | 366 |

| BCD to single 7 segment display Converter [495]    | 368 |

| AudioChip_V2 [514]                                 | 369 |

|                                                    | 371 |

|                                                    | 373 |

|                                                    | 375 |

|                                                    | 377 |

| Analog Current Comparator [524]                    | 379 |

|                                                    | 381 |

|                                                    | 383 |

|                                                    | 385 |

|                                                    | 391 |

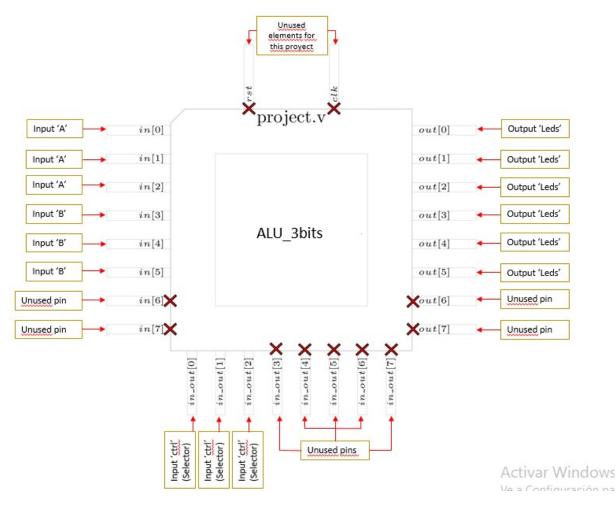

| 3-bit ALU [547]                                    | 392 |

| 8-bit Binary Counter [548]                         | 397 |

| SumLatchUART_System [549]                          |     |

| Power Management IC [550]                          |     |

| BIT COMPARATOR [551]                               |     |

| 2 bit Binary Calculator [552]                      |     |

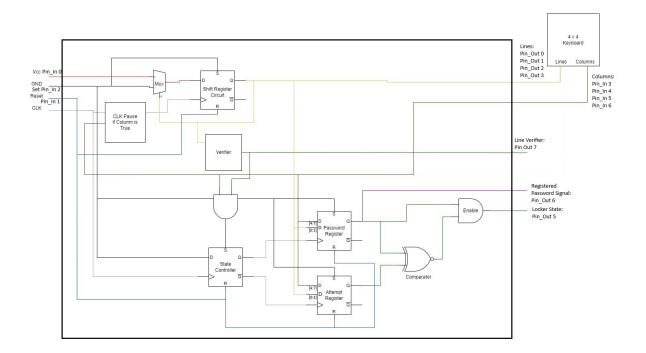

| IFSC Keypad Locker [553]                           | 405 |

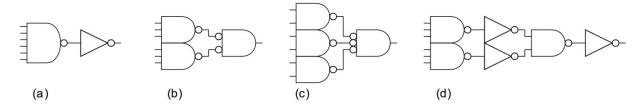

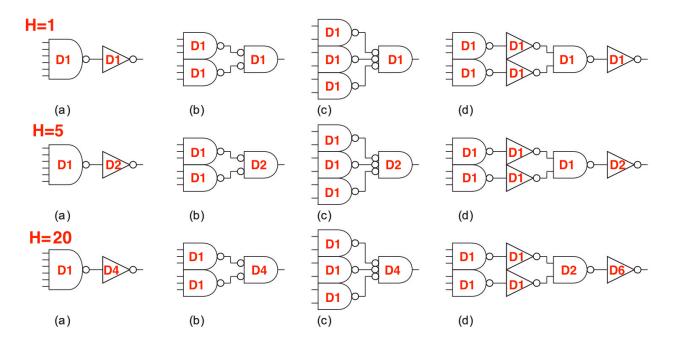

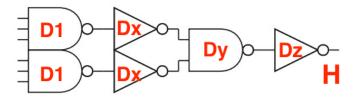

| Measurement of CMOS VLSI Design Problem 4.11 [554] | 408 |

| TDM Digital Clock [555]                            | 415 |

| Hardware Trojan Part II [556]                      | 416 |

| 4-Bit ALU [557]                                    |     |

| 8-bit DEM R2R DAC [558]                            | 420 |

| UART Transceiver [559]                             |     |

| Universal Motor and Actuator Controller [582]      |     |

| Dgrid_FPU [590]                                    |     |

| Parity Generator [608]                             |     |

| 24 H Clock [609]                                   |     |

| Sequence detector using 7-segment [610]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| CDMA_2024 [611]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |

| Simple Stopwatch [612]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 437 |

| Clock [613]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 439 |

| MULDIV unit (8-bit signed/unsigned) [614]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 440 |

| motor a pasos [615]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 445 |

| MULDIV unit (8-bit signed/unsigned) with sky130 HA/FA cells [616]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 451 |

| mult_2b [617]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |

| NCL LFSR [618]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

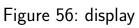

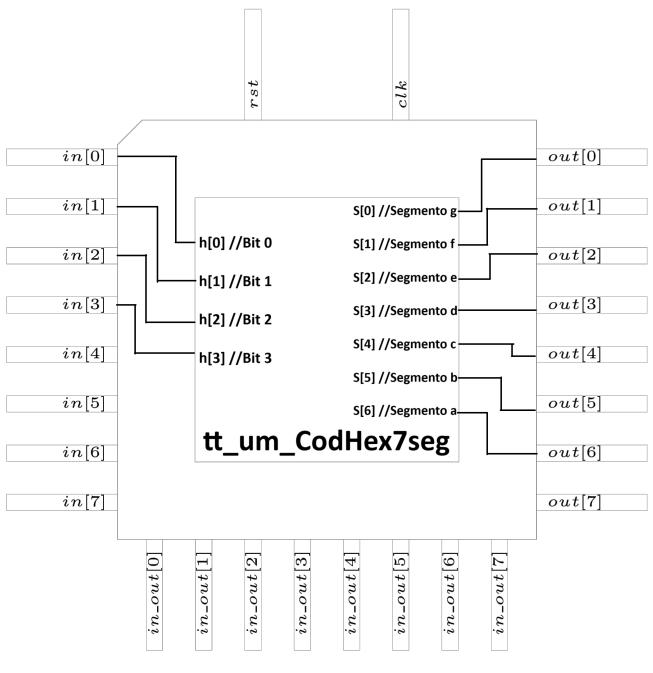

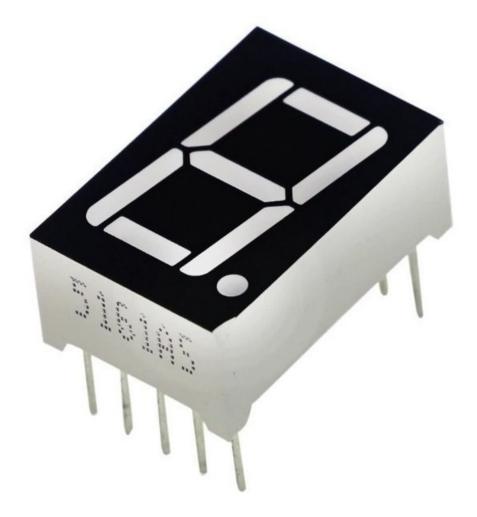

| Decodificador binario a display 7 segmentos hexadecimal [619]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |

| Latch RAM (64 bytes) [620]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

| Serial to Parallel Register [621]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

| Combination Lock [622]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

| PWM [623]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

| SPELL [642]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

| RNG3 [654]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

| 4-Bit Full Adder and Subtractor with Hardware Trojan [672]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

| Notre Dame Dorms LED [673]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

| Tiny ALU [674]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

| clk frequency divider controled by rom [675]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

| SAP-1 Computer [676]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

| PWM Controller [677]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

| 4 bit RAM [678]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |

| 8bit ALU [679]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

| ALU with a Gray and Octal decoders [680]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

| EVEN AND ODD COUNTERS [681]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

| Generador digital trifásico [682]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |

| Random number generator [683]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |

| Stepper [684]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 504 |

| TinyTapeout SPI Master [685]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

| serie_serie_register [686]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

| UACJ-Wallace multiplier [687]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |