# **Tiny Tapeout 7 Datasheet**

**Project Repository**

https://github.com/TinyTapeout/tinytapeout-07

June 12, 2024

# **Contents**

| Chip map                                                |       |   |       | 6      |

|---------------------------------------------------------|-------|---|-------|--------|

| Projects                                                |       |   |       | 9      |

| Chip ROM [0]                                            |       |   |       | <br>9  |

| TinyTapeout 7 Factory Test [1]                          |       |   |       | <br>11 |

| 6 bit addr [2]                                          |       |   |       | <br>13 |

| TTDLL [3]                                               |       |   |       |        |

| 8-Bit Register [4]                                      |       |   |       |        |

| UACJ_PWM [6]                                            |       |   |       |        |

| GPS signal generator [8]                                |       |   |       | <br>18 |

| Gaussian Blur [10]                                      |       |   |       |        |

| UART [12]                                               |       |   |       |        |

| Digital Timer [14]                                      |       |   |       |        |

| Clock Domain Crossing FIFO [36]                         |       |   |       |        |

| Pong-VGA [38]                                           |       |   |       |        |

| Iterative MAC [40]                                      |       |   |       |        |

| Adiabatic PSU sequencer test [42]                       |       |   |       |        |

| PRBS Generator [44]                                     |       |   |       |        |

| Full-adder out of a kmap [46]                           |       |   |       |        |

| dEFAULt 2hAC [64]                                       |       |   |       |        |

| ECC_test1 [65]                                          |       |   |       |        |

| All Digital DAC and Analog Comparators [66]             |       |   |       |        |

| 443MHz Manchester Decoding [67]                         |       |   |       |        |

| Dummy Counter [68]                                      |       |   |       |        |

| MicroCode Multiplier [69]                               |       |   |       |        |

| My 9-year-old son made an 8-bit counter chip [70]       |       |   |       |        |

| TT7 Simple Clock [71]                                   |       |   |       |        |

| Basilisc-2816 v0.1c CPU (experimental) [72]             |       |   |       |        |

| SIMON [73]                                              |       |   |       |        |

| VGA Snake Game [74]                                     |       |   |       |        |

| Modified Booth Multiplier [75]                          | <br>• | • | <br>• | <br>56 |

| GDS counter-measures experiment 1 [76]                  |       |   |       |        |

| unisnano [77]                                           |       |   |       |        |

| fractran-tt [78]                                        |       |   |       |        |

| Phase Shifted PWM Modulator [79]                        |       |   |       |        |

| 4bit_CPU_td4 [128]                                      |       |   |       |        |

| DVD Screensaver with Tiny Tapeout Logo (Tiny VGA) [130] |       |   |       |        |

| Ripple Carry Adder 8 bit [132]                          |       |   |       |        |

| DuckCPU [134]                                           |       |   |       |        |

| John Pong The Second [136]                              |       |   |       |        |

| Four NIST SP 800-22 tests implementation [138]          |       |   |       |        |

|                                                         |       |   |       |        |

| Subleq CPU with FRAM and UART [140]                     |       | • |       | <br>76 |

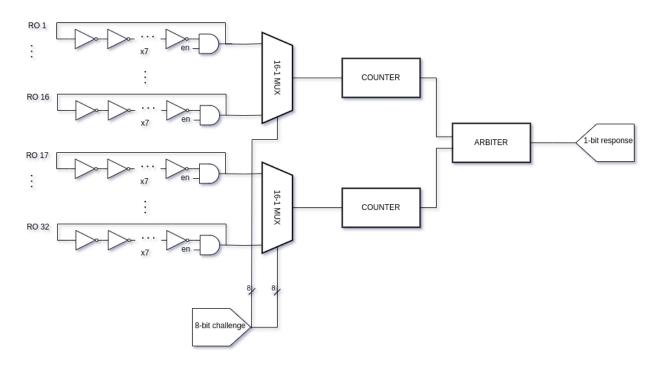

| RO-based Physically Unclonable Function (PUF) [142]                          |

|------------------------------------------------------------------------------|

| FastMagnitudeComparator [192]                                                |

| 8 bit PRNG [194]                                                             |

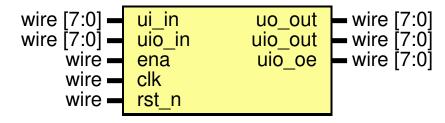

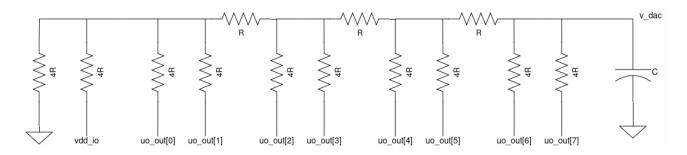

| 8-bit DEM R2R DAC [196]                                                      |

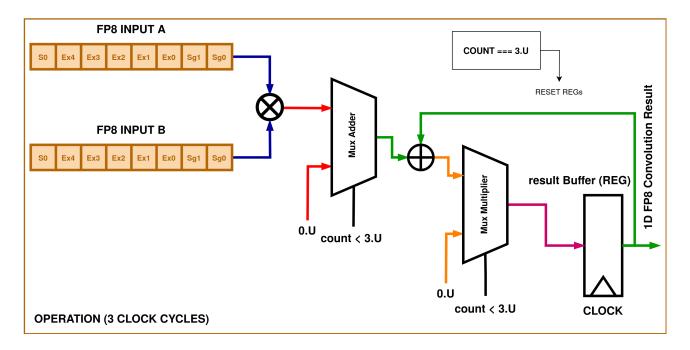

| FP-8 MAC Module [198]                                                        |

| SerDes [200]                                                                 |

| Basilisc-2816 v0.1b CPU [202]                                                |

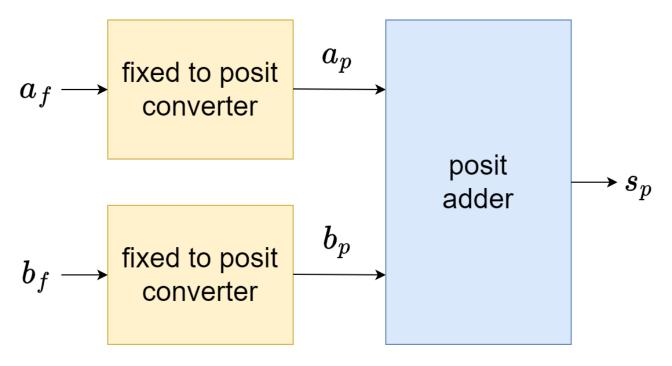

| integer to posit converter and adder [204]                                   |

| LFSR [206]                                                                   |

| Serial Character LED Matrix [225]                                            |

| DDS and DAC [227]                                                            |

| PLL Playground [229]                                                         |

| Analog comparator [231]                                                      |

| Gilbert Mixer [233]                                                          |

| Instrumentation Amplifier for Electrocardiogram Signal Adquisition [239] 113 |

| router [256]                                                                 |

| Conway's Terminal [258]                                                      |

| Zilog Z80 [259]                                                              |

| VGA Perlin Noise [260]                                                       |

| 4-bit R2R DAC [261]                                                          |

| MOS Bandgap [263]                                                            |

| VGA Checkers [264]                                                           |

| Analog buffer test [265]                                                     |

| Current Mode Trigger [267]                                                   |

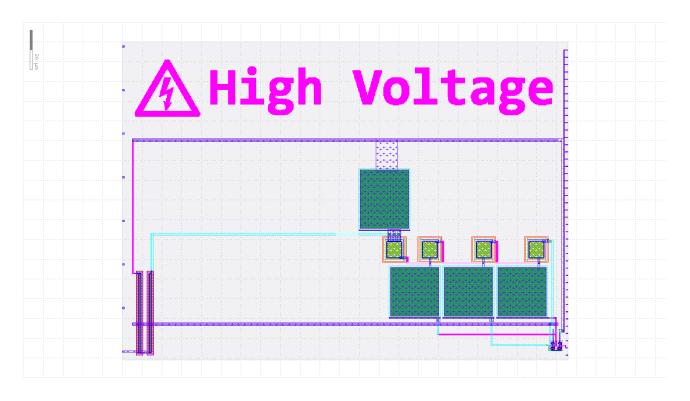

| Dickson Charge Pump [269]                                                    |

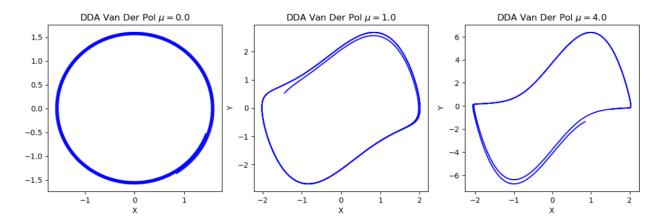

| DDA solver for van der Pol oscillator [270]                                  |

| Analog Test Circuit ITS 2 [271]                                              |

| VGA player [320]                                                             |

| Explorer [322]                                                               |

| Real Time Motor Controller [324]                                             |

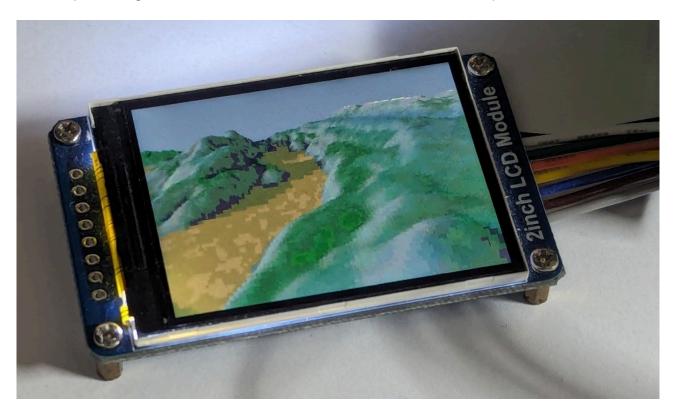

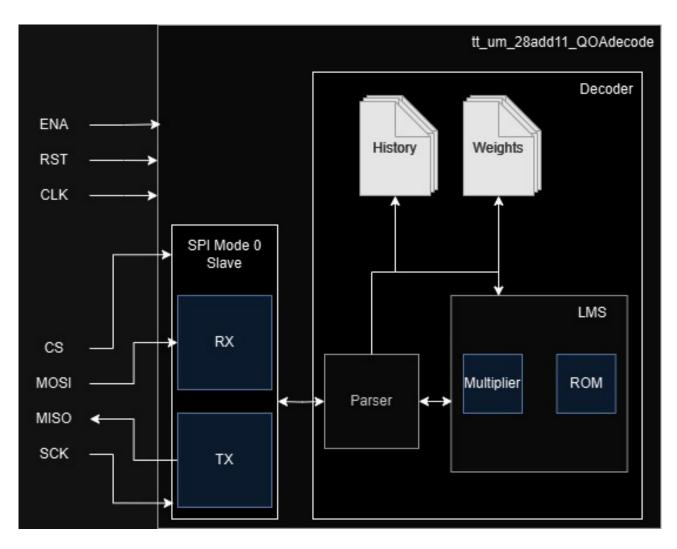

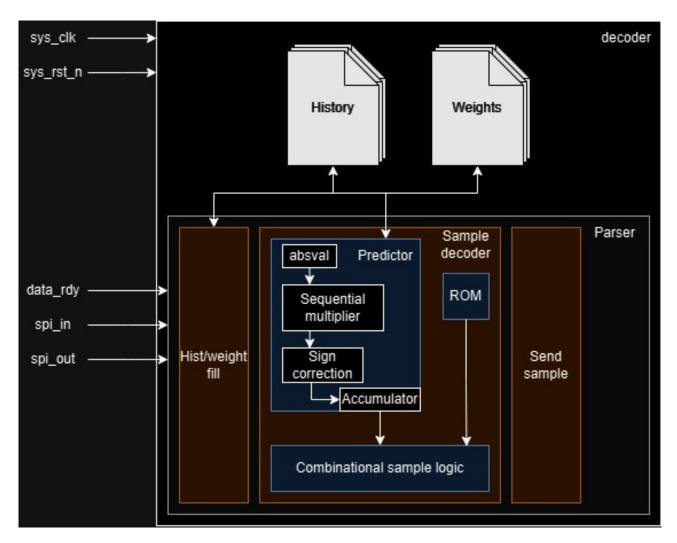

| QOA Decoder [326]                                                            |

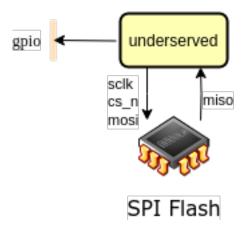

| underserved [328]                                                            |

| co processor for precision farming [330]                                     |

| Delay Line Time Multiplexed NAND Gate [332]                                  |

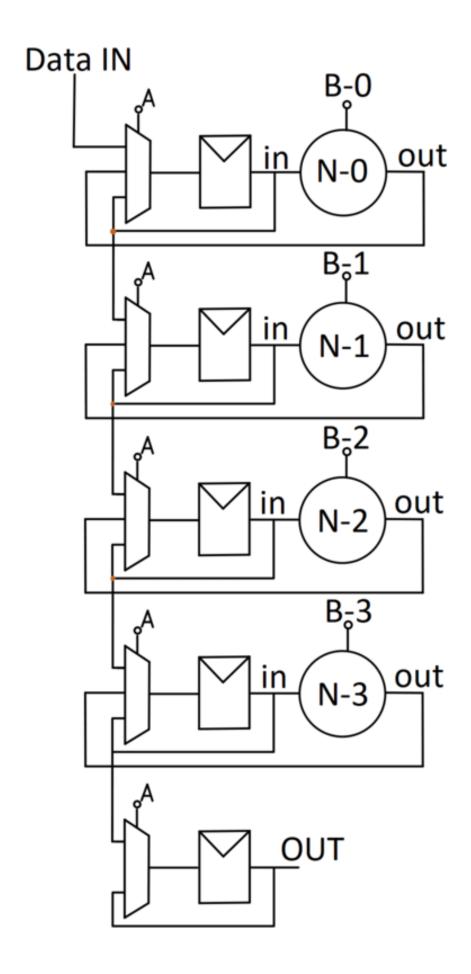

| Neural Network dinamic [334]                                                 |

| Chess [452]                                                                  |

| Mastermind [458]                                                             |

| TinyWSPR [462]                                                               |

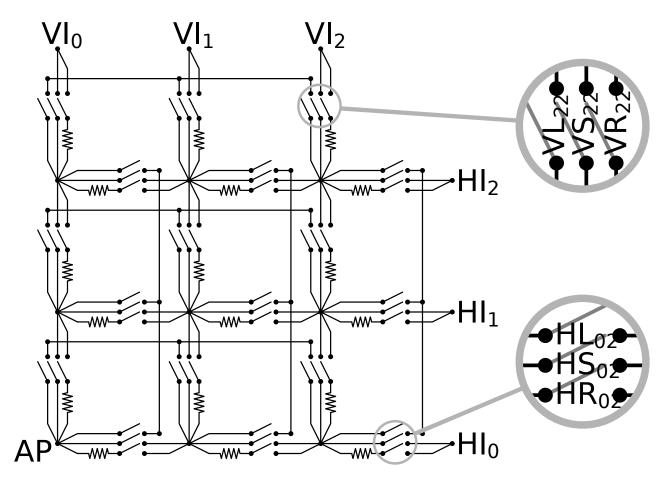

| Mini AIE: 2x2 CGRA with Ring-NoC [480]                                       |

| Field Programmable Resistor Network [482]                                    |

| AY-8193 single channel DAC [484]                                             |

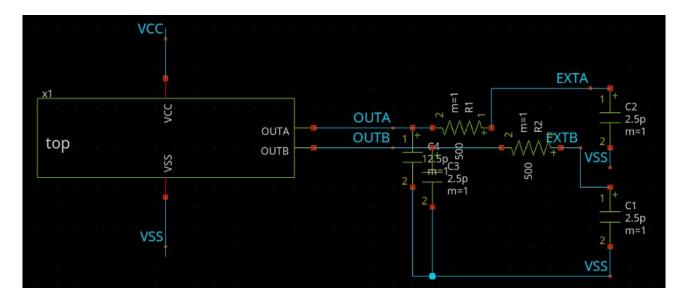

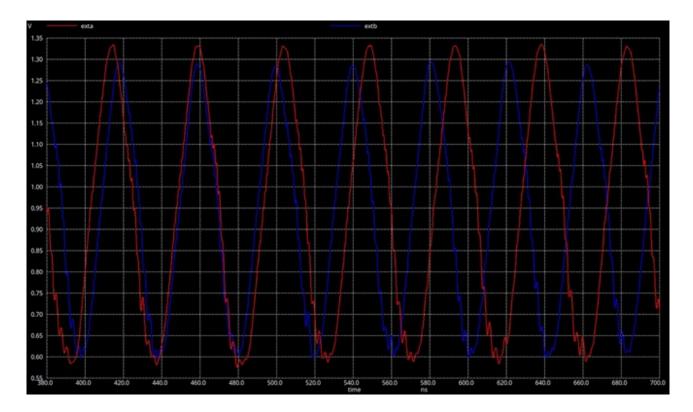

| dual oscillator [486]                                                        |

| Analog TDC [488]                                                         |     |

|--------------------------------------------------------------------------|-----|

| 12 bit SAR ADC [490]                                                     | 191 |

| RF_peripheral_circuits [492]                                             | 196 |

| mixed_signal_pulse_gen [494]                                             | 198 |

| TT07 Analog Factory Test [512]                                           | 200 |

| Tiny Eater 8 Bit [514]                                                   | 202 |

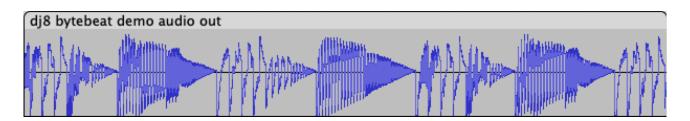

| DJ8 8-bit CPU w/ DAC [516]                                               | 208 |

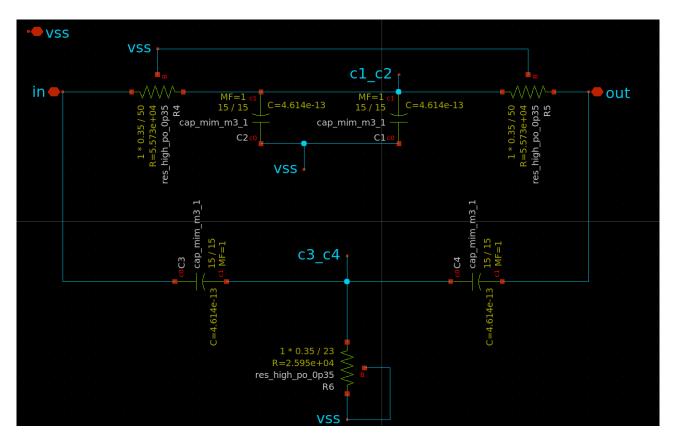

| Twin Tee Sine Wave Generator [518]                                       | 212 |

| Classic 8-bit era Programmable Sound Generator AY-3-8913 [520]           | 217 |

| Double Balanced Mixer and Quadrature Divider [522]                       | 219 |

| TT07 Differential Receiver test [524]                                    | 221 |

| QIF Neuron [526]                                                         | 223 |

| badGPU [582]                                                             |     |

| KianV RISC-V RV32E Baremetal SoC [588]                                   | 229 |

| TinyTPU [590]                                                            |     |

| 8-bit Vector Compute-in-SRAM [642]                                       | 232 |

| Mandelbrot Set Accelerator (32-bit IEEE 754) [654]                       | 238 |

| raybox-zero TT07 edition [714]                                           | 241 |

| tiny sha256 [718]                                                        | 244 |

| SPELL [782]                                                              | 245 |

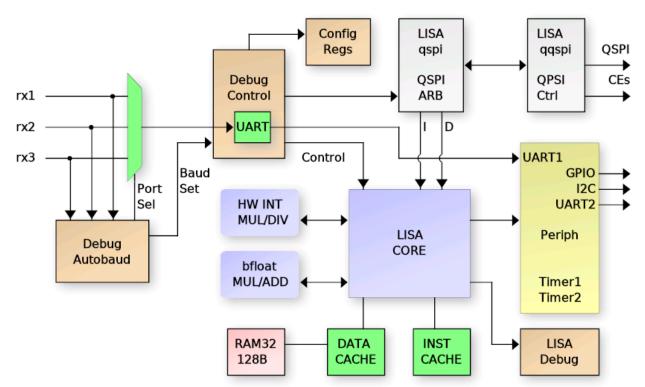

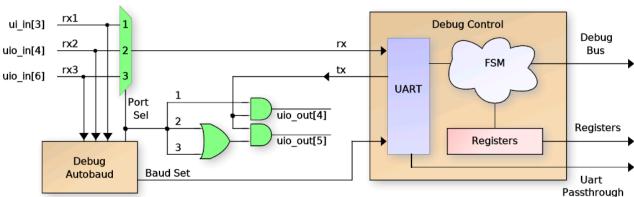

| LISA Microcontroller with TTLC [846]                                     | 250 |

| Simon Says memory game [897]                                             | 268 |

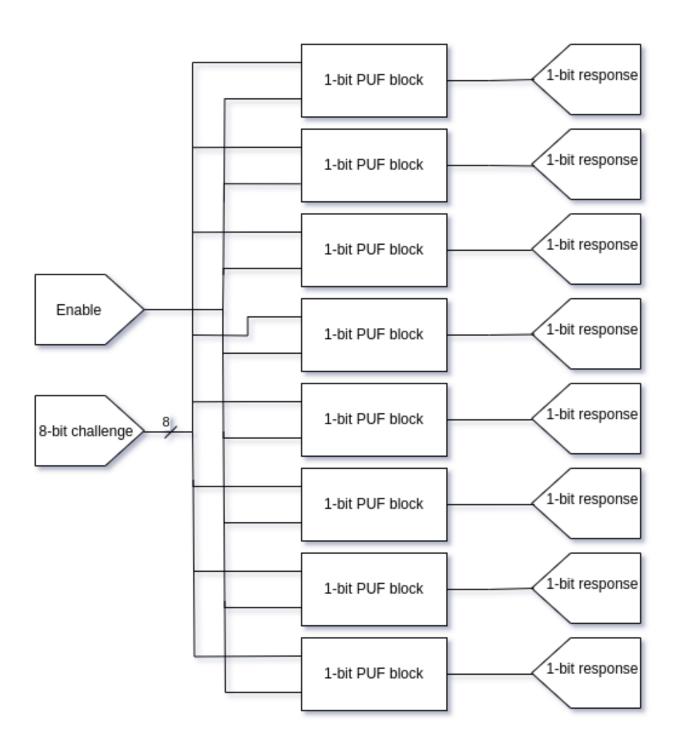

| Reversible logic based Ring-Oscillator Physically Unclonable Function (R | 0-  |

| PUF) [899]                                                               | 271 |

| CRC-8 CCITT [901]                                                        | 273 |

| VGA clock [903]                                                          |     |

| Padlock [905]                                                            | 277 |

| 7-Seg 'Tiny Tapeout' Display [907]                                       | 279 |

| clock [909]                                                              | 281 |

| Tiniest GPU [910]                                                        |     |

| SUBNEG CPU [911]                                                         |     |

| Stopwatch Project [961]                                                  |     |

| calculator [963]                                                         |     |

| Mini Light Up Game [965]                                                 |     |

| Basilisc-2816 v0.1a CPU [967]                                            | 289 |

| RLE Video Player [969]                                                   |     |

| secret L [971]                                                           |     |

| Send Receive [973]                                                       |     |

| RISCV32I with spi wrapper [974]                                          |     |

| ALU 74181 [975]                                                          | 329 |

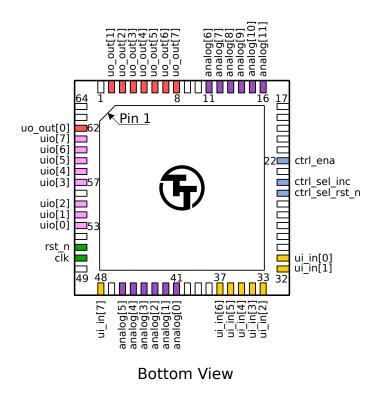

| Pinout                                                                   | 333 |

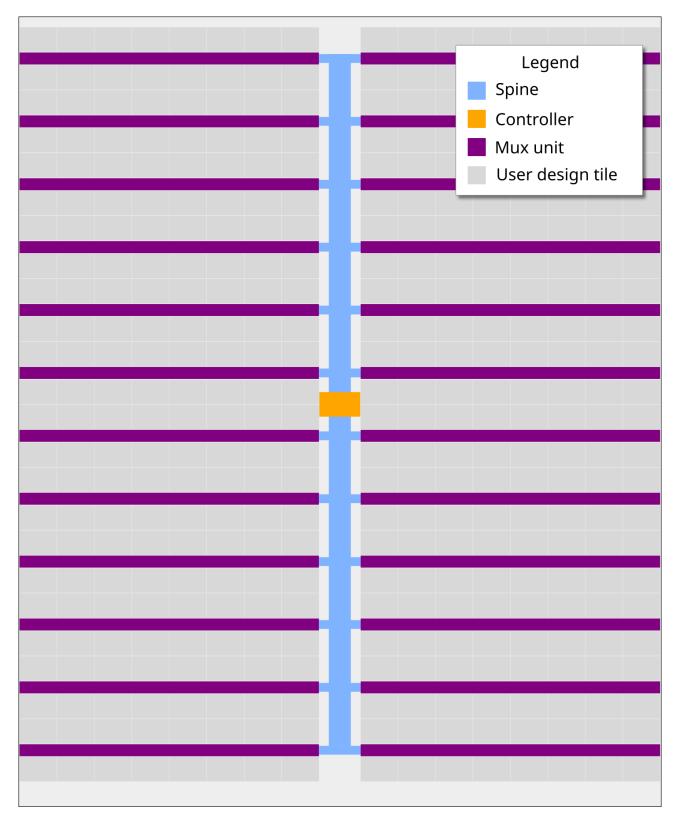

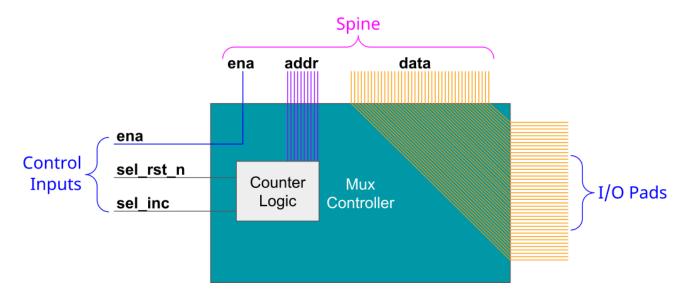

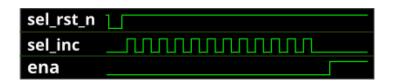

| The Tiny Tapeout Multiplexer | 334 |

|------------------------------|-----|

| Overview                     | 334 |

| Operation                    | 334 |

| Pinout                       | 337 |

| Sponsored by                 | 340 |

| Team                         | 340 |

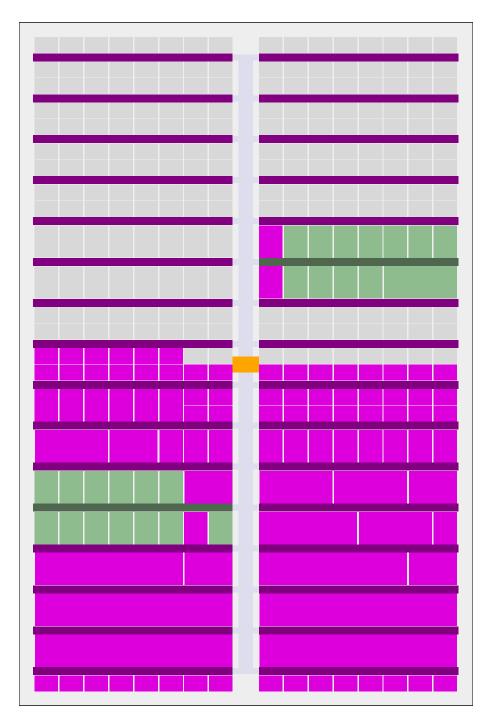

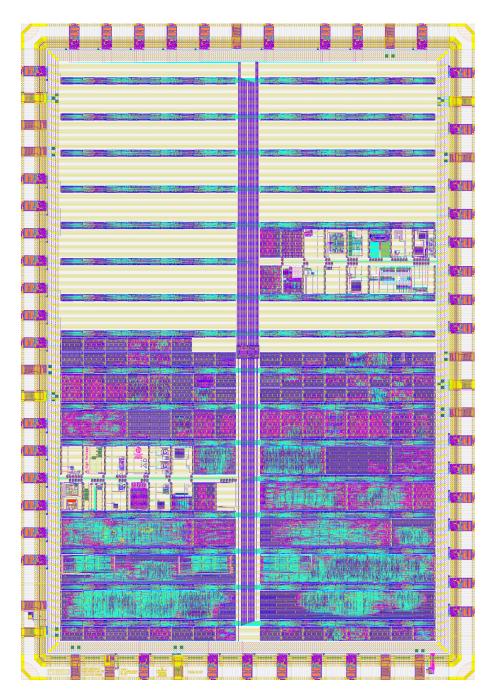

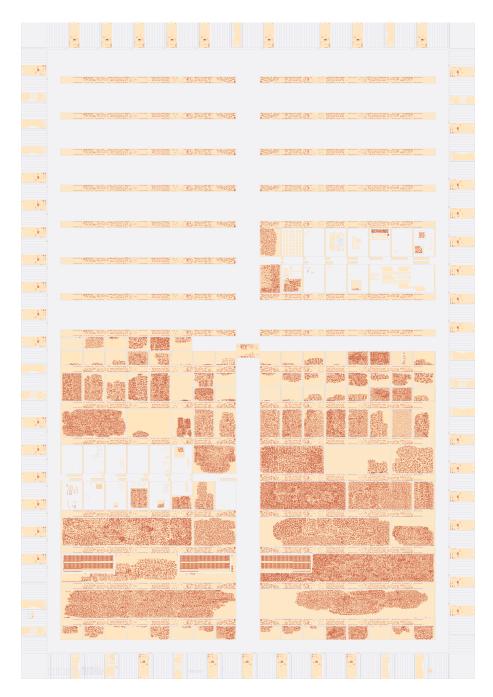

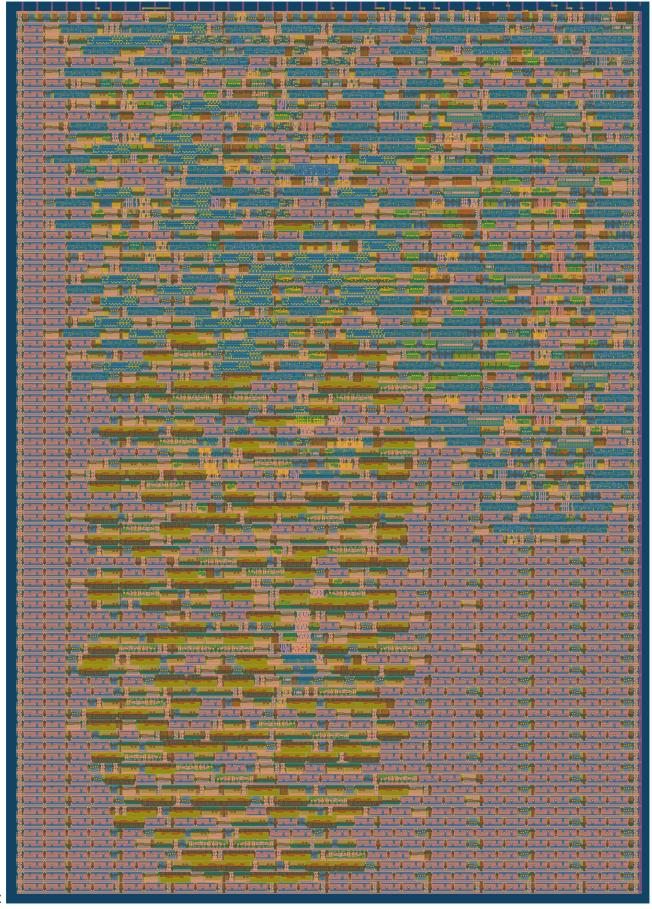

# Chip map

Figure 1: Full chip map

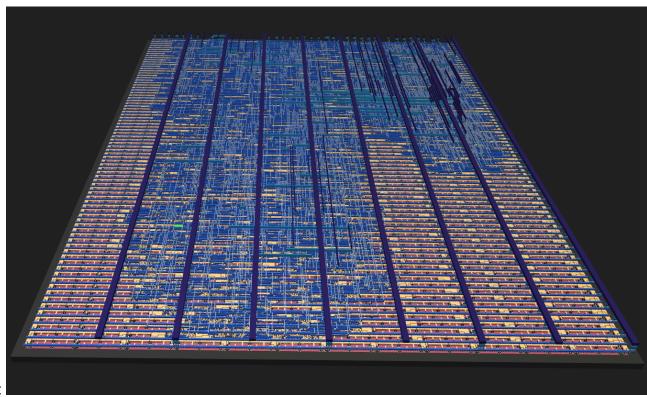

Figure 2: GDS render

Figure 3: Logic density (local interconnect layer)

# **Projects**

# Chip ROM [0]

Author: Uri Shaked

Description: ROM with information about the chip

GitHub repository

HDL projectMux address: 0

Extra docsClock: 0 Hz

#### How it works

ROM memory that contains information about the Tiny Tapeout chip. The ROM is 8-bit wide and 256 bytes long.

**The ROM layout** The ROM layout is as follows:

| Address | Length | Encoding  | Description                                            |

|---------|--------|-----------|--------------------------------------------------------|

| 0       | 8      | 7-segment | Shuttle name (e.g. "tt07"), null-padded                |

| 8       | 8      | 7-segment | Git commit hash                                        |

| 32      | 96     | ASCII     | Chip descriptor (see below)                            |

| 248     | 4      | binary    | <pre>Magic value: &amp;quot;TT\xFA\xBB&amp;quot;</pre> |

| 252     | 4      | binary    | CRC32 of the ROM contents, little-endian               |

**The chip descriptor** The chip descriptor is a simple null-terminated string that describes the chip. Each line is a key-value pair, separated by an equals sign. It contains the following keys:

| Key  | Description                                                                | Example value                                  |

|------|----------------------------------------------------------------------------|------------------------------------------------|

| repo | The identifier of the shuttle The name of the repository The commit hash * | tt07<br>TinyTapeout/tinytapeout-07<br>a1b2c3d4 |

• The commit hash is only included for Tiny Tapeout 5 and later.

Here is a complete example of a chip descriptor:

shuttle=tt07

repo=TinyTapeout/tinytapeout-07

commit=a1b2c3d4

**How the ROM is generated** The ROM is automatically generated by tt-support-tools while building the final GDS file of the chip. Look at the rom.py file in the repository for more details.

#### How to test

Read the ROM contents by setting the address pins and reading the data pins. The first 16 bytes of the ROM are 7-segment encoded and contain the shuttle name and commit hash. You can read them by toggling the first four DIP switches and observing the on-board 7-segment display.

| # | Input   | Output  | Bidirectional |

|---|---------|---------|---------------|

| 0 | addr[0] | data[0] |               |

| 1 | addr[1] | data[1] |               |

| 2 | addr[2] | data[2] |               |

| 3 | addr[3] | data[3] |               |

| 4 | addr[4] | data[4] |               |

| 5 | addr[5] | data[5] |               |

| 6 | addr[6] | data[6] |               |

| 7 | addr[7] | data[7] |               |

### TinyTapeout 7 Factory Test [1]

Author: Tiny Tapeout

Description: Factory test module

GitHub repository

HDL projectMux address: 1Extra docs

Clock: 0 Hz

#### How it works

The factory test module is a simple module that can be used to test all the I/O pins of the ASIC.

It has three modes of operation:

- 1. Mirroring the input pins to the output pins (when rst\_n is low).

- 2. Mirroring the bidirectional pins to the output pins (when rst\_n is high sel is low).

- 3. Outputing a counter on the output pins and the bidirectional pins (when rst\_n is high and sel is high).

The following table summarizes the modes:

| rst_n | sel | Mode                 | ou_out value | uio pins |

|-------|-----|----------------------|--------------|----------|

| 0     | Χ   | Input mirror         | ui_in        | High-Z   |

| 1     | 0   | Bidirectional mirror | uio_in       | High-Z   |

| 1     | 1   | Counter              | counter      | counter  |

The counter is an 8-bit counter that increments on every clock cycle, and resets when rst n is low.

#### How to test

- 1. Set rst\_n low and observe that the input pins (ui\_in) are output on the output pins (ou\_out).

- 2. Set rst\_n high and sel low and observe that the bidirectional pins (uio\_in) are output on the output pins (ou out).

- 3. Set sel high and observe that the counter is output on both the output pins (ou\_out) and the bidirectional pins (uio).

| # | Input         | Output                            | Bidirectional           |

|---|---------------|-----------------------------------|-------------------------|

| 0 | sel / in_a[0] | output[0] / counter[0]            | in_b[0] / counter[0]    |

| 1 | in_a[1]       | $output[1] \ / \ counter[1]$      | $in\_b[1] / counter[1]$ |

| 2 | in_a[2]       | output[2] / counter[2]            | in_b[2] / counter[2]    |

| 3 | in_a[3]       | <pre>output[3] / counter[3]</pre> | in_b[3] / counter[3]    |

| 4 | in_a[4]       | output[4] / counter[4]            | in_b[4] / counter[4]    |

| 5 | in_a[5]       | output[5] / counter[5]            | in_b[5] / counter[5]    |

| 6 | in_a[6]       | output[6] / counter[6]            | in_b[6] / counter[6]    |

| 7 | in_a[7]       | output[7] / counter[7]            | in_b[7] / counter[7]    |

# 6 bit addr [2]

Author: Nigel Coburn, Jason Murray

• Description: 6 bit addr, with continuous assignment (no clock)

GitHub repository

HDL projectMux address: 2

Extra docsClock: 0 Hz

#### How it works

6 Bit Addr: Overview

2x6 bit inputs with a carry 6 bit output with a carry

#### How to test

### Addition with no carry

$A=0b000001\ IC=0\ B=0b000001\ O=0b000010\ OC=0$

#### **External hardware**

List external hardware used in your project (e.g. PMOD, LED display, etc), if any

| # | Input               | Output            | Bidirectional       |

|---|---------------------|-------------------|---------------------|

| 0 | 0th bit for A input | 0th bit for A+B   | 0th bit for B input |

| 1 | 1st bit for A input | 1st bit for $A+B$ | 1st bit for B input |

| 2 | 2nd bit for A input | 2nd bit for $A+B$ | 2nd bit for B input |

| 3 | 3rd bit for A input | 3rd bit for $A+B$ | 3rd bit for B input |

| 4 | 4th bit for A input | 4th bit for $A+B$ | 4th bit for B input |

| 5 | 5th bit for A input | 5th bit for $A+B$ | 5th bit for B input |

| 6 | Input Carry bit     | Output Carry bit  |                     |

| 7 |                     |                   |                     |

# TTDLL [3]

Author: Dan Petrisko

Description: An all-digital DLL

GitHub repository

HDL projectMux address: 3

Extra docsClock: 0 Hz

#### How it works

This is a test design for all-digital tunable, hierarchical and composable oscillation blocks. The base primitives are delay elements, delay rows, delay columns and control registers. Control registers determine which delay elements are active at a given setting, increasing or decreasing the total period. We deomnstrate a clock generator and 90-degree delay line as potential applications for these elements. This design has been validated in TSMC-28 using commercial tools. This will be the first test of this design on open tools and and open PDK.

For a clock generator there are an odd number of delay elements, which causes the total delay to act as half of a clock oscillation. This is a fairly simple ring oscillator design, although it is designed to be glitch-free upon frequency changes and have even steps between tuning frequencies.

For a 90-degree delay line (useful in DDR controllers among other things), we take two odd delay blocks equal in size. The output of the first block is the generated 90-degree clock. The output of the second block is a generated 180-degree clock. Now, 180-degrees is trivial phase to generate – simply invert the input clock. We can compare the racing 180-degree clocks using a (intentionally) metastable register. If the dly180 > clkinv, then we reduce the dly latency. If the dly180 < clkinv, then we increase the dly latency. This will automatically tune dly90 due to the symmetry of the blocks.

TODO: Images coming soon!

#### How to test

The main driver for hardware testing is bsg\_tag (https://github.com/bespoke-silicon-group/basejump\_stl), which has python and C++ drivers available. The exact tag sequence can be found in the test/ directory. Examples of using this testing infrastructure is in ZynqParrot (https://github.com/black-parrot-hdk/zynq-parrot). If the

sequence is completed successfully, the IO outputs will increment proporotionally to the current clock frequency!

#### **External hardware**

Although the clock and delay period can be approximated by the counter outputs, an external oscilloscope is helpful for visualizing the clock and delay waveforms themselves, including phase and jitter.

| #                     | Input                                     | Output                                                     | Bidirectional                                                                   |

|-----------------------|-------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------|

| 0<br>1<br>2<br>3<br>4 | p_tag_clk_i<br>p_tag_en_i<br>p_tag_data_i | p_osc_clk_o p_ds_clk_o p_gen_clk_o p_dly_clk_o p_mon_clk_o | p_div_count_0_o p_div_count_1_o p_div_count_2_o p_div_count_3_o p_div_count_4_o |

| 5<br>6<br>7           |                                           | p_div_clk_o<br>p_ds_reset_o<br>p_mon_reset_o               | <pre>p_div_count_5_o p_div_count_6_o p_div_count_7_o</pre>                      |

# 8-Bit Register [4]

Author: Eric Ulteig

• Description: The 8 inputs are saved to the 8 outputs on a clock pulse

GitHub repository

Wokwi projectMux address: 4

Extra docsClock: 1 Hz

### How it works

D-type flip-flops are used to store the input bits.

#### How to test

The 8 inputs are saved to the 8 outputs. Use the push button to save and hold.

| # | Input  | Output  | Bidirectional |

|---|--------|---------|---------------|

| 0 | input1 | output1 |               |

| 1 | input2 | output2 |               |

| 2 | input3 | output3 |               |

| 3 | input4 | output4 |               |

| 4 | input5 | output5 |               |

| 5 | input6 | output6 |               |

| 6 | input7 | output7 |               |

| 7 | input8 | output8 |               |

# UACJ\_PWM [6]

Author: Grupo C

Description: Implementacion de un modulador de ancho de pulso (PWM) mediante Verilog esencial en electronica para regular la energia entregada a un dispositivo, este diseño esta bajo los requisitos del sistema

GitHub repository

HDL projectMux address: 6

Extra docs

Clock: 10000000 Hz

#### How it works

con una Implementacion de un modulador de ancho de pulso (PWM) mediante Verilog esencial en electronica para regular la energia entregada a un dispositivo, este diseño esta bajo los requisitos del sistema

#### How to test

con un fpga de xilinx basys 3

#### **External hardware**

List external hardware used in your project (e.g. PMOD, LED display, etc), if any

| # | Input      | Output | Bidirectional |

|---|------------|--------|---------------|

| 0 | duty_[0]   | pwm_o  |               |

| 1 | $duty_[1]$ |        |               |

| 2 | duty_[2]   |        |               |

| 3 | duty_[3]   |        |               |

| 4 | duty_[4]   |        |               |

| 5 | duty_[5]   |        |               |

| 6 | duty_[6]   |        |               |

| 7 | duty_[7]   |        |               |

### **GPS** signal generator [8]

- Author: Grupo de Aplicaciones en Sistemas Embebidos Universidad Tecnológica Nacional Facultad Regional Haedo

- Description: Generate a GPS IF signals using the following parameters: sat id, code phase, doppler and SNR.

- GitHub repository

- HDL projectMux address: 8

- Extra docs

Clock: 16368000 Hz

#### How it works

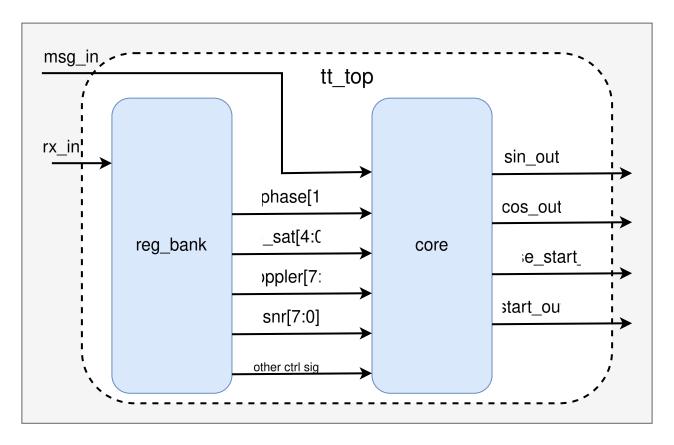

The gps signal generator is a configurable block capable used to test search algorithms for GPS receivers. It is composed by two main blocks:

- Register bank: a set of configuration registers with a uart rx interface for writeonly operations. These registers lets the user control: satellite ID, PRN code phase, doppler frequency, noise level, among others.

- Core: the core of the project is composed by a Gold Code generator, an NCO (numerically controlled oscillator) and PRNGs (pseudo random number generators). The core also provides a 1-bit message input to modulate the generated signal with a "navigation message".

### **Block Diagram**

#### Serial communication

Register bank configuration is performed through the serial interface. The operation to write a single register is divided in two steps:

- Send address byte.

- Send data byte.

### Register bank description

This section describes the registers of the device and its functionality.

Figure 4: Block Diagram

### **Control Register:**

Address: 0x0Width: 8 bits

| b7 | b6 | b5         | b4        | b3 | b2 | b1 | b0             |

|----|----|------------|-----------|----|----|----|----------------|

| X  | Χ  | signal off | noise off | Χ  | Χ  | Χ  | general enable |

• b0: general enable of the core.

• b4: turn off noise generator.

b6: turn off signal.

### Sat\_id register:

Address: 0x2Width: 5 bits

| b4    | b3    | b2    | b1    | b0    |

|-------|-------|-------|-------|-------|

| id[4] | id[3] | id[2] | id[1] | id[0] |

• id[4:0]: Selects the satellite PRN code. There are up to 32 satellite PRN codes.

### Doppler register:

Address: 0x3Width: 8 bits

| b7   | b6   | b5   | b4   | b3   | b2   | b1   | b0   |

|------|------|------|------|------|------|------|------|

| d[7] | d[6] | d[5] | d[4] | d[3] | d[2] | d[1] | d[0] |

• d[7:0]: Doppler selection. The resultant frequency will be equal to:

$$f_{out} = 4092000.0 - 8000.0 + 500.0 * (d-176)MHz \\$$

### Code phase low register:

Address: 0x4Width: 8 bits

| b7   | b6   | b5   | b4   | b3   | b2   | b1   | b0   |

|------|------|------|------|------|------|------|------|

| p[7] | p[6] | p[5] | p[4] | p[3] | p[2] | p[1] | p[0] |

• p[7:0]: low byte of the PRN code phase.

### Code phase high register:

Address: 0x5Width: 8 bits

| b7    | b6    | b5    | b4    | b3    | b2    | b1   | b0   |

|-------|-------|-------|-------|-------|-------|------|------|

| p[15] | p[14] | p[13] | p[12] | p[11] | p[10] | p[9] | p[8] |

• p[15:8]: high byte of the PRN code phase.

### **SNR** register

Address: 0x6Width: 3 bits

| b2     | b1     | b0     |

|--------|--------|--------|

| snr[2] | snr[1] | snr[0] |

• snr[2:0]: This indicates how many right shifts (») will be applied to the generated signal. Applying more shifts reduces the amplitude of the signal with respect to the generated noise, reducing the SNR.

#### How to test

Clock frequency of the system should be set to 16.368 MHz. The register bank is configured with a uart interface at 115200 bands. Enable the design by writting the corresponding bit of the control bank.

**External hardware** A micropocessor or FPGA can be used to modulate the navigation message at the input. The output can be recorded for post-analysis or fed to the digital front end of a GPS receiver. The output is a 1-bit signal.

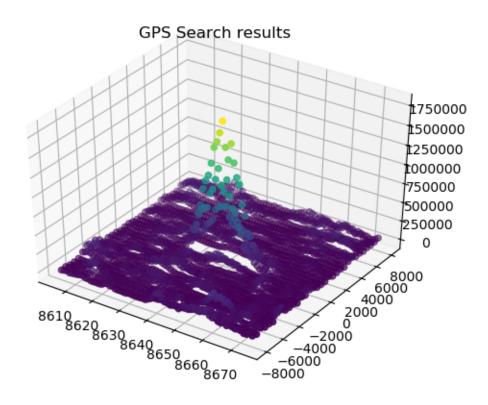

Figure 5: search\_example

**Example:** expected output of a search algorithm

| # | Input                                                                | Output                                                                                                                          | Bidirectional |

|---|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------|

| 0 | msg_in - Used to modulate GPS signal with custom navigation message. | sin_out - Sine output with CA+msg modulation + noise.                                                                           | Not used      |

| 1 | Not used                                                             | cos_out - Cosine output with CA+msg modulation (no noise).                                                                      | Not used      |

| 2 | Not used                                                             | noise_start_or - Start of PRNG sequence used as noise.                                                                          | utNot used    |

| 3 | rx_in - UART rx input. Used to configure the register bank.          | start_out - Start of GPS signal. This output goes high when the configured phase matches the actual phase of the output signal. | Not used      |

| 4 | Not used                                                             | clk - Output<br>clock                                                                                                           | Not used      |

| 5 | Not used                                                             | Not used                                                                                                                        | Not used      |

| 6 | Not used                                                             | Not used                                                                                                                        | Not used      |

| 7 | Not used                                                             | Not used                                                                                                                        | Not used      |

### Gaussian Blur [10]

Author: Alfonso Cortes

• Description: 4-bit gaussian blur filter

GitHub repositoryWokwi projectMux address: 10

Extra docs

• Clock: 100000 Hz

#### How it works

This filter receives nine 4-bit pixels in a free-running shift register and performs a gaussian blur, returning the value of the middle pixel. The weights are as shown below.

|         | 1 | 2 | 1 |

|---------|---|---|---|

| 1<br>16 | 2 | 4 | 2 |

|         | 1 | 2 | 1 |

Figure 6: 0 \_9K4Upm5p0aBIKDS

#### How to test

Input the pixel value and its neighborhood (nine pixels) from left to right, top to bottom. Once the shift register is full (after nine clock cycles) the output can be sampled. The last stage of the shift register is also available at the output for testing purposes.

### **External hardware**

An FPGA should be useful.

| # | Input             | Output        | Bidirectiona |

|---|-------------------|---------------|--------------|

| 0 | reg_in[0]         | reg_out[0]    |              |

| 1 | $reg\!\!$ $in[1]$ | $reg\_out[1]$ |              |

| 2 | reg_in[2]         | reg_out[2]    |              |

| 3 | reg_in[3]         | reg_out[3]    |              |

| 4 |                   | blur[0]       |              |

| 5 |                   | blur[1]       |              |

| 6 |                   | blur[2]       |              |

| 7 |                   | blur[3]       |              |

|   |                   |               |              |

# **UART** [12]

Author: Elisa Parent

• Description: Connecting two digital devices

GitHub repositoryWokwi projectMux address: 12

Mux address: 12Extra docs

• Clock: 300 Hz

### How it works

Using a connector to send digital signals to different digital parts.

#### How to test

Switchs are used to pick the ASCII character

### **External hardware**

arduino,7-seg display, 8 switch

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 0 | in1   | out1   |               |

| 1 | in2   | out2   |               |

| 2 | in3   | out3   |               |

| 3 | in4   |        |               |

| 4 | in5   |        |               |

| 5 | in6   |        |               |

| 6 | in7   |        |               |

| 7 | in8   |        |               |

# Digital Timer [14]

Author: Francisca Donoso

• Description: The circuit acts as a configurable timer displaying the remaining time in binary form as time passes

GitHub repositoryWokwi projectMux address: 14

Extra docsClock: 0 Hz

#### How it works

A value is placed in the inputs from 0 to 7 to define how much it counts. Then, the start input is set to 1 to load that value, and it begins to count. When it reaches zero, the end flag is raised.

#### How to test

#### **External hardware**

It is recommended to use switches for the inputs, a button for the start input, and LEDs for all the outputs.

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 0 |       |        | in_start      |

| 1 |       |        |               |

| 2 |       |        |               |

| 3 |       |        |               |

| 4 |       |        | out_state     |

| 5 |       |        | out_end_flag  |

| 6 |       |        |               |

| 7 |       |        |               |

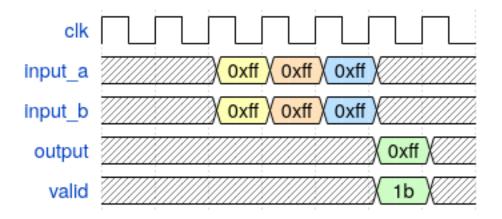

### Clock Domain Crossing FIFO [36]

Author: Pavan Mantri

Description: This FIFO buffers 4-bits data asynchronously across clock domains

GitHub repository

HDL projectMux address: 36

Extra docsClock: 0 Hz

#### How it works

The cdc\_fifo module transfers data between two clock domains: a write clock domain and a read clock domain. The module includes a dual-ported RAM(dpram) for storing data, along with logic for handling read and write operations(cdc\_fifo\_read\_state and cdc\_fifo-write-state). synchronizers(synchronizer) and binary/gray converters(binary\_to\_gray and gray\_to\_binary) ensure proper synchronization between two clock domains.

#### How to test

Hold write\_reset and read\_reset LOW while running the clock for a bit to reset, then raise to initialize the module.

writing to the fifo: Prepare your data on the 4-bit write\_data bus, ensure the full state is low and then raise write\_increment for 1 cycle of write\_clock to write data into the FIFO memory.

Reading from the fifo: The FIFO will present the current output on the read\_data bus. If empty is low, this output should be valid and you can acknowledge receive of this vallue by raising read\_increment for 1 cycle of read\_clock.

#### External hardware

NO external hardware is used.

| # | Input           | Output     | Bidirectional |

|---|-----------------|------------|---------------|

| 0 | write_clock     | empty      | write_reset   |

| 1 | write_increment | full       | read_reset    |

| 2 | read_clock      |            |               |

| 3 | read_increment  |            |               |

| 4 | write_data0     | read_data0 |               |

| 5 | write_data1     | read-data1 |               |

| 6 | write_data2     | read_data2 |               |

| 7 | write_data3     | read_data3 |               |

### Pong-VGA [38]

Author: Victor Zayakov

Description: Pong game over a VGA connection

GitHub repository

HDL projectMux address: 38

Extra docs

Clock: 50000000 Hz

#### How it works

This project is an implementation of the classic Pong video game. The interface is VGA, and the game will be displayed when connected to a monitor using a VGA cable. This includes all elements of the game: the two paddles and the ball, and a scoreboard.

The VGA protocol is implemented in hardware using Counter modules, RangeCheck modules, and an FSM to control them. It follows the VGA specification of  $640 \times 480$  resolution at 60 Hz, and operates using a 50 MHz clock signal.

The rest of the hardware for the Pong video game works on top of the VGA module.

#### How to test

The game can be tested through a direct connection to a monitor over VGA. Four switches and one button are required to interact with the game: An up/down switch and move/no-move switch for each of the two players, and one button for serving the ball.

To test the HDL design, one can compare the timing of all 8 VGA pins to the industry-standard timing defined here: http://www.tinyvga.com/vga-timing/640x480@60Hz

#### External hardware

The game requires four switches and one button to play, as mentioned above. It also requires an external splitter for each of the three VGA color signals. This is to split each of VGA\_R, VGA\_G and VGA\_B from 1-bit to 8-bit signals. These splitters can be placed on an external PCB.

| # | Input          | Output      | Bidirectional |

|---|----------------|-------------|---------------|

| 0 | R_move_switch  | VGA_CLK     |               |

| 1 | R_up_switch    | VGA_BLANK_N |               |

| 2 | L_move_switch  | VGA_SYNC_N  |               |

| 3 | L_up_switch    | VGA_VS      |               |

| 4 | serve_L_button | VGA_HS      |               |

| 5 |                | VGA_R       |               |

| 6 |                | VGA_G       |               |

| 7 |                | VGA_B       |               |

|   |                |             |               |

# Iterative MAC [40]

Author: Raju Machupalli

Description: Iterative multiply and accumulation unit for ML accelerators

GitHub repository

HDL projectMux address: 40

Extra docs

Clock: 50000000 Hz

#### How it works

The design contains iterative multiplication and addition unit. The multiplier is a 7x8 bit unit. At reset time, input through ui\_in pins stores in a reg and used as operand 1 for multiplier. After reset, operand 2 for multiplier is supplied through ui\_in at each clock cycle. The bidirectional pins provide operand 3 which will be added to the multiplier output. the output is read through uo\_out pins.

#### How to test

It's a bit complex, as bias values are supplied in different sequences, and output needs to change or align with the read output. Full instructions will be added here once the design is submitted for fabrication.

#### **External hardware**

It does not require any additional hardware supply the input data using CPU.

| # | Input    | Output       | Bidirectional |

|---|----------|--------------|---------------|

| 0 | ui_in[0] | uo_out[0]    | uio_in[0]     |

| 1 | ui_in[1] | $uo\_out[1]$ | uio_in[1]     |

| 2 | ui_in[2] | uo_out[2]    | uio_in[2]     |

| 3 | ui_in[3] | uo_out[3]    | uio_in[3]     |

| 4 | ui_in[4] | uo_out[4]    | uio_in[4]     |

| 5 | ui_in[5] | uo_out[5]    | uio_in[5]     |

| 6 | ui_in[6] | uo_out[6]    | uio_in[6]     |

| # | Input    | Output    | Bidirectional |

|---|----------|-----------|---------------|

| 7 | ui_in[7] | uo_out[7] | uio_in[7]     |

### Adiabatic PSU sequencer test [42]

Author: Chris Pacejo

• Description: test of a power supply sequencer for adiabatic circuits

GitHub repository

HDL projectMux address: 42

Extra docs

Clock: 32000000 Hz

#### How it works

This is a simple sequencer for a 9-step 4-phase combined power-clock PSU for adiabatic circuitry. The rate of each phase is 1/32 the input clock rate.

It generates two sets of control signals, for phases 0 and 1. The control signals indicates which step of the charging circuitry should be activated. (Phases 2 and 3 simply invert the meaning of the steps.)

Since there are not enough output pins to represent all steps, pin ui[0] selects whether phase 0 or 1 is routed to the output pins. Steps 1 through 7 of the selected phase are routed to uo[1] through uo[7]. Steps 0 and 8 of both phases 0 and 1 are routed to pins uio[0] through uio[3] regardless of the setting of ui[0].

Finally, four "digital sync" signals are generated and routed to pins uio [4] through uio [7]. These mark appropriate clock cycles when data can be latched in to or out from an adiabatic gate on phase 0 or 1.

#### How to test

This project is free-running. Simply issue a reset, then use ui [0] to select which phase you wish to monitor, and monitor it.

#### External hardware

No external hardware is necessary.

| # | Input            | Output             | Bidirectional                           |

|---|------------------|--------------------|-----------------------------------------|

| 0 | phase select (X) | selected phase (X) | phase 0 step 0                          |

| 1 |                  | phase X step 1     | phase 0 step 8                          |

| 2 |                  | phase X step 2     | phase 1 step 0                          |

| 3 |                  | phase X step 3     | phase 1 step 8                          |

| 4 |                  | phase X step 4     | digital sync phase 0 read               |

| 5 |                  | phase X step 5     | digital sync phase 1 read               |

| 6 |                  | phase X step 6     | digital sync phase 0 write              |

| 7 |                  | phase X step 7     | $\   \text{digital sync phase 1 write}$ |

### PRBS Generator [44]

Author: David Parent

Description: Generates a PRBS signal

GitHub repository

HDL projectMux address: 44

Extra docsClock: 0 Hz

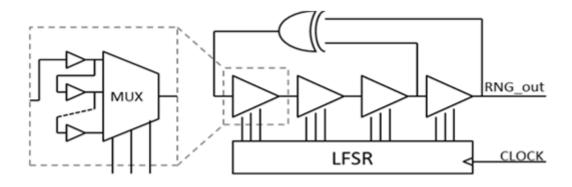

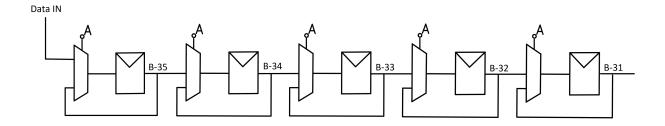

#### How it works

The chip generates a PRBS31 signal using a Fibonacci LFSR and analyzes it with the same structure. The output of the PRBS is taken off the chip and read back in to be analyzed.

Two 7-bit vectors are converted into puedo random signal PSR by comparing the vector to the PRBS. These signals are also output and can be used as an alternative to a PWM DAC. These two PRS are multiplied with an and gate, and the out is sent off-chip. Singal A is squared by delaying it by one clock cycle and anding the signal with the delayed version.

A 131-bit PRBS generator is included as well to fill up the tile as much as possible.

Everything will be documented here:https://docs.google.com/document/d/1nhcHBQsxXUUo1\_

#### How to test

Input Clock and reset

#### **External hardware**

ADALM2000

# Input Output Bidirectional

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 0 | i1    | out1   |               |

| 1 | i2    | out2   |               |

| 2 | i3    | out3   |               |

| 3 | i4    |        |               |

| 4 | i5    |        |               |

| 5 | i6    |        |               |

| 6 | i7    |        |               |

| 7 | i8    |        |               |

# Full-adder out of a kmap [46]

Author: Levi Feldman

• Description: A full-adder made out of a kmap.

GitHub repositoryWokwi projectMux address: 46

Extra docsClock: 0 Hz

#### How it works

It is a straightforward full-adder circuit but it is made directly out of the kmaps for both outputs.

#### How to test

Standard full-adder usage. But the implementation is different though.

#### **External hardware**

None.

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 0 | Α     | SUM    |               |

| 1 | В     | C-OUT  |               |

| 2 | C-IN  |        |               |

| 3 |       |        |               |

| 4 |       |        |               |

| 5 |       |        |               |

| 6 |       |        |               |

| 7 |       |        |               |

|   |       |        |               |

# dEFAULt 2hAC [64]

Author: Beau Ambur

Description: Inverted 7-segment !(tinY tAPeout)

• GitHub repository

Wokwi projectMux address: 64

Extra docsClock: 1 Hz

## How it works

Sequentially spells out a message using the 7-segment display.

#### How to test

Decipher the hidden message by inverting the segments.

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 0 |       | а      |               |

| 1 |       | b      |               |

| 2 |       | С      |               |

| 3 |       | d      |               |

| 4 |       | e      |               |

| 5 |       | f      |               |

| 6 |       | g      |               |

| 7 |       | dot    |               |

## **ECC\_test1** [65]

Author: Dr. Vaibhav Neema

Description: it is use for detecting single bit error

GitHub repositoryWokwi project

• Mux address: 65

Extra docsClock: 0 Hz

#### How it works

The objective of this work is to design a chip module which performs 1-bit error detection and correction in the transmitted encoded data. The proposed design includes three sections: a transmitter, built in self-test block (for testing purposes), and a receiver. The transmitter takes an 8-bit input and generates 4 redundant bits, creating a 12-bit encoded data stream for transmission. The second block is used as built in self-test block(BIST). This block is used to intentionally insert an error during transmission of encoded data to properly test our design. If no error is inserted in the transmitted code word, 4 output pins display the redundant bits. However, If 1-bit error is provided, these pins display the error position. The receiver block can correct any 1-bit error in the received 12-bit data and displays the corrected data as provided at the input side.

#### How to test

This design has 8-input data pins which will use to provide digital input bits, 8 output pins will use to check the output by connectings LED's. Four birectional pins will use as a input ports for BIST and remaining four bidirectional pins will use as output pins to detect the postion of the error.

#### External hardware

Twelve LED's, LED Display, four bit counter, Eight bit counter and Twelve digital input switch

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 0 | IN0   | OUT0   | ttio0:IN      |

| 1 | IN1   | OUT1   | ttio1:IN      |

| 2 | IN2   | OUT2   | ttio2:IN      |

| 3 | IN3   | OUT3   | ttio3:IN      |

| 4 | IN4   | OUT4   | ttio4:OUT     |

| 5 | IN5   | OUT5   | ttio5:OUT     |

| 6 | IN6   | OUT6   | ttio6:OUT     |

| 7 | IN7   | OUT7   | ttio7:OUT     |

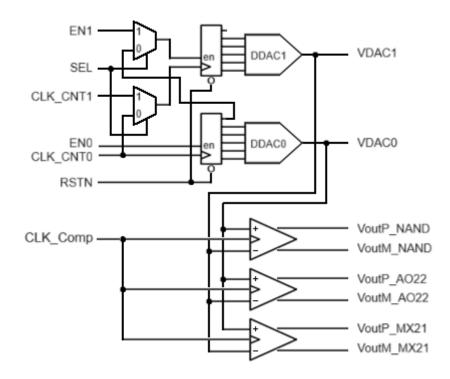

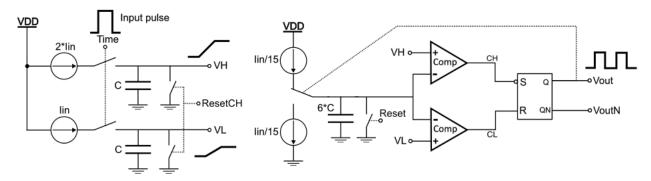

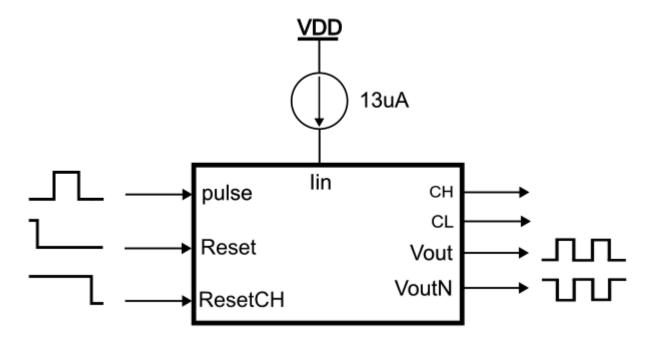

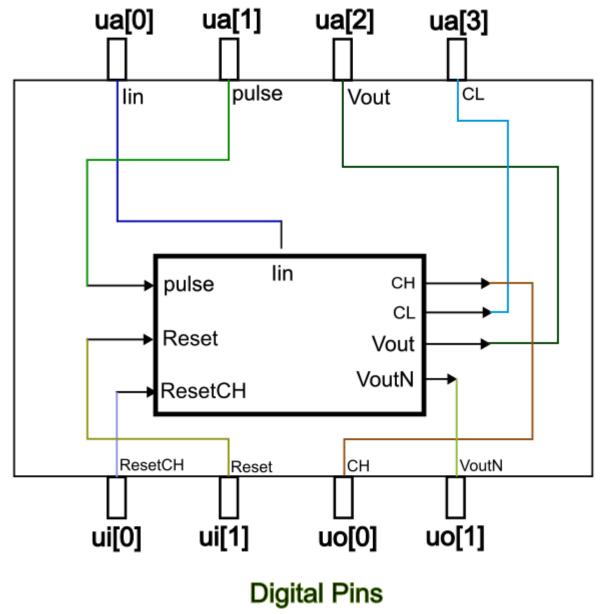

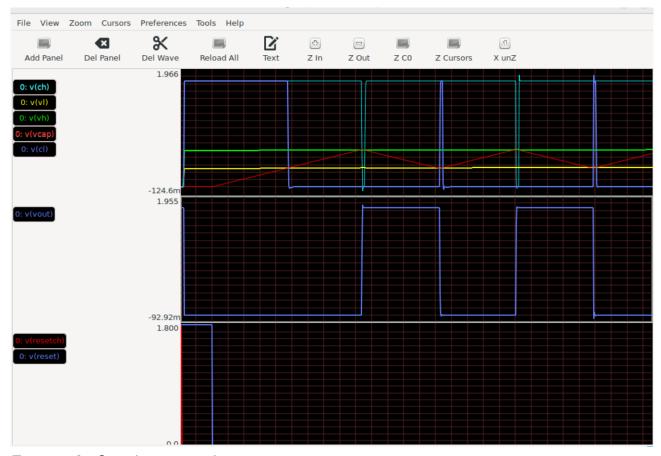

# All Digital DAC and Analog Comparators [66]

Author: Maximiliam Luppe

Description: Implementation of a DAC and three versions of a analog comparator using only standard cells

GitHub repository

HDL projectMux address: 66

Extra docsClock: 0 Hz

#### How it works

This project implements three different analog comparators based on standard logic cells. They are based on work of Sala et al. [1].

Figure 7: Digital DAC and Comparators diagram

Two DACs, based on the work of Yang et al. [2], also implemented using only standard logic cells, with the aid of two 5-bit counters, generate an analog ramp signal to test the comparators.

1. R. D. Sala, C. Bocciarelli, F. Centurelli, V. Spinogatti and A. Trifiletti, "A Novel Ultra-Low Voltage Fully Synthesizable Comparator exploiting

- NAND Gates," 2023 18th Conference on Ph.D Research in Microelectronics and Electronics (PRIME), Valencia, Spain, 2023, pp. 21-24, doi: 10.1109/PRIME58259.2023.10161936

- 2. D. Yang, T. Ueno, W. Deng, Y. Terashima, K. Nakata, A. T. Narayanan, R. Wu, K. Okada, A. Matsuzawa, "A 0.0055mm2  $480\mu$ W Fully Synthesizable PLL Using Stochastic TDC in 28nm FDSOI," IEICE Transactions on Electronics, v. E99.C, no. 6, 2016, pp. 632-640, doi: 10.1587/transele.E99.C.632

#### How to test

The SEL pin alows to select two different test conditions. With SEL=0, both counters work together, generating a 10-bit sequence. For each step in the DAC1, DAC0 generates 32 different voltage levels, from near 0V to near Vcc. With SEL=1, both counters work independently.

#### **External hardware**

It's necessary an osciloscope to visualize the outputs from the DACs and the comparators.

| # | Input                  | Output        | Bidirectional |

|---|------------------------|---------------|---------------|

| 0 | First Counter Clock    | VinP          |               |

| 1 | Second Counter Clock   | VinM          |               |

| 2 | Comparators Clock      | $VoutP_NAND$  |               |

| 3 | First Counter Enable   | $VoutM_NAND$  |               |

| 4 | Second Counter Enable  | VoutP_AO22    |               |

| 5 | Counter Mode Selection | VoutM_AO22    |               |

| 6 |                        | $VoutP\_MX21$ |               |

| 7 |                        | VoutM_MX21    |               |

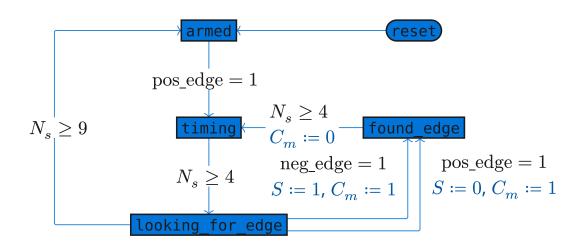

## 443MHz Manchester Decoding [67]

Author: Zachary Kohnen

Description: A manchester decoder and parser for a 433 mhz transmission

GitHub repository

HDL projectMux address: 67

Extra docs

Clock: 20000 Hz

#### How it works

There are 2 state machines. One to decode the manchester encoded signal, and the other to parse the data frames. For the manchester decoding aspect, the following state machine is implemented.

Figure 8: State Diagram

Blue text are side effects of the transitions.  $N_s$  is a counter that increments while in each state, and is reset on each state transition.

The state machine makes use of a delay of 5 cycles in order to ignore any non-data carrying transition.

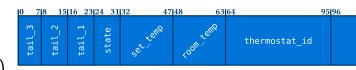

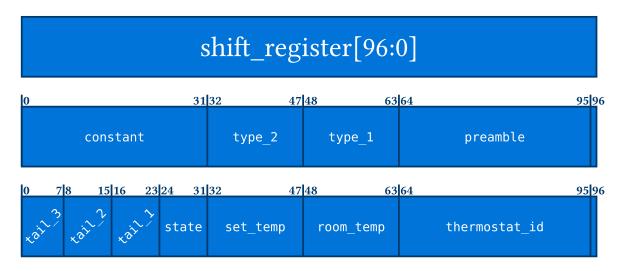

The data sent over the air follows the following format. (bit labels are as the data is

shifted into a shift-register (0 = last bit received))

In order to save space in the design, since the preamble section and data section are of equal length, only half of the message needs to be buffered at a time.

The below diagram shows 2 views into the shift register. The first view is used to validate the existence of a preamble. Once that has been tripped, the system reloads the register with 0x1, and fills the register again until the initial set bit falls into the last (96) place, causing the shift register to halt all loads until it is reset.

#### How to test

Wire the system up, and read out the internal registers through the parallel\_out lines

| Address | Parallel Out         |

|---------|----------------------|

| 0000    | thermostat_id[7:0]   |

| 0001    | thermostat_id[15:8]  |

| 0010    | thermostat_id[23:16] |

| 0011    | thermostat_id[31:24] |

| 0100    | room_temp[7:0]       |

| 0101    | room_temp[15:8]      |

| 0110    | set_temp[7:0]        |

| 0111    | set_temp[15:8]       |

| 1000    | state                |

| 1001    | tail_1               |

| Address      | Parallel Out     |

|--------------|------------------|

| 1010<br>1011 | tail_2<br>tail_3 |

| 1100-1111    | 00000000         |

## **External hardware**

Pin  $\mbox{ui\_in[0]}$  (digital\_in) must be connected to the digital output of a 433MHz receiver

| # | Input      | Output             | Bidirectional      |

|---|------------|--------------------|--------------------|

| 0 | digital_in | parallel_out[0]    | full               |

| 1 |            | $parallel\_out[1]$ | manchester_clock   |

| 2 | halt       | parallel_out[2]    | manchester_data    |

| 3 |            | parallel_out[3]    | transmission_begin |

| 4 | address[0] | parallel_out[4]    | neg_edge           |

| 5 | address[1] | parallel_out[5]    | pos_edge           |

| 6 | address[2] | $parallel\_out[6]$ |                    |

| 7 | address[3] | $parallel\_out[7]$ |                    |

# **Dummy Counter [68]**

Author: Chinmay

• Description: A 16-bit counter

GitHub repository

HDL projectMux address: 68

Extra docsClock: 0 Hz

## How it works

Like a 16-bit counter

#### How to test

Like a 16-bit counter

## **External hardware**

NA

| # | Input    | Output | Bidirectional |

|---|----------|--------|---------------|

| 0 | count_en | b0     | b8            |

| 1 | mult_en  | b1     | b9            |

| 2 | m_a0     | b2     | b10           |

| 3 | m_a1     | b3     | b11           |

| 4 | m_a2     | b4     | b12           |

| 5 | m_b0     | b5     | b13           |

| 6 | m_b1     | b6     | b14           |

| 7 | m_b2     | b7     | b15           |

# MicroCode Multiplier [69]

Author: Neil Powell

• Description: microcode unit for shift and add multiplication

• GitHub repository

HDL projectMux address: 69

Extra docs

■ Clock: 1000 Hz

## How it works

Input two 4-bit numbers A and B. 8-bit product is returned.

#### How to test

Just reset and supply the inputs

#### **External hardware**

Switches and LEDs

| # | Input     | Output     | Bidirectional |

|---|-----------|------------|---------------|

| 0 | inputA[0] | SMP_out[0] |               |

| 1 | inputA[1] | SMP_out[1] |               |

| 2 | inputA[2] | SMP_out[2] |               |

| 3 | inputA[3] | SMP_out[3] |               |

| 4 | inputB[0] | SMP_out[4] |               |

| 5 | inputB[1] | SMP_out[5] |               |

| 6 | inputB[2] | SMP_out[6] |               |

| 7 | inputB[3] | SMP_out[7] |               |

# My 9-year-old son made an 8-bit counter chip [70]

• Author: Kian Dabui

• Description: My 9-year-old son made an 8-bit counter chip following instructions and a picture with a brief explanation.

GitHub repositoryWokwi projectMux address: 70

Extra docsClock: 0 Hz

#### How it works

My 9-year-old son made an 8-bit counter chip following instructions and a picture with a brief explanation.

#### How to test

The output from Q0 to Q7 counts up in binary.

#### **External hardware**

The output from Q0 to Q7 counts up in binary using an LED Pmod.

| # | Input | Output   | Bidirectional |

|---|-------|----------|---------------|

| 0 |       | q0       |               |

| 1 |       | q1       |               |

| 2 |       | q2       |               |

| 3 |       | q3<br>q4 |               |

| 4 |       | q4       |               |

| 5 |       | q5       |               |

| 6 |       | q6       |               |

| 7 |       | q7       |               |

## TT7 Simple Clock [71]

Author: Joseph Hsu

Description: This is a very simple, configurable clock. By default it's 20 MHz, but it can be configured to 10/12/14 Mhz.

GitHub repository

HDL projectMux address: 71Extra docs

Clock: 20000000 Hz

#### How it works

So this clock is configured off of the FPGA clock at 20 MhZ. However, the clock is configurable to different frequencies and settings.

#### How to test

See if the clock works. The first, second, and third switches should speed up/slow down the clock, which can be used to set the clock. The fourth switch is used to go to arduino mode. The fifth, sixth switches should allow you to switch between the minutes display and the hours display respectively. The seventh switch should allow you you to run the clock in 4 segment display mode.

#### **External hardware**

PMOD 2 segment display, possible 4 segment

| # | Input                 | Output | Bidirectional |

|---|-----------------------|--------|---------------|

| 0 |                       |        |               |

| 1 | Clock Option - 10 MHz |        |               |

| 2 | Clock Option - 12 MHz |        |               |

| 3 | Clock Option - 14 MHz |        |               |

| 4 | Arduino Mode          |        |               |

| 5 | Minute Display        |        |               |

| 6 | Hour Display          |        |               |

| # | Input        | Output | Bidirectional |

|---|--------------|--------|---------------|

| 7 | 4 Digit Mode |        |               |

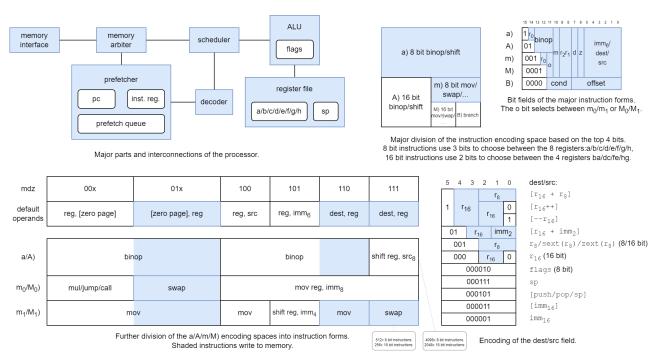

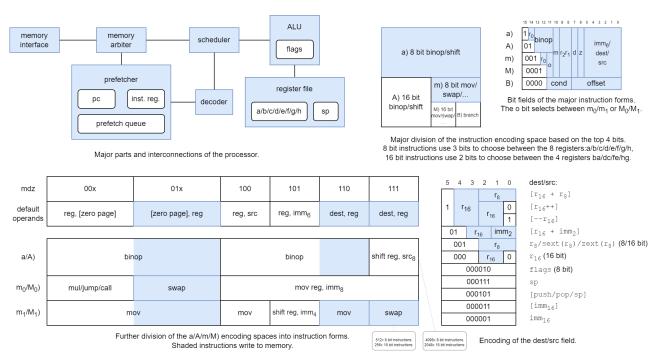

## Basilisc-2816 v0.1c CPU (experimental) [72]

Author: Toivo Henningsson

Description: Small 2-bit serial 8/16 bit CPU

GitHub repository

HDL projectMux address: 72

Extra docs

Clock: 50000000 Hz

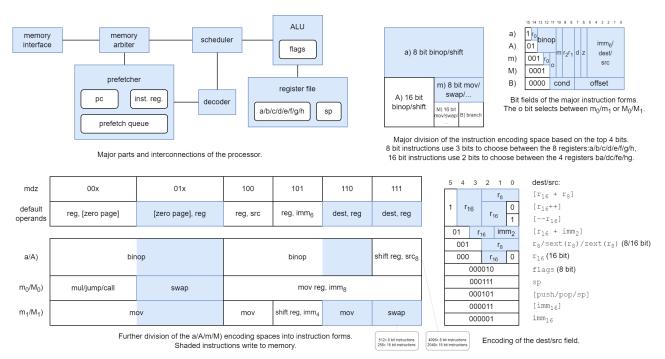

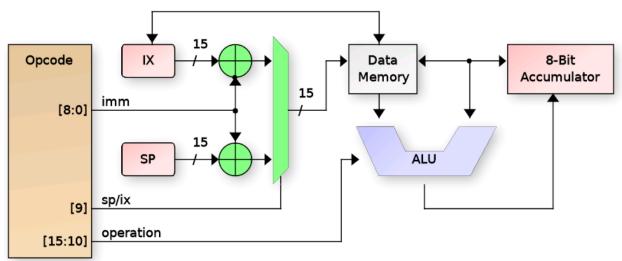

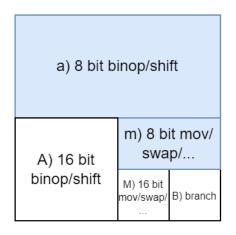

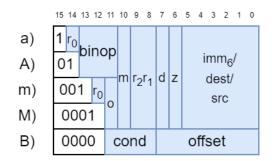

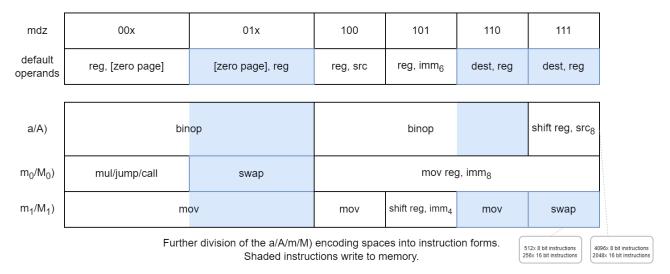

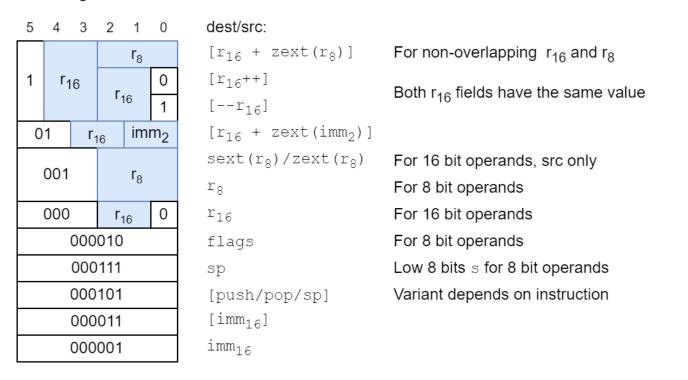

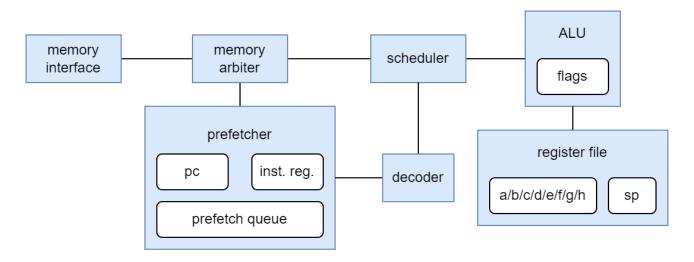

#### Overview

Basilisc-2816 v0.1 is a small 2-bit serial 2/8/16 bit processor that fits into one Tiny Tapeout tile. It has been designed around the constraints of

- small area,

- 4 pin serial memory interface to a RAM emulator implemented in an RP2040 microcontroller (which can be supported by the RP2040 microcontroller on the Tiny Tapeout 7 Demo Board),

- to be suitable to be included in in the next version of the AnemoneGrafx-8 retro console https://github.com/toivoh/tt06-retro-console, which motivates the other constraints.

#### Features:

2-bit serial execution:

- ALU results etc are calculated at 2 bits/cycle

- 2-bit-serial register file with two read/write ports

- Addresses and data are sent to/from memory at 2 bits/cycle

- \* The processor starts to operate on each bit of incoming read data as it arrives

- Saves area compared to processing 8/16 bits per cycle / using a parallel access register file

- No point in calculating faster than the memory interface allows

- 8x 8-bit general purpose registers that can be paired into 4x 16-bit general purpose registers, plus an 8 bit stack register

- 8 bit and 16 bit versions of almost all instructions

- 64 kB address space

- 16 bits/instruction

- Quite regular and orthogonal instruction encoding, most instructions can use most addressing modes

- op reg, src and op src, reg instruction forms

#### Instructions:

- mov, swap

- binop: add/adc/sub/sbc/and/or/xor/cmp/test

- \* for register-to-register also: neg/negc/revsub/revsbc/and\_not/ or not/xor not/not,

- shl/shr/sar/rol/ror with variable or immediate shift count,

- mul: 8x8 and 8x16 bit multiply instructions, producing 2 result bits per cycle like everything else,

- branch cc, offset: relative branch

- st unconditional/call/12 conditions including signed/unsigned comparisons.

- jump/call: absolut direct/indirect jump/call,

- additional functionality through combination with addressing modes, e g, ret = jump [pop]

#### Addressing modes:

- [imm7] / [imm7\*2]: zero page

- -[r16 + imm2]

- -[r16 + r8]

- [r16] with postincrement/predecrement

- [push] / [pop] / [top-of-stack] depending on whether the operand is written/read/modified

- [imm16]

- Sign/zero extension of any 8 bit register as source operand to 16 bit instructions

- imm16 / [imm16] operands supported using extra instruction word

- 2-4 word instruction prefetch queue

#### Basilisc-2816 v0.1 variants

Basilisc-2816 v0.1 has been taped out in three variants for Tiny Tapeout 7:

|       | mul         | Prefetch   | Hardened   | Uses    | Mux     |

|-------|-------------|------------|------------|---------|---------|

|       | instruction | queue size | with       | latches | address |

| v0.1a | yes         | 2          | OpenLane 1 | no      | 967     |

| v0.1b | no          | 3          | OpenLane 2 | no      | 202     |

| v0.1c | yes         | 4          | OpenLane 2 | yes     | 72      |

successively more experimental. Longer prefetch queue should help contribute to better performance, especially with long memory access latencies.

This is the 0.1c version. For more details, see https://github.com/toivoh/tt07-basilisc-2816-cpu/blob/main/docs/info.md or the documentation for Basilisc-2816 v0.1a CPU [967].

| # | Input      | Output       | Bidirectional |

|---|------------|--------------|---------------|

| 0 | rx_in[0]   | tx_out[0]    |               |

| 1 | $rx_in[1]$ | $tx\_out[1]$ |               |

| 2 |            | tx_fetch     |               |

| 3 |            | tx_jump      |               |

| 4 |            |              |               |

| 5 |            |              |               |

| 6 |            |              |               |

| 7 |            |              |               |

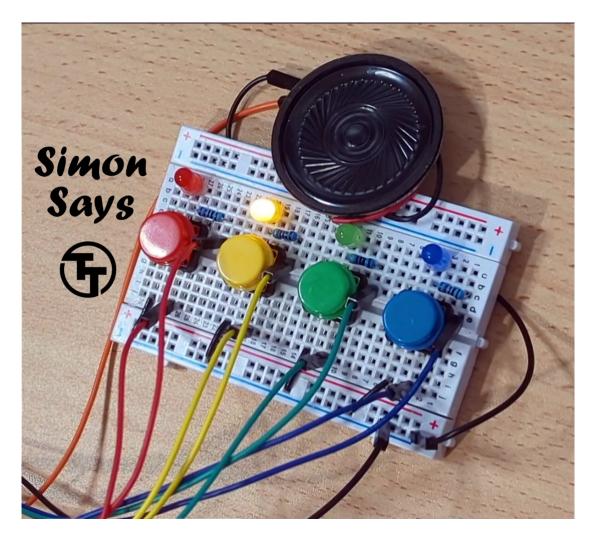

# **SIMON** [73]

• Author: seanyen0

Description: SIMON game

GitHub repository

HDL projectMux address: 73

Extra docs

• Clock: 20000000 Hz

#### How it works

SIMON game. Comes up with sequences of increasing length. User imitates sequence with Digilent PmodBTN. If user loses, 7-segment display shows "L" and user's max number of correct sequences in hex. Upon losing, user can press any button to reset.

#### How to test

Manual reset can be applied by toggling input "in7" high-low.

User needs PmodBTN to enter the guesses.

#### **External hardware**

Digilent PmodBTN plugged into upper row of input header.

| # | Input    | Output | Bidirectional |

|---|----------|--------|---------------|

| 0 | Button 0 | sseg0  |               |

| 1 | Button 1 | sseg1  |               |

| 2 | Button 2 | sseg2  |               |

| 3 | Button 3 | sseg3  |               |

| 4 |          | sseg4  |               |

| 5 |          | sseg5  |               |

| 6 |          | sseg6  |               |

| 7 | Reset    | sseg7  |               |

# VGA Snake Game [74]

Author: Barak Hoffer

• Description: Snake game with vga output

• GitHub repository

HDL projectMux address: 74

Extra docs

■ Clock: 31500000 Hz

#### How it works

A simple snake game with vga output and left,right,up,down buttons.

#### How to test

Connect to a VGA monitor. Change left,right,up,down (ui\_in[0:3]) buttons to change movement.

#### **External hardware**

## TinyVGA PMOD

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 0 | left  | R1     |               |

| 1 | right | G1     |               |

| 2 | up    | B1     |               |

| 3 | down  | VSync  |               |

| 4 |       | R0     |               |

| 5 |       | G0     |               |

| 6 |       | B0     |               |

| 7 |       | HSync  |               |

# Modified Booth Multiplier [75]

Author: Varun Chandra Pendyala

Description: The proposed design multiplies two 8bit signed numbers using modified booth algorithm

GitHub repository

HDL projectMux address: 75

Extra docs

Clock: 100000000 Hz

#### How it works

The project multiplies two 8 bit signed numbers and generates a 16 bit product using Modified Booth Multiplier Algorithm

#### How to test

Two 8-bit signed numbers are fed as input to the multiplier, the multiplier bits are recoded and fed to a dadda multiplier design and the corresponding outputs are added in a carry lookahead adder to get the final 32 bit product

#### **External hardware**

N.A

| # | Input            | Output     | Bidirectional |

|---|------------------|------------|---------------|

| 0 | multiplicand[0]  | product[0] | product[8]    |

| 1 | multiplicand[1]  | product[1] | product[9]    |

| 2 | multiplicand[2]  | product[2] | product[10]   |

| 3 | multiplicand[3]  | product[3] | product[11]   |

| 4 | multiplicand[4]  | product[4] | product[12]   |

| 5 | multiplicand[5]  | product[5] | product[13]   |

| 6 | multiplicand[6]  | product[6] | product[14]   |

| 7 | multiplicand [7] | product[7] | product[15]   |

|   |                  |            |               |

# GDS counter-measures experiment 1 [76]

Author: Aurélien Hernandez

Description: Experiment with GDS-level open-source countermeasure implementation

• GitHub repository

HDL project

• Mux address: 76

Extra docsClock: 0 Hz

#### How it works

PoC of custom hardened macro for fab testing and research purposes. It simply expose a set of customized matrices hardened.

#### How to test

Select one of the two sets of matrices using the MAT\_SEL input. Compare the observated IN -> OUT mapping using the reference model (GDS).

## **External hardware**

Nothing required.

| # | Input        | Output        | Bidirectional |

|---|--------------|---------------|---------------|

| 0 | in_mat_0     | out_mat_0     | mat_sel       |

| 1 | $in\_mat\_1$ | $out\_mat\_1$ |               |

| 2 | in_mat_2     | out_mat_2     |               |

| 3 |              | out_mat_3     |               |

| 4 | in_mat_4     | out_mat_4     |               |

| 5 | in_mat_5     | out_mat_5     |               |

| 6 | in_mat_6     | out_mat_6     |               |

| 7 | in_mat_7     | out_mat_7     |               |

# unisnano [77]

• Author: Maria, Diego, Victor

• Description: UART menu with text output and hardware actions

GitHub repository

HDL project

• Mux address: 77

Extra docs

• Clock: 50000 Hz

#### How it works

A basic UART driver TX and RX is created and waits for the user input as characters (From 1 to 7 with no line ending). If options from 1 to 5 are selected, an informative text is displayed. If options from 6 to 7 are selected, an output bit is toggled

#### How to test

An UART transciever is requiered, using the recommended UART pins RX on #3 and TX on #34. A 50MHZ clock is needed at 115200bps

#### **External hardware**

Two LED's with a MOSFET driver

| # | Input | Output  | Bidirectional |

|---|-------|---------|---------------|

| 0 |       |         |               |

| 1 |       | output1 |               |

| 2 |       | output2 |               |

| 3 | rx    |         |               |

| 4 |       | tx      |               |

| 5 |       |         |               |

| 6 |       |         |               |

| 7 |       |         |               |

# fractran-tt [78]

Author: Jack Leightcap

Description: Hardware implementation of John Conway's estoeric turingcomplete lanugage Fractran

GitHub repository

HDL project

• Mux address: 78

Extra docsClock: 1 Hz

#### How it works

Fractran is an esoteric programming language built around prime factorization.

Fractran programs are lists of positive fractions: e.g.,

$$\frac{17}{91}, \frac{78}{85}, \frac{19}{51}, \frac{23}{38}, \frac{29}{33}, \frac{77}{29}, \dots$$

Execution follows 3 rules:

- 1. The program is given an initial input integer  $n \in \mathbb{N}$ . This is the "accumulator" value.

- 2. To compute the next state,  $n \leftarrow qn$  where  $q \in \mathbb{Q}$  is the first fraction in the program where  $qn \in \mathbb{N}$ .

- 3. Repeat (2) until no such q exists, then halt with output n.

Depending on how terms are represented, (2) is a very simple operating to implement in hardware. The "cheat" is to operate on pre-factored values: for example, the first few fractions of the above example:

$$2^{0}3^{0}5^{0}7^{-1}11^{0}13^{-1}17^{1}, 2^{1}3^{1}5^{-1}7^{0}11^{0}13^{1}17^{-1}, 2^{0}3^{-1}5^{0}7^{0}11^{0}13^{0}17^{-1}19^{1}, 2^{-1}3^{0}5^{0}7^{0}11^{0}13^{0}17^{-1}19^{1}, 2^{-1}3^{0}5^{0}7^{0}11^{0}13^{0}17^{-1}19^{1}, 2^{-1}3^{0}5^{0}7^{0}11^{0}13^{0}17^{-1}19^{1}, 2^{-1}3^{0}5^{0}7^{0}11^{0}13^{0}17^{-1}19^{1}, 2^{-1}3^{0}5^{0}7^{0}11^{0}13^{0}17^{-1}19^{1}, 2^{-1}3^{0}5^{0}7^{0}11^{0}13^{0}17^{-1}19^{1}, 2^{-1}3^{0}5^{0}7^{0}11^{0}13^{0}17^{-1}19^{1}, 2^{-1}3^{0}5^{0}7^{0}11^{0}13^{0}17^{-1}19^{1}, 2^{-1}3^{0}5^{0}7^{0}11^{0}13^{0}17^{-1}19^{1}, 2^{-1}3^{0}5^{0}7^{0}11^{0}13^{0}17^{-1}19^{1}, 2^{-1}3^{0}5^{0}7^{0}11^{0}13^{0}17^{-1}19^{1}, 2^{-1}3^{0}5^{0}7^{0}11^{0}13^{0}17^{-1}19^{1}, 2^{-1}3^{0}5^{0}7^{0}11^{0}13^{0}17^{-1}19^{1}, 2^{-1}3^{0}5^{0}7^{0}11^{0}13^{0}17^{-1}19^{1}, 2^{-1}3^{0}5^{0}7^{0}11^{0}13^{0}17^{-1}19^{1}, 2^{-1}3^{0}5^{0}7^{0}11^{0}13^{0}17^{-1}19^{1}, 2^{-1}3^{0}5^{0}7^{0}11^{0}13^{0}17^{-1}19^{1}, 2^{-1}3^{0}5^{0}7^{0}11^{0}13^{0}17^{-1}19^{1}, 2^{-1}3^{0}5^{0}7^{0}11^{0}13^{0}17^{-1}19^{1}, 2^{-1}3^{0}5^{0}7^{0}11^{0}13^{0}17^{-1}19^{1}, 2^{-1}3^{0}5^{0}7^{0}11^{0}13^{0}17^{0}17^{0}11^{0}117^{0}11^{0}117^{0}11^{0}117^{0}11^{0}117^{0}11^{0}117^{0}11^{0}117^{0}11^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^{0}117^$$

For  $n=825=3^15^211^1$ ,  $nq\in\mathbb{N}$  if all pairwise added prime factor degrees are positive: testing  $825\times\frac{17}{91}$ :

$$3^15^211^1 \times 7^{-1}13^{-1} = 3^15^27^{-1}11^113^{-1}$$

The negative degrees are not cancelled by the terms of n: testing  $825 \times \frac{29}{33}$ ,

$$3^15^211^1 \times 3^{-1}11^{-1}29^1 = 5^229^1$$

All negative degrees cancel, and the result is written as the new accumulator.

#### How to test

See port mapping in info.yaml.

## Encodings:

- accumulator: 8-bit unsigned integer degrees. Value 0b11111111 reserved as sentinel "STOP" value.

- fraction: 8-bit signed (one's complement) degrees. Value 0b11111111 (the "second zero") reserved as sentinel "STOP" value.

Apply to these two inputs pair of streams of prime factor degrees. When the each stream is exhausted, apply the "STOP" value.

For each input, there is output:

- resultant degree, or "STOP" when both input streams exhausted, indicating a positive result and accumulator writeback.

- HALT, when a negative degree is calculuated, indicating the start of the next fraction.

#### External hardware

The logic implemented internally is quite small, requiring support circuitry. This might include:

- 1. fraction counter: program counter

- 2. degree pointer: counter for current prime term

- 3. fraction ROM: storing prime degrees, punctuaed by "STOP"s

- 4. banked accumulator RAM: two banks of memory to store current accumulator, and calculated value. on an integral result, the 'scratch' bank is switched to accumulator, old accumulator becomes 'scratch'.

| # | Input                  | Output                | Bidirectional       |

|---|------------------------|-----------------------|---------------------|

| 0 | accumulator stream [0] | factorized stream [0] | fraction stream [0] |

| 1 | accumulator stream [1] | factorized stream [1] | fraction stream [1] |

| 2 | accumulator stream [2] | factorized stream [2] | fraction stream [2] |

| 3 | accumulator stream [3] | factorized stream [3] | fraction stream [3] |

| 4 | accumulator stream [4] | factorized stream [4] | fraction stream [4] |

| 5 | accumulator stream [5] | factorized stream [5] | fraction stream [5] |

| 6 | accumulator stream [6] | factorized stream [6] | fraction stream [6] |

| 7 | accumulator stream [7] | factorized stream [7] | fraction stream [7] |

## Phase Shifted PWM Modulator [79]

Author: Nelson Salvador & Francisca Donoso

Description: Phase-Shifted Pulse Width Modulation (PS-PWM) that generates the switching signals for 2 PMOS and 2 NMOS from a duty cycle (d1 and d2)

GitHub repository

HDL project

• Mux address: 79

Extra docs

■ Clock: 1000 Hz

#### How it works

The Phase Shifted PWM (PS-PWM) system generates phase-shifted PWM signals used for controlling power converters. The main module orchestrates the process by integrating various submodules. It starts by receiving and assigning inputs, then uses a shift register to process serial data, which determines control signals for selecting clock sources and phase-shifted triangular waveforms. These waveforms are generated by dedicated modules for different phases (0, 90, 180, and 270 degrees). The system selects the appropriate phase for two channels and compares these waveforms with input data to produce raw PWM signals. Dead time generators add configurable delays to these signals to prevent transistor cross-conduction. Finally, an output multiplexer and enable control ensure the PWM signals are correctly outputted based on enable signals, producing the desired PS-PWM output.

#### How to test

## 1. Initial Setup

## Connect Power Supply:

- Ensure the module is powered correctly.

## Clock Signal:

Connect a function generator to the clk input.

## Control Signals:

- Connect switches or signal sources for rst\_n, CLK\_SR, and data\_SR.

## Inputs:

Connect ui\_in and uio\_in to signal sources like DIP switches or a microcontroller.

#### 2. Reset the Module

#### Procedure:

- Set rst\_n to low to reset the module.

- Observe the module's outputs to confirm they reset.

- Set  ${\tt rst\_n}$  to high to release the reset.

## 3. Shift Data into the Shift Register

#### Procedure:

- Set data\_SR to the first bit of your 11-bit data (1 or 0).

- Pulse CLK\_SR high, then low to clock in the bit.

- Repeat for each bit in your data sequence (e.g., 11'b00011001101. Sequentially input each bit representing dt[0] to dt[4], SELECTOR\_SIGNAL\_GENERATOR\_1[0], SELECTOR\_SIGNAL\_GENERATOR\_1[1], SELECTOR\_SIGNAL\_GENERATOR\_2[0], SELECTOR\_SIGNAL\_GENERATOR\_2[0], and OUTPUT\_SELECTOR\_EXTERNAL[2] into the data\_SR input. For each bit, you set data\_SR to the corresponding value (1 or 0) and toggle CLK\_SR high, then low, to clock in the bit. This sequential shifting ensures that each data\_out corresponds to the specified comment name within the Shift\_Register module.).

## 4. Configure ui\_in and uio\_in (example, 20% duty cycle)

#### Procedure:

- Set ui\_in to 11010000 to set d1 = 13 (d1 and d2 are 6 bit length, so 13/64 is about 20%).

- Set  $uio_in[3:0]$  to 1101 to set part of d2 = 13.

## 5. Monitor Outputs

#### Procedure:

- Use an oscilloscope or logic analyzer to check uo\_out signals.

- Verify the PWM signals on uo\_out[0] (PMOS1), uo\_out[1] (NMOS2), uo\_out[2] (PMOS2), uo\_out[3] (NMOS1), and the clock signal on uo\_out[4].

- Confirm the PWMs duty cycle matches the expected 20%.

## **External hardware**

There is no need of external hardware.

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 0 | d1[0] | PMOS1  | d2[2]         |

| 1 | d1[1] | NMOS2  | d2[3]         |

| 2 | d1[2] | PMOS2  | d2[4]         |

| 3 | d1[3] | NMOS1  | d2[5]         |

| 4 | d1[4] | clk_in | CLK_SR        |

| 5 | d1[5] |        | Data_SR       |

| 6 | d2[0] |        | CLK_EXT       |

| 7 | d2[1] |        |               |

|   |       |        |               |

# 4bit\_CPU\_td4 [128]

Author: Ko KosugiDescription: 4bit\_CPU

GitHub repository

HDL project

■ Mux address: 128

Extra docsClock: 10 Hz

#### How it works

4-bit CPU with 4 input ports and 4 output ports.

#### How to test

Set the inputs and check the outputs.

#### **External hardware**

List external hardware used in your project (e.g. PMOD, LED display, etc), if any

| # | Input  | Output       | Bidirectional |

|---|--------|--------------|---------------|

| 0 | data_0 | addres_0     | IO_0          |

| 1 | data_1 | addres_1     | IO_1          |

| 2 | data_2 | addres_2     | IO_2          |

| 3 | data_3 | addres_3     | IO_3          |

| 4 | data_4 | cf           | 0             |

| 5 | data_5 | ALU_to_reg_0 | ALU_to_reg_3  |

| 6 | data_6 | ALU_to_reg_1 | select_0      |

| 7 | data_7 | ALU_to_reg_2 | select_1      |

# **DVD** Screensaver with Tiny Tapeout Logo (Tiny VGA) [130]

Author: Uri Shaked

Description: Tiny Tapeout Logo bouncing around the screen (640x480 VGA)

GitHub repository

HDL project

Mux address: 130

Extra docs

Clock: 25175000 Hz

#### How it works

Displays a bouncing Tiny Tapeout logo on the screen.

Figure 9: Tiny Tapeout screensaver

#### How to test

Connect to a VGA monitor. Set the following inputs to configure the design:

- tile (ui\_in[0]) to repeat the logo and tile it across the screen,

- color (ui\_in[1]) to enable color output.

# External hardware

# TinyVGA PMOD

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 0 | tile  | R1     |               |

| 1 | color | G1     |               |

| 2 |       | B1     |               |

| 3 |       | VSync  |               |

| 4 |       | R0     |               |

| 5 |       | G0     |               |

| 6 |       | B0     |               |

| 7 |       | HSync  |               |

## Ripple Carry Adder 8 bit [132]

Author: Jason Kaufmann

Description: Adds two 8 bit numbers together

GitHub repository

HDL project

• Mux address: 132

Extra docsClock: 0 Hz

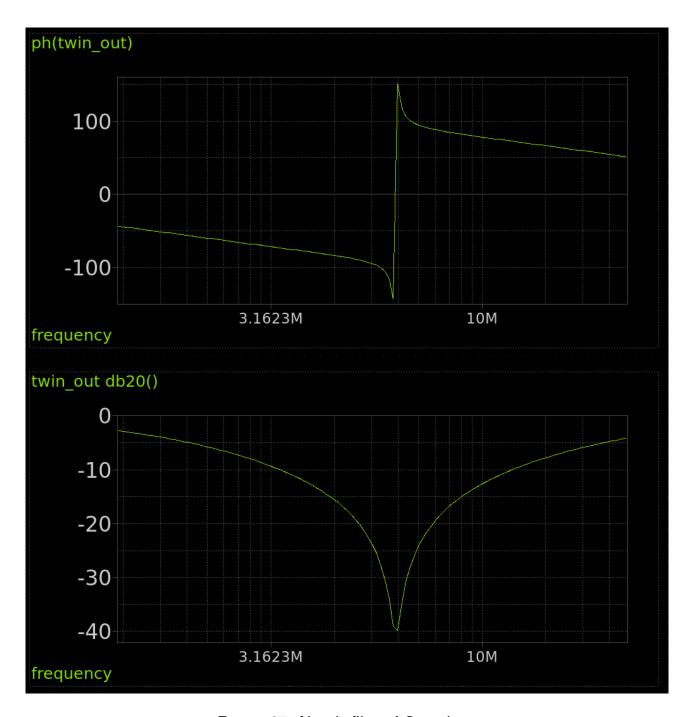

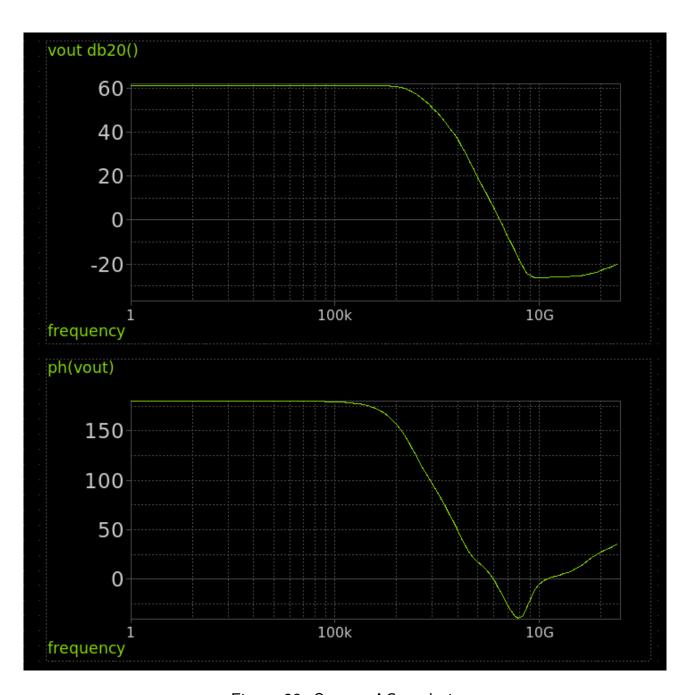

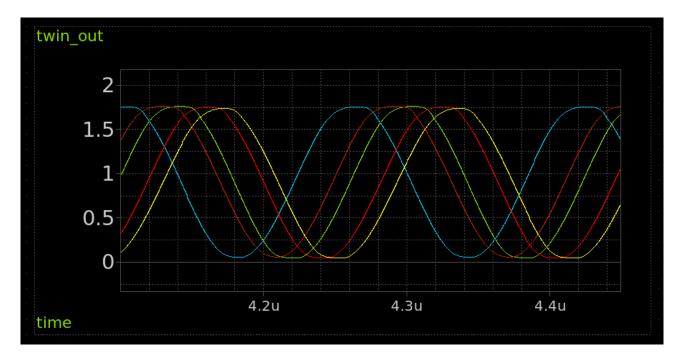

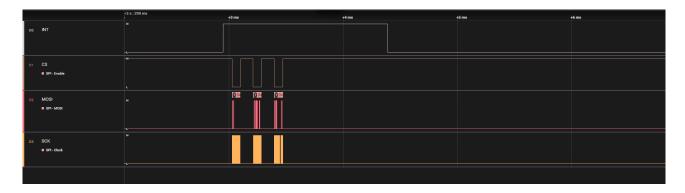

#### How it works