# **Tiny Tapeout 9 Datasheet**

### Project Repository https://github.com/TinyTapeout/tinytapeout-09

January 12, 2025

Contents

### Chip map

| Projects                                                                                                  | 15   |

|-----------------------------------------------------------------------------------------------------------|------|

| Chip ROM [0]                                                                                              | . 15 |

| TinyTapeout Factory Test $1 \ldots \ldots$ | . 17 |

| Trubick - Tiny Tapeout Logic Gate 2                                                                       | . 19 |

| Andrew Vo - Repository [3]                                                                                |      |

| tinytapeout [4]                                                                                           | . 21 |

| $Half \; adder \; [5]  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $          |      |

| Samson's Tiny Tapout Project [6]                                                                          | . 23 |

| Jacks First Project [7]                                                                                   |      |

| 4 x 4 array multiplier NuKoP [8]                                                                          |      |

| MuxLED [9]                                                                                                |      |

| Tiny Tapeout [10]                                                                                         |      |

| halfadder+not [11]                                                                                        |      |

| Yohan Tiny Tapeout Project [12]                                                                           |      |

| 4-bit Multiplier [13]                                                                                     | . 32 |

| Yared Fente's Tiny Tapeout [14]                                                                           |      |

| Metastable Chip [15]                                                                                      |      |

| Secret Initial [32]                                                                                       |      |

| Binary to 7 Segment Display Decoder [33]                                                                  |      |

| Tahiti [34]                                                                                               |      |

| Letter H [35]                                                                                             |      |

| APTT [36]                                                                                                 |      |

| Two PFD [37]                                                                                              |      |

| Zero to Nine Display Count [38]                                                                           |      |

| Redco [39]                                                                                                |      |

| Light LED [40]                                                                                            |      |

| Matmul System [41]                                                                                        |      |

| Tiny Tapeout-Huerta [42]                                                                                  |      |

| Light [43]                                                                                                |      |

| TinyTapeOut [44]                                                                                          |      |

| Nathan's chip [45]                                                                                        |      |

| OR gate [46]                                                                                              |      |

| project [47]                                                                                              |      |

| D_flipflop_hold_test [64]                                                                                 |      |

| Dipankar's first Wowki design [65]                                                                        |      |

| Bit Counter [66]                                                                                          |      |

| Hamad's design [67]                                                                                       |      |

| Full bit adder [68]                                                                                       |      |

| Encoder [69]                                                                                              |      |

| Encoder [70]                                                                                              |      |

12

| GDS [71]                                                                    | 63  |

|-----------------------------------------------------------------------------|-----|

| Big J's Big Circuit [72]                                                    | 64  |

| 2 Bit Times 2 Bit Plus 4 Bit MAD and 5 Bit Binary to 7 Segment Display [73] | 65  |

| AndLogicPass [74]                                                           | 67  |

| Not Good BCD Decoder [75]                                                   | 68  |

| Half Adder [76]                                                             | 69  |

| tinytapeoutkr [77]                                                          | 72  |

| Jordan [78]                                                                 | 73  |

| My First ASIC [79]                                                          | 74  |

| GJAA Design [96]                                                            | 75  |

| 8b10b decoder and multiplier [97]                                           | 76  |

| Logic Gates [98]                                                            | 78  |

| Test Design 1 [99]                                                          | 79  |

| My First TinyTapeout [100]                                                  | 81  |

| Decimation Filter for Incremental and Regular Delta-Sigma Modulators [101]  | 83  |

| 1st [102]                                                                   | 86  |

| adder-accumulator [103]                                                     | 87  |

| JCB First WOKWI Design [104]                                                | 93  |

| ECE 298A 8-Bit CPU Control Block [105]                                      | 94  |

| Logic Gates 7-Segment Display [106]                                         | 98  |

| LFSR Encrypter [107]                                                        | 99  |

|                                                                             | 100 |

|                                                                             | 102 |

|                                                                             | 103 |

|                                                                             | 104 |

|                                                                             | 107 |

| ece2204_4x4_mult [129]                                                      |     |

| my_4bit_multiplier [130]                                                    |     |

| T3 (Tiny Ternary Tapeout) [131] $\ldots$                                    |     |

| Hybrid_Adder_8bit [132]                                                     |     |

| 3 Neuron ALIF [133]                                                         |     |

| 8-bit Carry Look-Ahead Adder [134]                                          |     |

| 2bit adder [135]                                                            |     |

| RISC-V Mini [136]                                                           |     |

| 4-1 mux [137]                                                               |     |

| 8-bit carry-skip [138]                                                      |     |

| STDP Circuit [139]                                                          |     |

| 4 bit array multiplier [140]                                                |     |

| instrumented_ring_oscillator [141]                                          |     |

| Array Multiplier [142]                                                      |     |

| Linear Feedback Shift Register [143]                                        |     |

| Frequency Encoder and Decoder [160]                                         |     |

|                                                                             | 140 |

| TT Test [161]                               | 142 |

|---------------------------------------------|-----|

| carry skip adder [162]                      |     |

| 4-bit up/down binary counter [163]          | 145 |

| xor gate with registered output [164]       | 147 |

| Team 17's 8 bit DAC [165]                   | 149 |

| Multi-LFSR [166]                            |     |

| ECE2204MultiplierProject [167]              |     |

| Micro tile container [168]                  |     |

| 4bit multiplier [169]                       |     |

| Forward Pass Network for Simple ANN [170]   |     |

| Tiny Registers [171]                        |     |

| 7-Segment Byte Display [172]                |     |

| Leaky Integrate Fire Neuron [173]           |     |

| znah_vga_ca [174]                           |     |

| Tiny Tapeout Group 7 Lab D [175]            |     |

| 4-bit Multiplier [192]                      | 174 |

| FIREngine [193]                             |     |

| 4x4multiplier [194]                         |     |

| Lab B Group 1 Array Multiplier [195]        |     |

| 4-bit Multiplier [196]                      |     |

| Array Multiplier [197]                      | 184 |

| 4x4 Multiplier [198]                        |     |

| 4x4 Array Multiplier [199]                  |     |

| tt09 kathyhtt [200]                         |     |

| 4x4 Array Multiplier [201]                  | 193 |

| TINY TAPE OUT [202]                         |     |

| ECE2204 4x4 Array Multiplier [203]          | 197 |

| TinyTapeout1 [204]                          |     |

| comparator [205]                            | 201 |

| FB GDS [206]                                |     |

| 4x4 Array Multiplier [207]                  | 203 |

| Semana UCU Verilog [224]                    | 206 |

| 4 by 4 Array Multiplier [226]               | 212 |

| 4-bit multiplier [228]                      | 215 |

| OpenRAM SRAM macro [229]                    | 218 |

| Array Multiplier [230]                      |     |

| VGA Pride [231]                             | 222 |

| 4-bit Array Multiplier [232]                | 226 |

| Noise test for a CDAC capacitor chain [233] | 229 |

| ECE-UY 2204 4x4 Array Multiplier [234]      | 230 |

| Analog Switch [235]                         |     |

| array_multiplier [236]                      | 235 |

| Digital OTA [237]                                             | 238 |

|---------------------------------------------------------------|-----|

| 8-bit-CARRY_SKIP [238]                                        | 240 |

| Telephone hybrid [239]                                        |     |

| Array Multiplier [256]                                        |     |

| Array multiplier [258]                                        |     |

| Array Multiplier [260]                                        |     |

| 1bit_am_sdr [261]                                             | 253 |

| Array Multiplier [262]                                        | 257 |

| Time to Digital Converter [263]                               | 260 |

| Delta RNN and Leaky Integrate-and-Fire Nueron Circuit [264]   | 266 |

| tt_um_tim2305_adc_dac [265]                                   | 268 |

| Verilog ring oscillator [266]                                 | 270 |

| 2-bit Flash ADC [267]                                         | 271 |

| Adaptive Leaky Integrate and Fire Neuron [268]                | 273 |

| pll [269]                                                     | 275 |

| Matmul System [270]                                           | 277 |

| Analog MUX module [271]                                       | 278 |

| Steven's Wokwi Test [288]                                     | 280 |

| 2-Bit-Adder [289]                                             | 281 |

| 8-Bit CPU [290]                                               | 282 |

| fulladder [291]                                               | 298 |

| RLE Video Player [292]                                        | 299 |

| Hopfield Network with Izhikevich-type RS and FS Neurons [293] | 302 |

| 4-bit Multiplier [294]                                        | 303 |

| Perceptron [295]                                              | 306 |

| Histogramming [296]                                           | 307 |

| test_friday2 [297]                                            | 310 |

| Perceptron Neuron [298]                                       | 314 |

| carry_select [299]                                            | 316 |

| I2C and SPI [300]                                             |     |

| Lab C 4x4 Mult-Array [301]                                    |     |

| Configurable Logic Block [302]                                |     |

| Tiny RAM DFF 2r1w [303]                                       |     |

| ECE-2204 4x4 Array Multiplier [320]                           | 328 |

| Senol Gulgonul tt09 [321]                                     |     |

| ECE2204 4x4 Array Multiplier [322]                            | 331 |

| Space Detective Maze Explorer [323]                           |     |

| Array Multiplier [324]                                        | 336 |

| Hamming Code (7,4) [325]                                      |     |

| ece2204 project for tapeout [326]                             |     |

| tiny-tapeout-8bit-GPTPrefixCircuit [327]                      |     |

| 4x4 array multiplier [328]                                    | 351 |

| LIF on a Ring Topology [329]                                             | 354 |

|--------------------------------------------------------------------------|-----|

| 4-bit-array-multiplier [330]                                             |     |

| Delta-Sigma ADC Decimation Filter [331]                                  | 359 |

| Array_Multiplier [332]                                                   | 360 |

| an lfsr with synaptic neurons (excitatory or inhibitatory) [333]         | 362 |

| Generador PWM multiproposito con frecuencia y ciclo de trabajo modulable |     |

| [334]                                                                    | 364 |

| Perceptron [335]                                                         | 366 |

| 2_bit_7seg [416]                                                         | 367 |

| Adbe_Project [417]                                                       | 368 |

| 8 bit LFSR [418]                                                         | 369 |

| Odd or even [419]                                                        |     |

| Broken Two Bit Adder [420]                                               |     |

| Manchester Encoder [421]                                                 | 372 |

| 4 bit adder [422]                                                        | 373 |

| Tiny_Tapeout_Adder! [423]                                                | 374 |

| TinyTapeout workshop - Wokwi 8 Bit LFSR [424]                            | 375 |

| Morse Code for J and R [425]                                             | 376 |

| 3bitFullAdder [426]                                                      | 377 |

| XorTree [427]                                                            | 378 |

| Sigma-Delta ADC [428]                                                    | 379 |

| tt09-4bit-adder-dhags [429]                                              | 381 |

| Mini-Adder and Clock Divider [430]                                       | 382 |

| 7-seg display checker [431]                                              | 383 |

| Drew's First Wokwi Design [448]                                          | 384 |

| Shadoff Test [449]                                                       | 385 |

| Pseudo Random Generator Using 2 Ring Oscillators [450]                   | 387 |

| Tiny Tapeout Take 2 [451]                                                | 388 |

| JonsFirstTapeout [452]                                                   | 389 |

| Speller [453]                                                            | 390 |

| And Gates that don't do much [454]                                       | 391 |

| RAYS FIRST TAPEOUT rev 2 [455]                                           | 392 |

| SimplePattern [456]                                                      | 393 |

| 6 Bit shift register [457]                                               | 395 |

| sphereinabox hello [458]                                                 | 396 |

| Duffy [459]                                                              | 397 |

| Input Counter [460]                                                      | 398 |

| Will It NAND? [461]                                                      | 399 |

| 4 bit ALU [462]                                                          | 400 |

| Bad Logic [463]                                                          | 402 |

| Full Adder [481]                                                         |     |

| 2048 sliding tile puzzle game (VGA) [482]                                | 404 |

| TT-Farhad [483]                                             | 406 |  |  |

|-------------------------------------------------------------|-----|--|--|

| Four Bit Adder [485]                                        |     |  |  |

| SPI Logic Analyzer with Charlieplexed Display [486]         |     |  |  |

| 2 bit adder [487]                                           | 410 |  |  |

| pio-ram-emulator example: Julia fractal [488]               |     |  |  |

| AND and NOT gate testing [489]                              |     |  |  |

| Analog 8 bit 3.3v R2R DAC [490]                             | 415 |  |  |

| Kanoa's first Wokwi deseign Tinytapeout 2024 Nonsense [491] |     |  |  |

| Ring Oscillators [492]                                      |     |  |  |

| add it [493]                                                |     |  |  |

| AMS Chip ITS [494]                                          |     |  |  |

| one [495]                                                   | 423 |  |  |

| SIC-1 8-bit SUBLEQ Single Instruction Computer [518]        | 424 |  |  |

| 4-bit R2R DAC [520]                                         | 427 |  |  |

| Dickson Charge Pump [522]                                   |     |  |  |

| Analog double inverter [524]                                |     |  |  |

| OpAmp 3stage [526]                                          |     |  |  |

| Counter [544]                                               | 437 |  |  |

| Shifter [545]                                               |     |  |  |

| 7-bit arbiter [546]                                         |     |  |  |

| NAND Flip-Flop [547]                                        | 440 |  |  |

| LCA's first Wokwi design [548]                              | 441 |  |  |

| chip [549]                                                  |     |  |  |

| Tinysynth [550]                                             |     |  |  |

| rhTinyTapeout [551]                                         |     |  |  |

| half adder [552]                                            | 445 |  |  |

| rand [553]                                                  | 446 |  |  |

| Tiny Tapeout 9 Template [554]                               | 447 |  |  |

| Ripple counter [555]                                        | 448 |  |  |

| four flip flops [556]                                       | 449 |  |  |

| adder-tt09 [557]                                            | 450 |  |  |

| Full Adder [558]                                            | 452 |  |  |

| NAND-Equ [559]                                              | 453 |  |  |

| Elevator Design [576]                                       | 454 |  |  |

| L display [578]                                             |     |  |  |

| S-R latch [580]                                             | 457 |  |  |

| Gabe's Big AND [582]                                        | 458 |  |  |

| Secret Code [584]                                           | 459 |  |  |

| joes-first-tiny-tapeout [586]                               |     |  |  |

| Abey's 1st Chip Design [588]                                |     |  |  |

| patrick's project [590]                                     |     |  |  |

| tt09-pettit-wokproc-trainer [591]                           |     |  |  |

| Full adder Design [608]                                     |

|-------------------------------------------------------------|

| seven [609]                                                 |

| Vincent's First Design [610]                                |

| gatesoup [611]                                              |

| A Tale of Two NCOs [612]                                    |

| Tiny Tapeout 9 Template Version 1 Tata Luka [613]           |

| Workshop demo [614]                                         |

| UART TX [615]                                               |

| LRC - Longitudinal Redundancy Check generator [616]         |

| my First WokWi Design [617]                                 |

| print [618]                                                 |

| Tiny Tapeout 9 [619]                                        |

| hello [620]                                                 |

| tinydsp-lol [621]                                           |

| Full Adder [622]                                            |

| Leaky integrate and fire spiking neural network [623]       |

| Stochastic Integrator [640]                                 |

| E2M0 x INT8 Systolic Array [642]                            |

| VGA Nyan Cat [644]                                          |

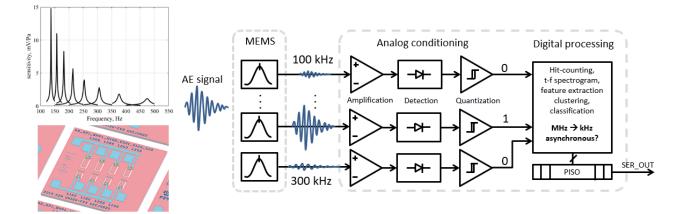

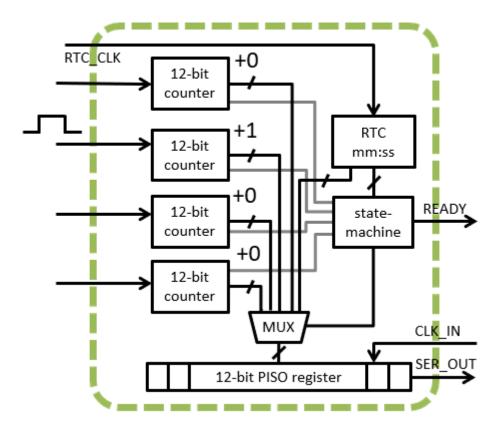

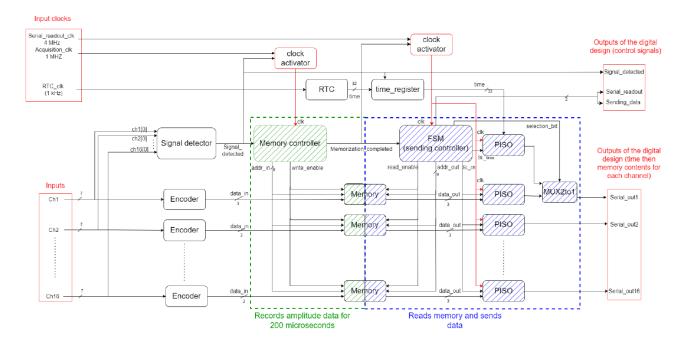

| 15 channels emission counter [646]                          |

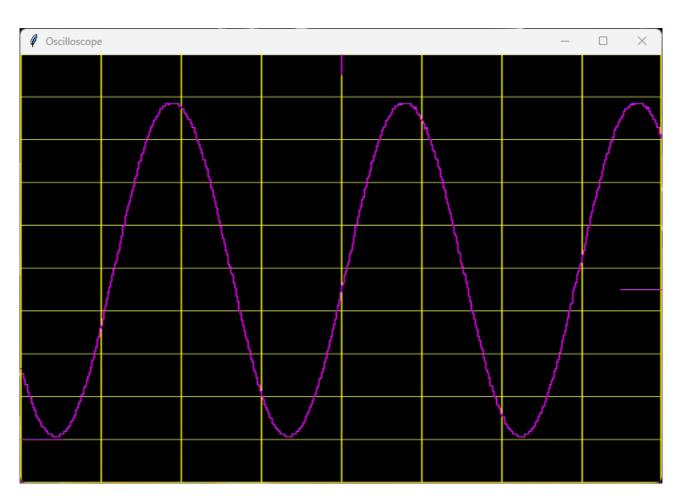

| Basic Oszilloscope and Signal Generator [648]               |

| T3 (Tiny Ternary Tapeout) CSA [650]                         |

| CORA-16 [652]                                               |

| ITS-RISCV [654]                                             |

| 16 Bit Izhikevich Neuron [672]                              |

| Giant Ring Oscillator (3853 inverters) [673]                |

| dff_mem [674]                                               |

| Lab B Group 10 Array Multiplier [675]                       |

| Verilog ring oscillator V2 [676]                            |

| TwoChannelSquareWaveGenerator [677]                         |

| Basic model for Systollic array implementation of LIF [678] |

| RGB Mixer demo [679]                                        |

| mips.sv [680]                                               |

| VGA clock [681]                                             |

| gta6 [682]                                                  |

| 8-bit CBILBO [683]                                          |

| Name Speller [684]                                          |

| Michaels Tiny Tapeout ALU [685]                             |

| 2-bit Full Adder [686]                                      |

| ovl abc chip [687]                                          |

| Simon's Caterpillar [704]                                   |

| tt6502 [706]                                                |

| Oscillating Bones [708]                                        | . 544 |

|----------------------------------------------------------------|-------|

| SoCET UART with FIFO buffers [710]                             |       |

| VGA Drop (audio/visual demo) $[712]$                           |       |

| Warp [714]                                                     |       |

| Sequential Shadows [TT08 demo competition] [716]               |       |

| achasen workshop validation [718]                              |       |

| 7-Segment Digital Desk Clock [736]                             |       |

| TinySnake [737]                                                |       |

| Basic Perceptron + ReLU [738]                                  |       |

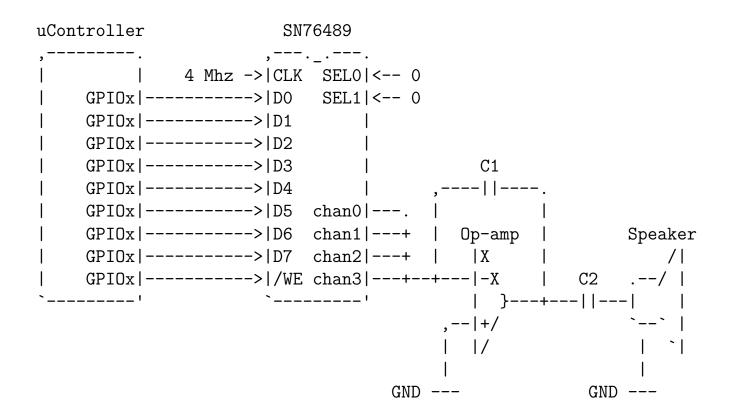

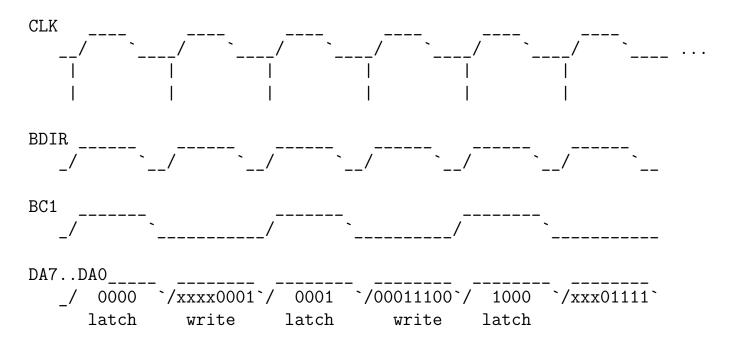

| Classic 8-bit era Programmable Sound Generator SN76489 [739]   |       |

| Basic Matrix-Vector Multiplication [740]                       |       |

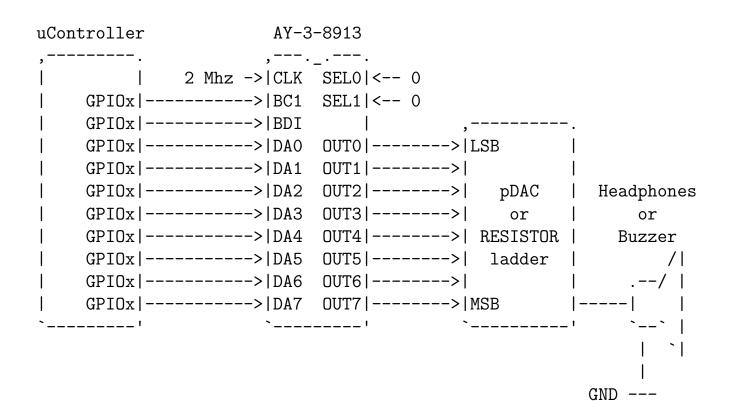

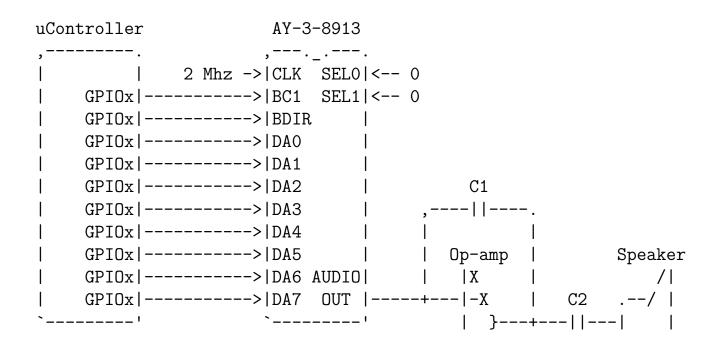

| Classic 8-bit era Programmable Sound Generator AY-3-8913 [741] |       |

| 8 bit MAC Unit [742]                                           |       |

| Cgates [743]                                                   |       |

| Programmable PWM Generator [744]                               |       |

| eksdee [745]                                                   |       |

| Verilog test project [746]                                     |       |

| ternary, E1M0, E2M0 decoders [747]                             |       |

| Basic LIF Neuron [748]                                         |       |

| Dynamic Threshold Leaky Integrate-and-Fire [749]               |       |

| Integrate-and-Fire Neuron Circuit [750]                        |       |

| tt09-C6-array-multiplier [751]                                 |       |

| Zilog Z80 [770]                                                |       |

| Spectrogram extractor, 2 channels [782]                        |       |

| Encoder [800]                                                  |       |

| chip_fab [801]                                                 | . 608 |

| Clocked Display [802]                                          | . 609 |

| YoshiTP [803]                                                  |       |

| A simple leaky integrate and fire neuron [804]                 | . 612 |

| Who knows what's happening Tiny Tapeout [805]                  | . 614 |

| VGA Tiny Logo (1 tile) [806]                                   | . 615 |

| Tiniest of tapeouts [807]                                      | . 616 |

| SK Test Workshop [808]                                         | . 617 |

| Tian TT9 [809]                                                 | . 618 |

| 2-bit 2x2 Matrix Multiplier [810]                              | . 619 |

| RISCV Processor Design [811]                                   |       |

| Verilog ring oscillator V3 [812]                               |       |

| Test_project [813]                                             | . 624 |

| 4-Bit Toy CPU [814]                                            |       |

| RISCV Processor Design [815]                                   |       |

| APA102 to WS2812 Translator [832]                              | . 629 |

| Collatz conjecture brute-forcer [834]                          |       |

| TT09 SKY130 ROM Test [836]                                                                             | . 633 |

|--------------------------------------------------------------------------------------------------------|-------|

| TT09 SKY130 ROM Test (no LVT variant) [838]                                                            | . 635 |

| PID Controller [840]                                                                                   |       |

| Frequency Counter SSD1306 OLED [842]                                                                   |       |

| Basys 3 Over UART Link [844]                                                                           |       |

| Tiny 1-bit AM Radio [846]                                                                              |       |

| Encoder [864]                                                                                          |       |

| dummy [865]                                                                                            | . 648 |

| First Tapeout Chip - OCR [866]                                                                         | . 649 |

| sarah's first chip [867]                                                                               |       |

| Half Adder [868]                                                                                       | . 652 |

| tiny cipher 4 bit key [869]                                                                            | . 653 |

| Kai's Death Adder [870]                                                                                | . 654 |

| 2 input multiplexor [871]                                                                              | . 655 |

| Kevin Project [872]                                                                                    |       |

| Tutorial: Simple LIF Neuron [873]                                                                      | . 657 |

| Leaky Neuron Network [874]                                                                             |       |

| Neuromorphic Hardware for SNN LSTM [876]                                                               |       |

| Project [878]                                                                                          |       |

| Hardware UTF Encoder/Decoder [897]                                                                     |       |

| BINCounterAndGates [899]                                                                               |       |

| Color Bars [901]                                                                                       |       |

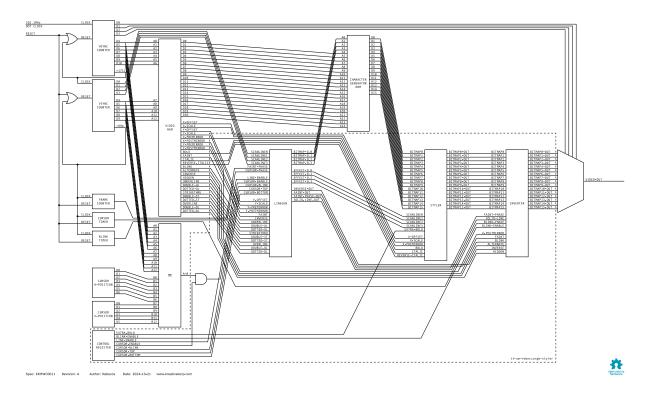

| Fuzzy Search Engine [903]                                                                              |       |

| TT09Ball GDS Art [905]                                                                                 |       |

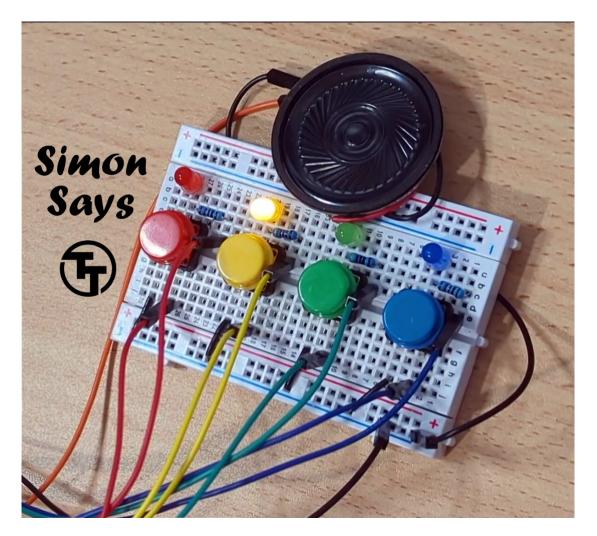

| Simon Says memory game [907]                                                                           |       |

| TT09Ball VGA Screensaver [909]                                                                         | . 688 |

| ChatGPT-generated Spiking Neural Network with Delays [910]                                             |       |

| 32x8 LED Matrix Animation [911]                                                                        |       |

| 8b10b decoder and multiplier [961]                                                                     |       |

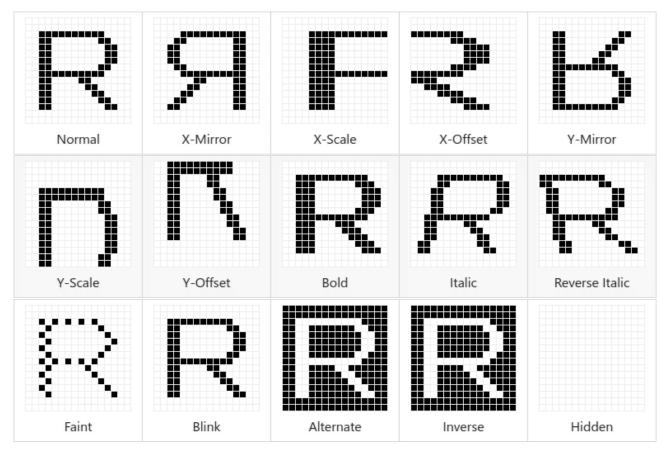

| Styler [963] $\ldots$ |       |

| VGA Timing Experiments [965]                                                                           | . 701 |

| Universal Binary to Segment Decoder [967]                                                              |       |

| INTERCAL ALU [969]                                                                                     |       |

| Simple PWM Module [971]                                                                                |       |

| freqSweep [973]                                                                                        |       |

| Atari 2600 [974]                                                                                       |       |

|                                                                                                        | . 125 |

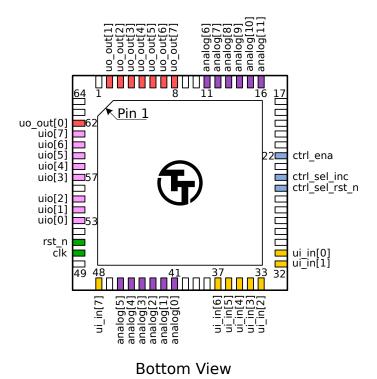

| Pinout                                                                                                 | 728   |

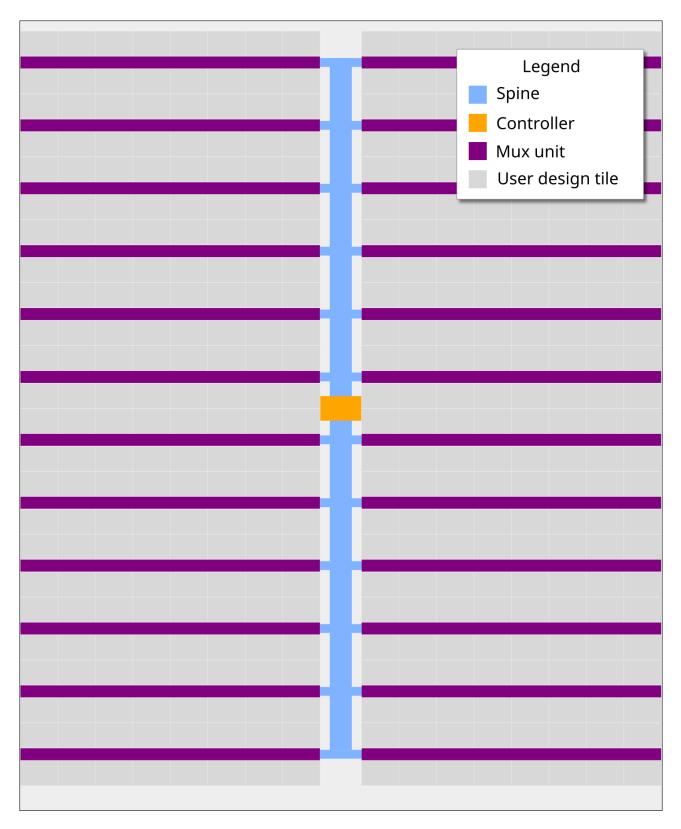

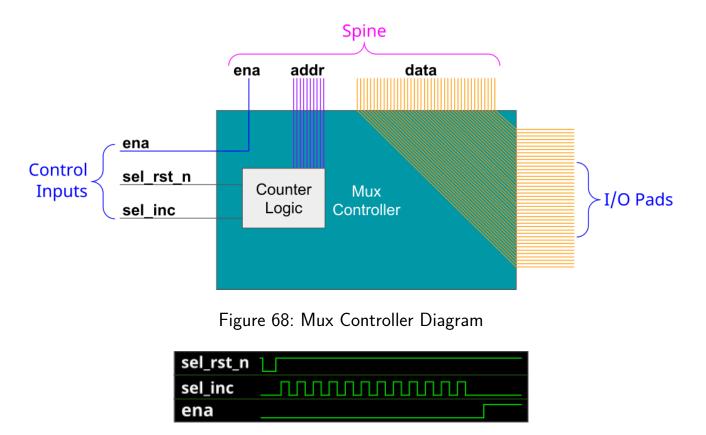

| The Tiny Tapeout Multiplexer                                                                           | 729   |

|                                                                                                        | . 729 |

| •            |     |

|--------------|-----|

| Sponsored by | 735 |

| Team         | 735 |

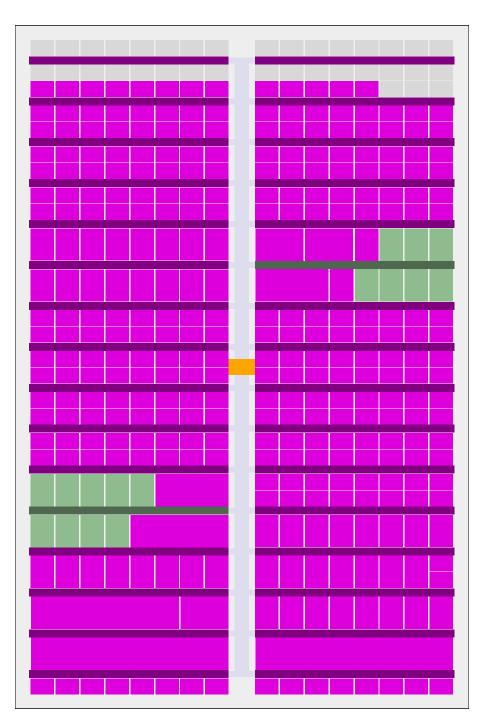

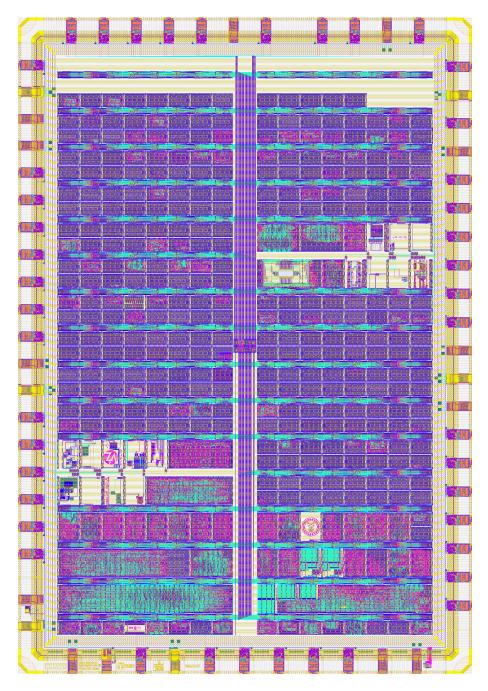

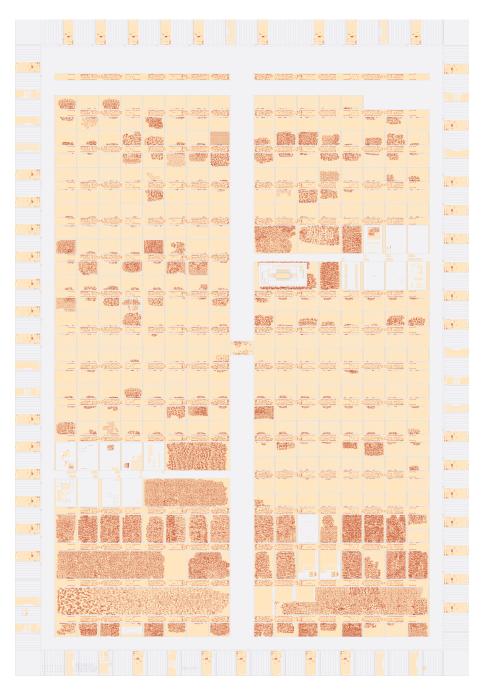

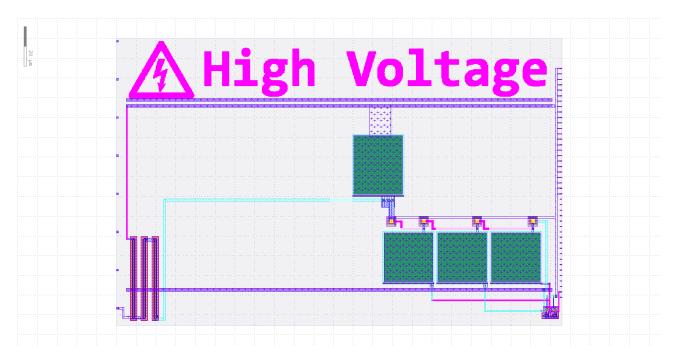

# Chip map

Figure 1: Full chip map

Figure 2: GDS render

Figure 3: Logic density (local interconnect layer)

# **Projects**

# Chip ROM [0]

- Author: Uri Shaked

- Description: ROM with information about the chip

- GitHub repository

- HDL project

- Mux address: 0

- Extra docs

- Clock: 0 Hz

### How it works

ROM memory that contains information about the Tiny Tapeout chip. The ROM is 8-bit wide and 256 bytes long.

| Address | Length | Encoding  | Description                               |

|---------|--------|-----------|-------------------------------------------|

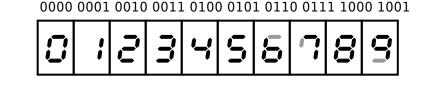

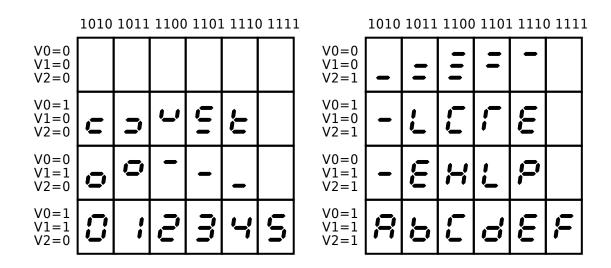

| 0       | 8      | 7-segment | Shuttle name (e.g. "tt07"), null-padded   |

| 8       | 8      | 7-segment | Git commit hash                           |

| 32      | 96     | ASCII     | Chip descriptor (see below)               |

| 248     | 4      | binary    | Magic value:                              |

|         |        |           | <pre>&amp;quot;TT\xFA\xBB&amp;quot;</pre> |

| 252     | 4      | binary    | CRC32 of the ROM contents, little-endian  |

**The ROM layout** The ROM layout is as follows:

**The chip descriptor** The chip descriptor is a simple null-terminated string that describes the chip. Each line is a key-value pair, separated by an equals sign. It contains the following keys:

| Key  | Description                                                                      | Example value                                  |

|------|----------------------------------------------------------------------------------|------------------------------------------------|

| repo | The identifier of the shuttle<br>The name of the repository<br>The commit hash * | tt07<br>TinyTapeout/tinytapeout-07<br>a1b2c3d4 |

• The commit hash is only included for Tiny Tapeout 5 and later.

Here is a complete example of a chip descriptor:

shuttle=tt07

repo=TinyTapeout/tinytapeout-07

commit=a1b2c3d4

**How the ROM is generated** The ROM is automatically generated by tt-supporttools while building the final GDS file of the chip. Look at the rom.py file in the repository for more details.

### How to test

Read the ROM contents by setting the address pins and reading the data pins. The first 16 bytes of the ROM are 7-segment encoded and contain the shuttle name and commit hash. You can read them by toggling the first four DIP switches and observing the on-board 7-segment display.

| # | Input   | Output  | Bidirectional |

|---|---------|---------|---------------|

| 0 | addr[0] | data[0] |               |

| 1 | addr1   | data1   |               |

| 2 | addr2   | data2   |               |

| 3 | addr[3] | data[3] |               |

| 4 | addr[4] | data[4] |               |

| 5 | addr[5] | data[5] |               |

| 6 | addr[6] | data[6] |               |

| 7 | addr[7] | data[7] |               |

### TinyTapeout Factory Test 1

- Author: Tiny Tapeout

- Description: Factory test module

- GitHub repository

- HDL project

- Mux address: 1

- Extra docs

- Clock: 0 Hz

### How it works

The factory test module is a simple module that can be used to test all the  $\rm I/O$  pins of the ASIC.

It has three modes of operation:

- 1. Mirroring the input pins to the output pins (when rst\_n is low).

- 2. Mirroring the bidirectional pins to the output pins (when rst\_n is high sel is low).

- 3. Outputing a counter on the output pins and the bidirectional pins (when rst\_n is high and sel is high).

The following table summarizes the modes:

| rst_n | sel | Mode                 | uo_out value | uio pins |

|-------|-----|----------------------|--------------|----------|

| 0     | Х   | Input mirror         | ui_in        | High-Z   |

| 1     | 0   | Bidirectional mirror | uio_in       | High-Z   |

| 1     | 1   | Counter              | counter      | counter  |

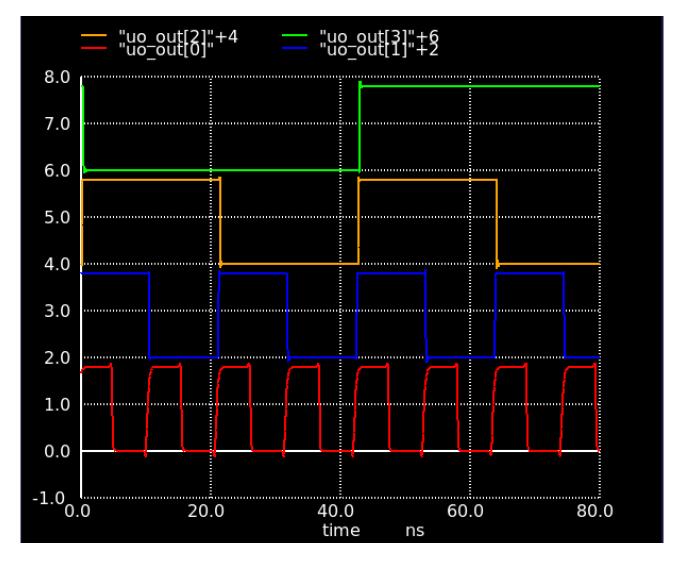

The counter is an 8-bit counter that increments on every clock cycle, and resets when rst\_n is low.

### How to test

- 1. Set rst\_n low and observe that the input pins (ui\_in) are output on the output pins (uo\_out).

- 2. Set rst\_n high and sel low and observe that the bidirectional pins (uio\_in) are output on the output pins (uo\_out).

- 3. Set sel high and observe that the counter is output on both the output pins (uo\_out) and the bidirectional pins (uio).

| # | Input         | Output                    | Bidirectional        |

|---|---------------|---------------------------|----------------------|

| 0 | sel / in_a[0] | output[0] /<br>counter[0] | in_b[0] / counter[0] |

| 1 | in_a1         | output1 /<br>counter1     | in_b1 / counter1     |

| 2 | in_a2         | output2 /<br>counter2     | in_b2 / counter2     |

| 3 | in_a[3]       | output[3] /<br>counter[3] | in_b[3] / counter[3] |

| 4 | in_a[4]       | output[4] /<br>counter[4] | in_b[4] / counter[4] |

| 5 | in_a[5]       | output[5] /<br>counter[5] | in_b[5] / counter[5] |

| 6 | in_a[6]       | output[6] /<br>counter[6] | in_b[6] / counter[6] |

| 7 | in_a[7]       | output[7] /<br>counter[7] | in_b[7] / counter[7] |

### **Trubick - Tiny Tapeout Logic Gate 2**

- Author: Zane Trubick

- Description: Code for 7-Segment

- GitHub repository

- Wokwi project

- Mux address: 2

- Extra docs

- Clock: 0 Hz

### How it works

This chip has a secret code. Figure out the code to activate the "lock." Success will be indicated by a light.

### How to test

Troubleshoot until you get the code.

### External hardware

7-Segment Display, LED

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 0 | IN0   | OUT0   |               |

| 1 | IN1   | OUT1   |               |

| 2 | IN2   | OUT2   |               |

| 3 | IN3   | OUT3   |               |

| 4 | IN4   | OUT4   |               |

| 5 | IN5   | OUT5   |               |

| 6 | IN6   | OUT6   |               |

| 7 | IN7   | OUT7   |               |

### Andrew Vo - Repository [3]

- Author: Andrew Vo

- Description: Repository WokWi

- GitHub repository

- Wokwi project

- Mux address: 3

- Extra docs

- Clock: 0 Hz

### How it works

Using inverters to light up an 8 segment clock. Explain how your project works My chip uses a variety of 3 different inverters, which also involves a flip-flop inverter.

### How to test

Flipping the switches will light up its corresponding segment, however the flip flop inverter has its energy stored with switch 3 and 4, which would alternate. Explain how to use your project

### External hardware

LED Display

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 0 | IN0   | OUT0   |               |

| 1 | IN1   | OUT1   |               |

| 2 | IN2   | OUT2   |               |

| 3 | IN3   | OUT3   |               |

| 4 | IN4   | OUT4   |               |

| 5 | IN5   | OUT5   |               |

| 6 | IN6   | OUT6   |               |

| 7 | IN7   | OUT7   |               |

### tinytapeout [4]

- Author: Htun

- Description: Encoder

- GitHub repository

- Wokwi project

- Mux address: 4

- Extra docs

- Clock: 0 Hz

### How it works

My project works by connecting the first few ins and outs using not gates. Following that there are a few connections that go straight to the output. There is an And gate and any not gates.

### How to test

Press the run button and flip switches to see what lights light up.

### External hardware

None.

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 0 | IN0   | OUT0   |               |

| 1 | IN1   | OUT1   |               |

| 2 | IN2   | OUT2   |               |

| 3 | IN3   |        |               |

| 4 | IN4   |        |               |

| 5 | IN5   |        |               |

| 6 | IN6   |        |               |

| 7 | IN7   |        |               |

### Half adder [5]

- Author: Keyshon Howard

- Description: 2x2 Half adder

- GitHub repository

- Wokwi project

- Mux address: 5

- Extra docs

- Clock: 0 Hz

### How it works

"The Project is a half adder that uses an Xor gate for the Sum on the inputs and an and gate for the Carry bit"

### How to test

"You change the inputs and see the output change based on the lights illuminating"

### External hardware

"Two LED displays to see the output"

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 0 |       | OUT0   |               |

| 1 | IN1   |        |               |

| 2 | IN2   |        |               |

| 3 |       |        |               |

| 4 |       |        |               |

| 5 |       | OUT5   |               |

| 6 |       |        |               |

| 7 |       |        |               |

### Samson's Tiny Tapout Project [6]

- Author: Samson

- Description: A game to get the number to show up as 0

- GitHub repository

- Wokwi project

- Mux address: 6

- Extra docs

- Clock: 0 Hz

### How it works

The inputs 0-7 will change how the LED will work. Some inputs use AND statements and others use XOR. The user will try to find out how to get the number 0.

### How to test

The user will input/guess to find the combination to get 0.

### **External hardware**

7 segment display.

| # | Input                                                                                     | Output                                                                                    | Bidirectional |

|---|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------|

| 0 | Connected to<br>an AND<br>statement<br>with 1 to<br>activate top<br>and top right<br>LEDs | Connected to<br>an AND<br>statement<br>with 1 to<br>activate top<br>and top right<br>LEDs |               |

| # | Input         | Output        | Bidirectional |

|---|---------------|---------------|---------------|

| 1 | Connected to  | Connected to  |               |

|   | an AND        | an AND        |               |

|   | statement     | statement     |               |

|   | with 0 to     | with 1 to     |               |

|   | activate top  | activate top  |               |

|   | and top right | and top right |               |

|   | LEDs          | LEDs          |               |

| 2 | Goes to input | Goes to input |               |

|   | w/~the~same   | w/ the same   |               |

|   | number        | number        |               |

| 3 | Goes to input | Goes to input |               |

|   | w/thesame     | w/ the same   |               |

|   | number        | number        |               |

| 4 | Goes to input | Goes to input |               |

|   | w/ the same   | w/the same    |               |

|   | number        | number        |               |

| 5 | Goes to input | Goes to input |               |

|   | w/ the same   | w/the same    |               |

|   | number        | number        |               |

| 6 | Connected to  | Connected to  |               |

|   | an XOR        | an XOR        |               |

|   | statement     | statement     |               |

|   | with 7 to     | with 7 to     |               |

|   | activate top  | activate top  |               |

|   | and top right | and top right |               |

|   | LEDs          | LEDs          |               |

| 7 | Connected to  | Connected to  |               |

|   | an XOR        | an XOR        |               |

|   | statement     | statement     |               |

|   | with 6 to     | with 6 to     |               |

|   | activate top  | activate top  |               |

|   | and top right | and top right |               |

|   | LEDs          | LEDs          |               |

### Jacks First Project [7]

- Author: Jack B

- Description: Jacks Frist Wokwi template

- GitHub repository

- Wokwi project

- Mux address: 7

- Extra docs

- Clock: 0 Hz

### How it works

This project is a full adder.

### How to test

Test inputs 0 and 1 as input bits, and input 2 as Carry in. Output 0 is the first digit out, and output 1 as carry out.

### External hardware

Used an LED to test the full adder.

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 0 | IN0   | OUT0   |               |

| 1 | IN1   | OUT1   |               |

| 2 | IN2   |        |               |

| 3 |       |        |               |

| 4 |       |        |               |

| 5 |       |        |               |

| 6 |       |        |               |

| 7 |       |        |               |

### 4 x 4 array multiplier NuKoP [8]

- Author: Aiden Li, Mahid Hosen

- Description: given two 4 bit unsigned binary numbers, outputs the product of the two numbers

- GitHub repository

- HDL project

- Mux address: 8

- Extra docs

- Clock: 0 Hz

### How it works

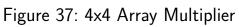

Using the 4 by 4 multiplier from the previous Lab, we implemented the design so that it could be used by a TinyTapeout chip. The 4 by 4 multiplier uses a series of full adders and AND gates, in order to multiply two 3 bit numbers together. In order to do this, the module multiplies the top number by the bottom number, using the AND and Full Adders, and repeats this over and over for each digit in the second binary number. Each number created has a zero added as a least significant bit, and then when all the four numbers are made, they are all added together to find the total product. The Verilog design incorporates the design by using multiple modules to represent different parts of the design. A full adder module is made to add two one digit bits together. Using the full adder module, the part module uses this to multiply each digit of the first number to one digit in the bottom number. Finally, the array\_mult\_generate module uses the part module to repeat this process for every digit on the second number, using generate to loop through each one. This final module outputs the 8 bit product of the two 4 digit binary numbers.

### How to test

The design works by having a set of 8 switches and 8 LEDs. The 8 switches represent the four bits for one input, and the 4 bits for another. The LEDs are for the output with it lighting up as a 1, and with it off being 0. Switching the switches changes the inputs for the two binary numbers you want and the LEDs will correspond with the 8 digit product. In order to test to see that the design works, you can choose two 4 bit numbers and see if the product displayed is correct. You can test for inputs such as 0000 and 0001 which should output 0000 and the other number respectively, because they are identities. We don't need to check for overflow because the largest product,  $15 \times 15 = 225$  is able to be represented by the 8 digits. Other numbers can also be used in order to test the functionality of the design.

### External hardware

The TinyTapeout chip has switches for the inputs and LEDs for the outputs.

| # | Input    | Output    | Bidirectional |

|---|----------|-----------|---------------|

| 0 | ui_in[0] | uo_out[0] |               |

| 1 | ui_in1   | uo_out1   |               |

| 2 | ui_in2   | uo_out2   |               |

| 3 | ui_in[3] | uo_out[3] |               |

| 4 | ui_in[4] | uo_out[4] |               |

| 5 | ui_in[5] | uo_out[5] |               |

| 6 | ui_in[6] | uo_out[6] |               |

| 7 | ui_in[7] | uo_out[7] |               |

# MuxLED [9]

- Author: Alex Moore

- Description: mulitplexor connected to LED

- GitHub repository

- Wokwi project

- Mux address: 9

- Extra docs

- Clock: 0 Hz

How it works

My project uses a mulitplexor to light up an LED as well as the display module.

#### How to test

Check if the LED and display both light up by switching input 7 on/off and inputs 4 and 6, if in7 is on then in 6 should turn the lights on. If in 7 is off then in4 will turn on the lights

External hardware

LED display & LED diode

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 0 |       | OUT0   |               |

| 1 |       | OUT1   |               |

| 2 |       | OUT2   |               |

| 3 |       | OUT3   |               |

| 4 | IN4   | OUT4   |               |

| 5 |       | OUT5   |               |

| 6 | IN6   | OUT6   |               |

| 7 | IN7   | OUT7   |               |

# Tiny Tapeout [10]

- Author: Andy

- Description: Using logic gates to determine sections on a 7 segment display

- GitHub repository

- Wokwi project

- Mux address: 10

- Extra docs

- Clock: 0 Hz

### How it works

Have several input values with respective output values while using gates to control different the inputs to have different outputs.

### How to test

Switch on and off for the input gates, test around different value combinations and options to see what you can create on the number display.

### External hardware

none.

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 0 | IN0   | OUT0   |               |

| 1 | IN1   | OUT1   |               |

| 2 | IN2   | OUT2   |               |

| 3 | IN3   |        |               |

| 4 | IN4   |        |               |

| 5 | IN5   |        |               |

| 6 | IN6   |        |               |

| 7 | IN7   |        |               |

### halfadder+not [11]

- Author: Vincent Phan

- Description: My project has a half adder and not gate which turns the lightoff and on for a clock.

- GitHub repository

- Wokwi project

- Mux address: 11

- Extra docs

- Clock: 0 Hz

### How it works

My first two inputs go through an adder. The last input goes through an inverter. The rest pass through.

### How to test

Flip the switches in order to light up the clock.

### External hardware

This requires the default seven segment display and dip switches.

| # | Input              | Output             | Bidirectional |

|---|--------------------|--------------------|---------------|

| 0 | connected to adder | sum                |               |

| 1 | connected to adder | carry              |               |

| 2 | pass through       | pass through       |               |

| 3 | pass through       | pass through       |               |

| 4 | pass through       | pass through       |               |

| 5 | pass through       | pass through       |               |

| 6 | pass through       | output to inverter |               |

| 7 | input to inverter  |                    |               |

### Yohan Tiny Tapeout Project [12]

- Author: Juan

- Description: Mixed Logic Gate to control 7 segment display

- GitHub repository

- Wokwi project

- Mux address: 12

- Extra docs

- Clock: 0 Hz

### How it works

"This is a project in work. The gates makes signals do funky things."

### How to test

"That is to be determined once the functionality is figured out."

### External hardware

"Seven segment display, input board, output board, switch panel"

| _ |       |        |               |

|---|-------|--------|---------------|

| # | Input | Output | Bidirectional |

| 0 | IN0   | OUT0   |               |

| 1 | IN1   | OUT1   |               |

| 2 | IN2   | OUT2   |               |

| 3 | IN3   | OUT3   |               |

| 4 | IN4   | OUT4   |               |

| 5 | IN5   | OUT5   |               |

| 6 | IN6   | OUT6   |               |

| 7 | IN7   | OUT7   |               |

|   |       |        |               |

### 4-bit Multiplier [13]

- Author: Nick Pham, Nathan Macapinlac

- Description: 4-bit multiplier for NYU's digital logic course's Lab 4

- GitHub repository

- HDL project

- Mux address: 13

- Extra docs

- Clock: 0 Hz

#### How it works

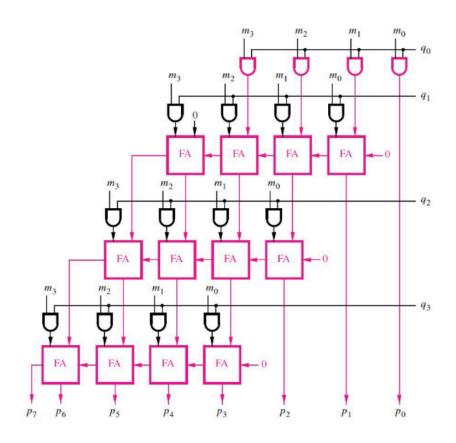

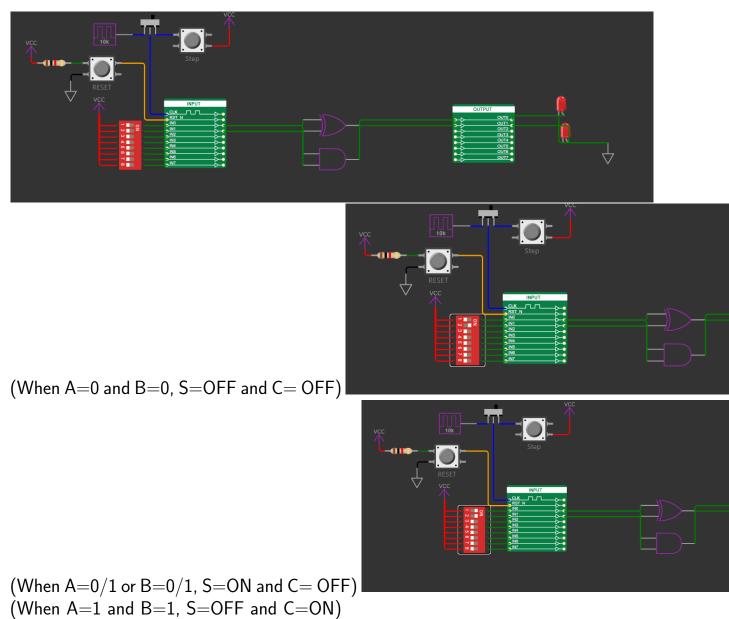

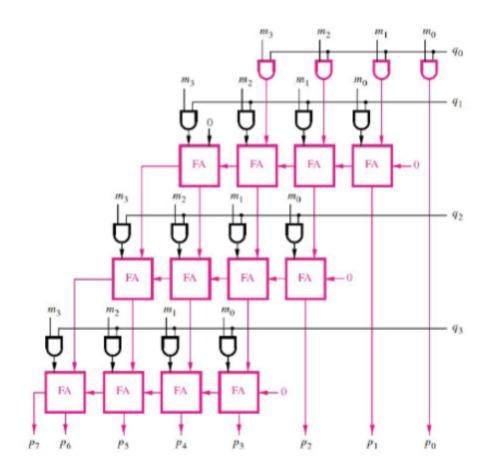

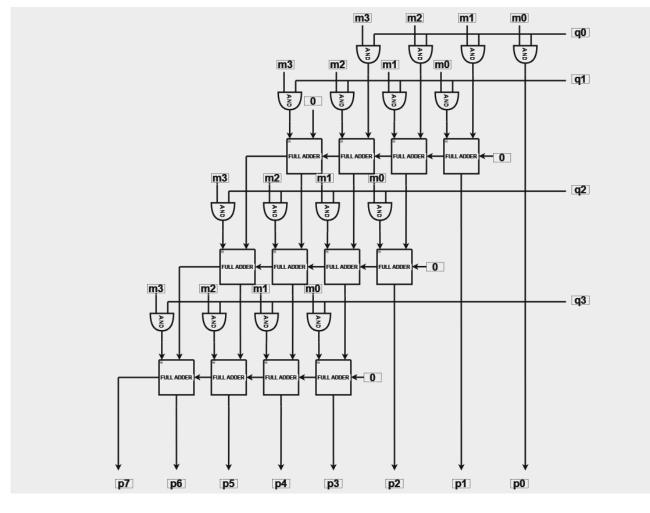

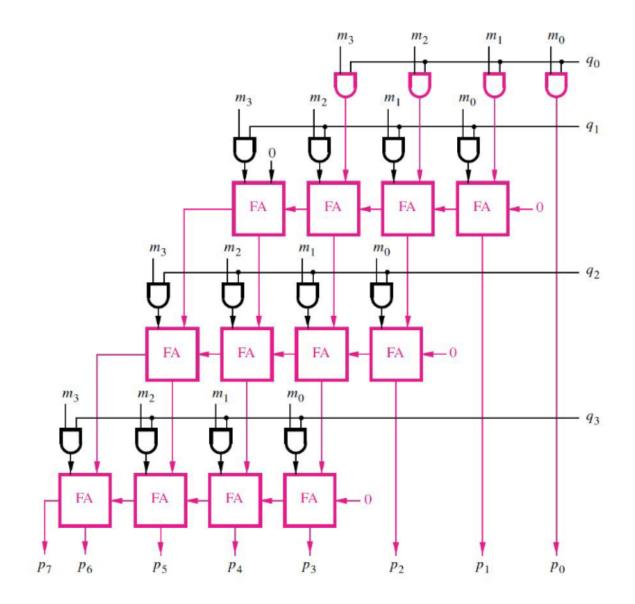

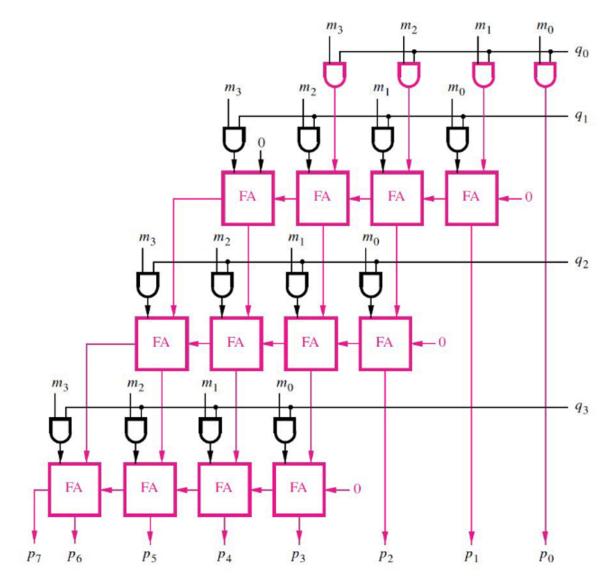

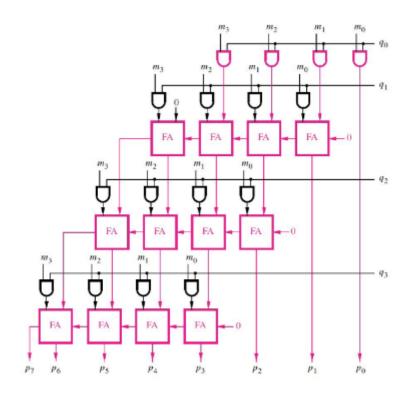

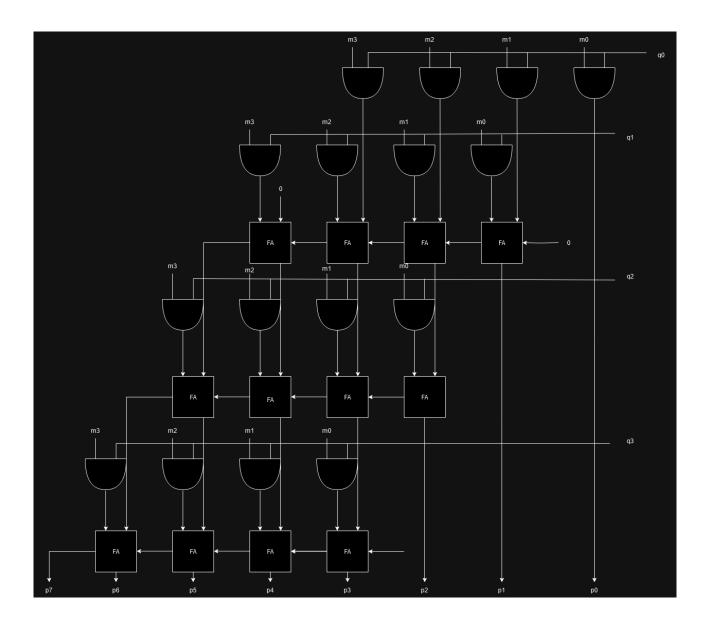

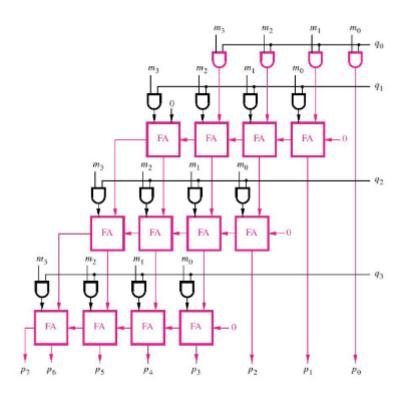

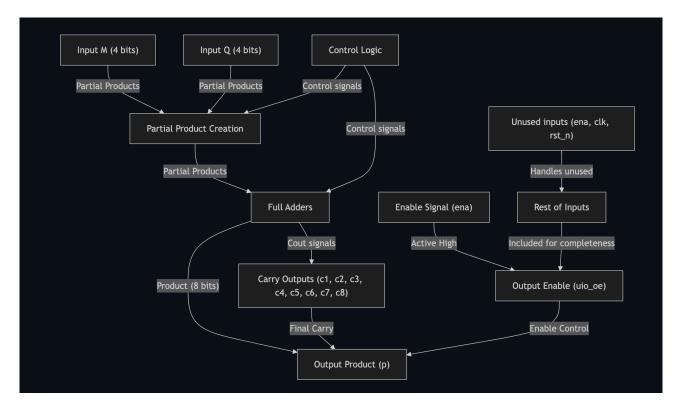

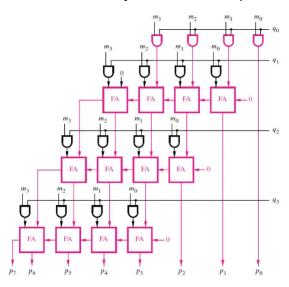

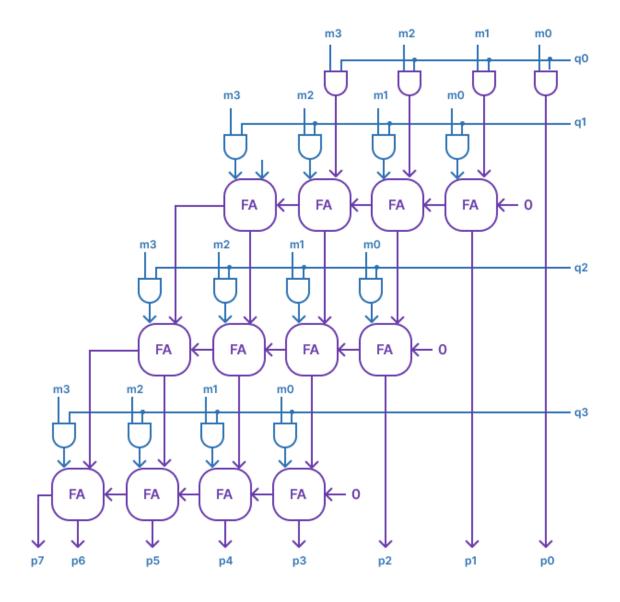

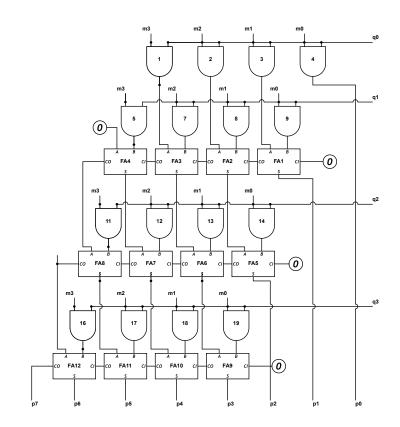

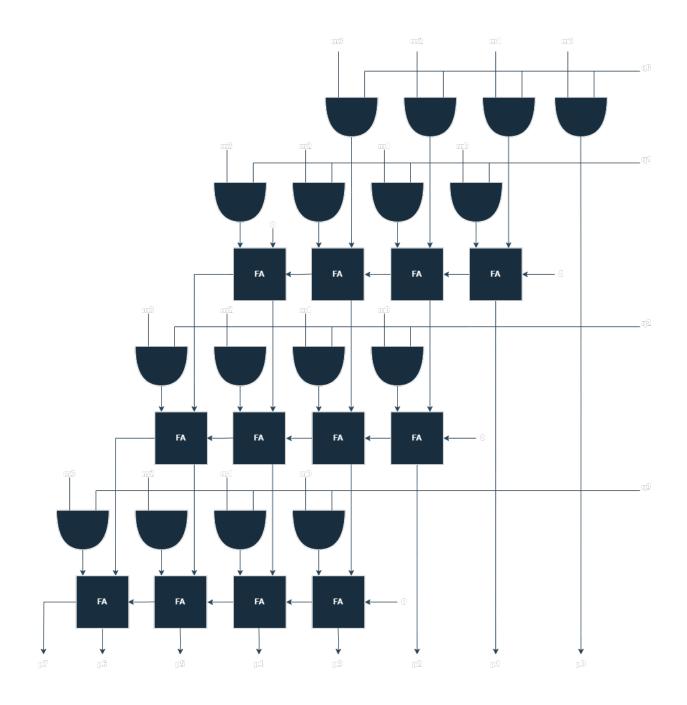

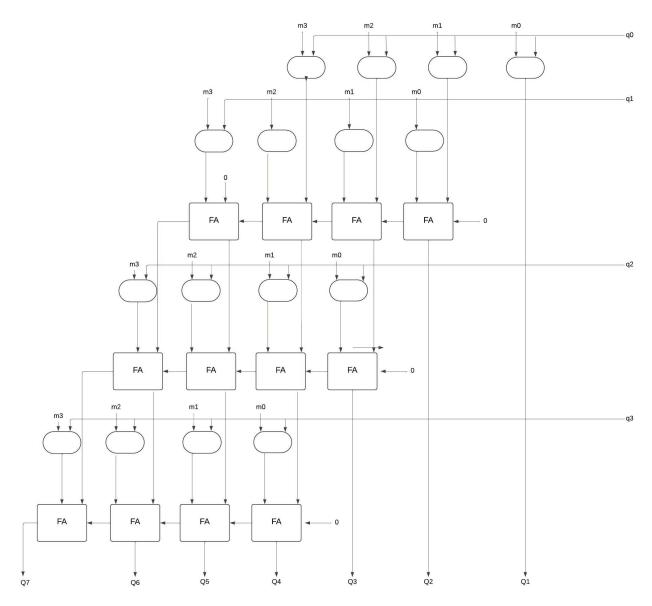

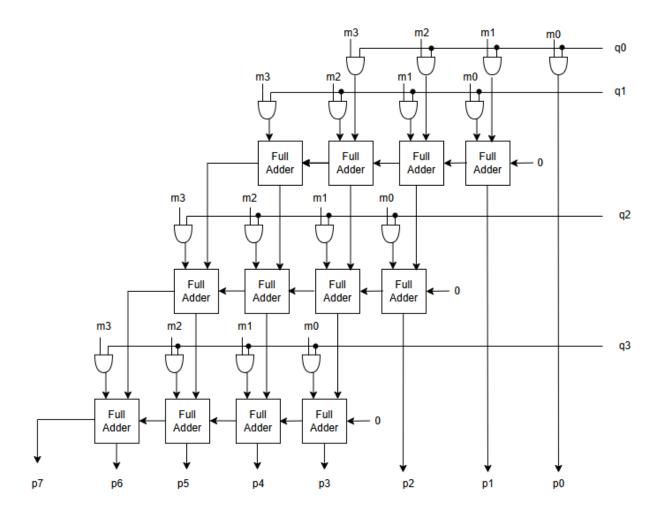

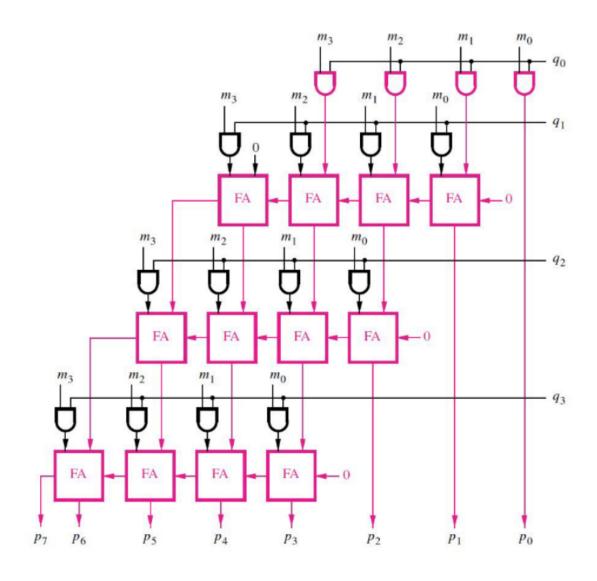

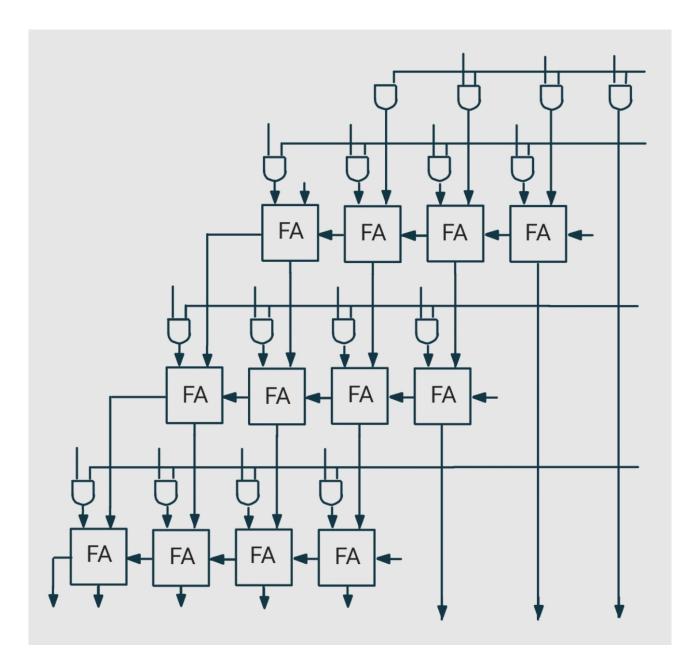

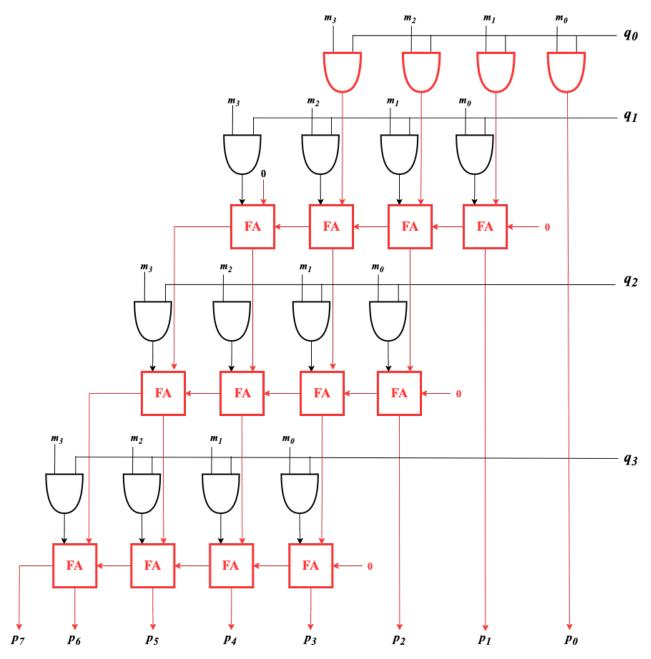

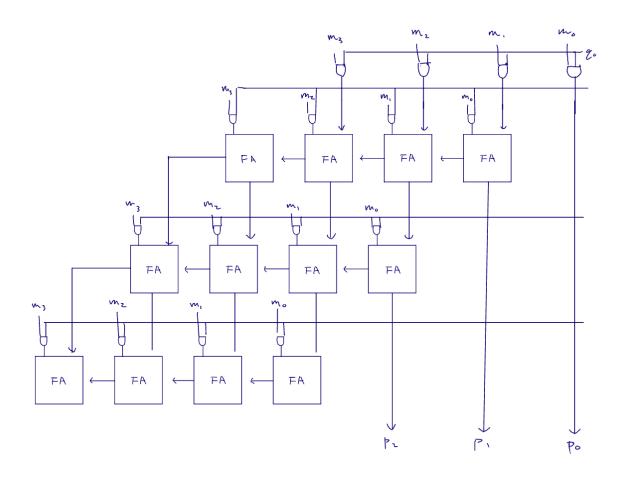

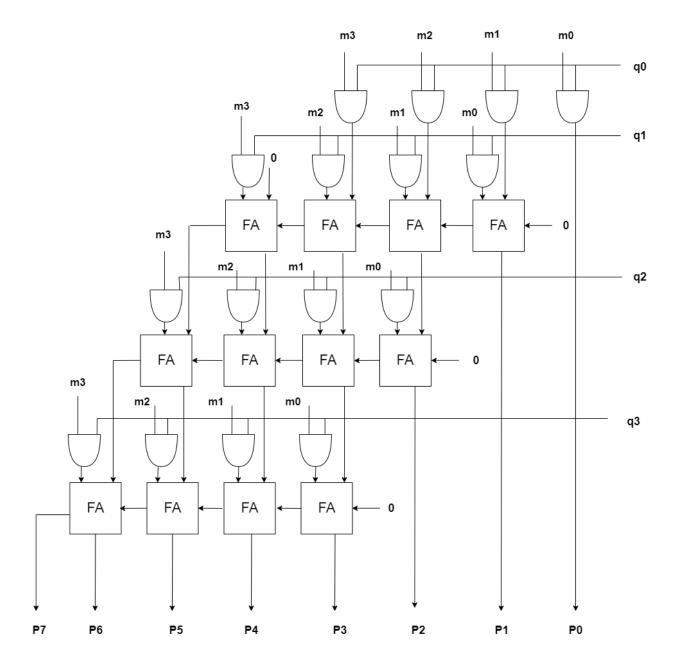

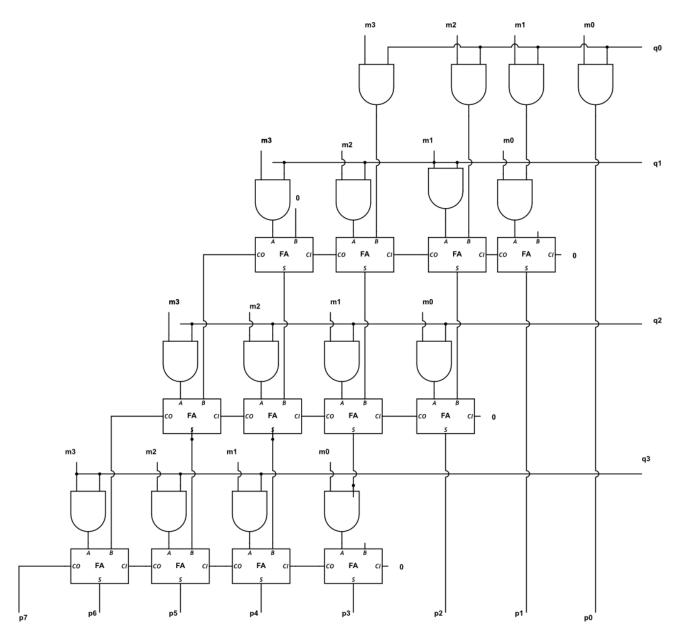

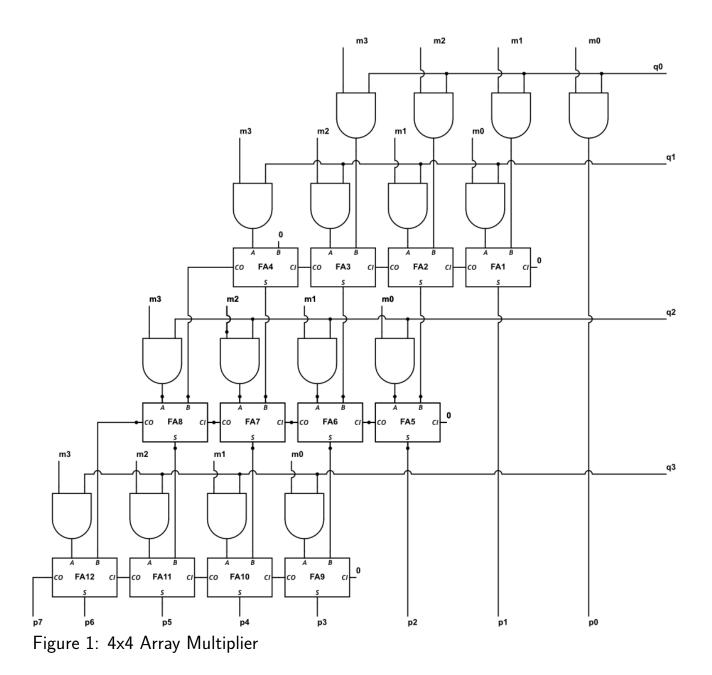

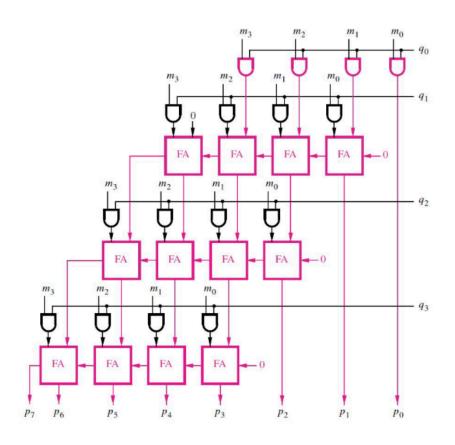

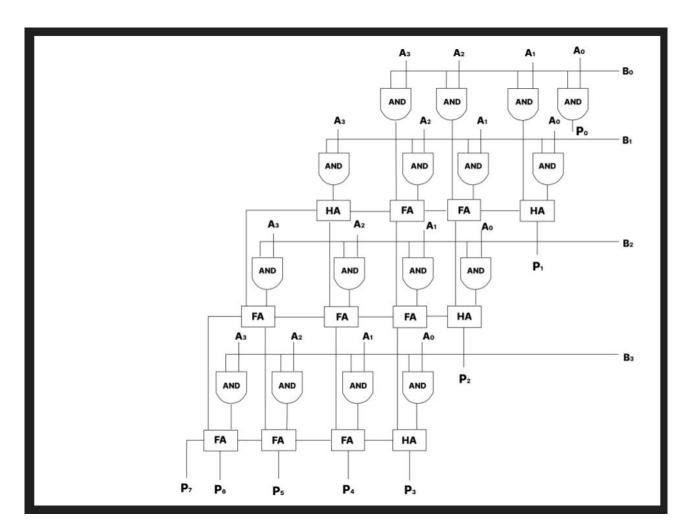

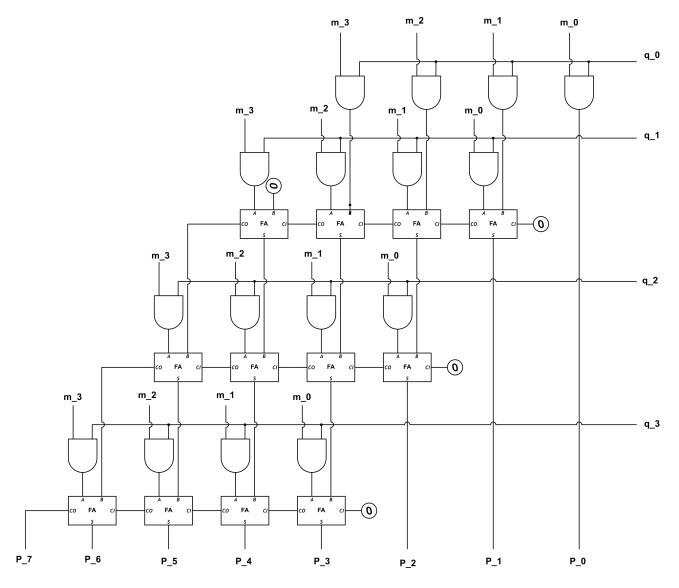

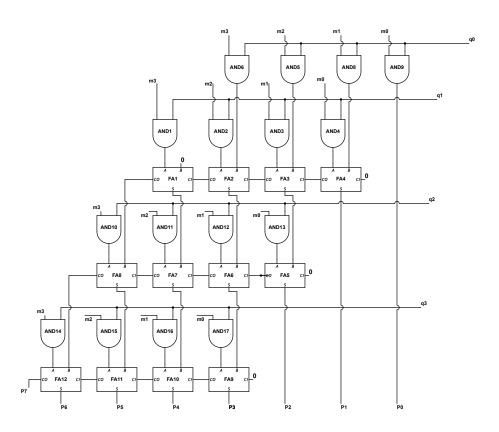

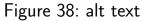

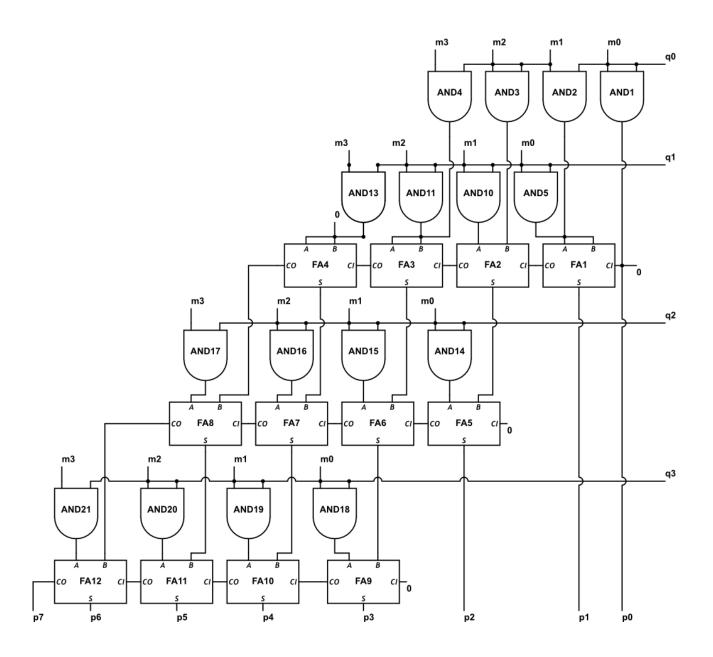

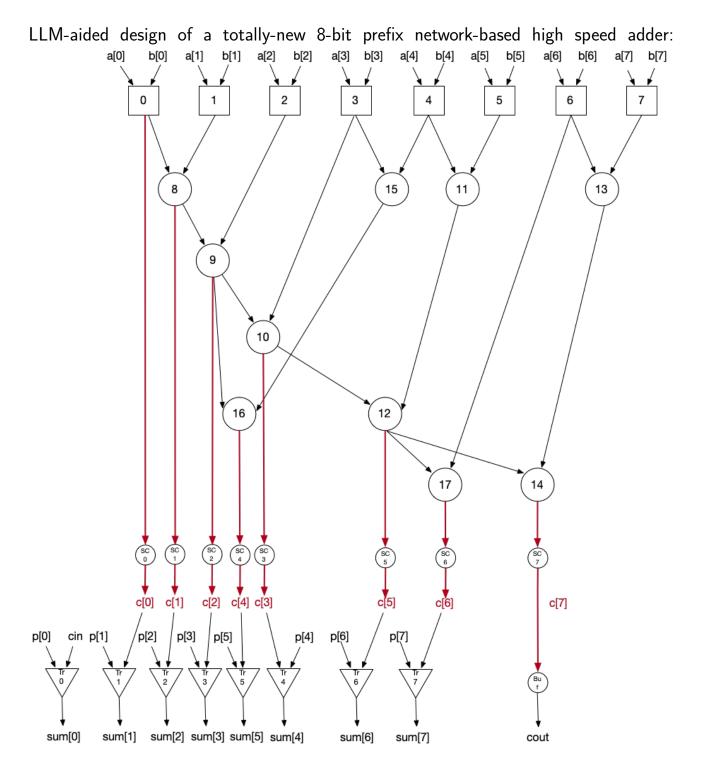

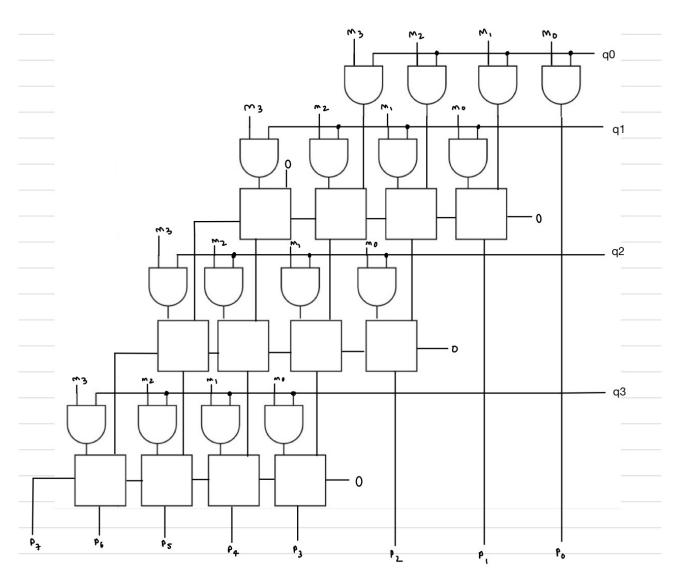

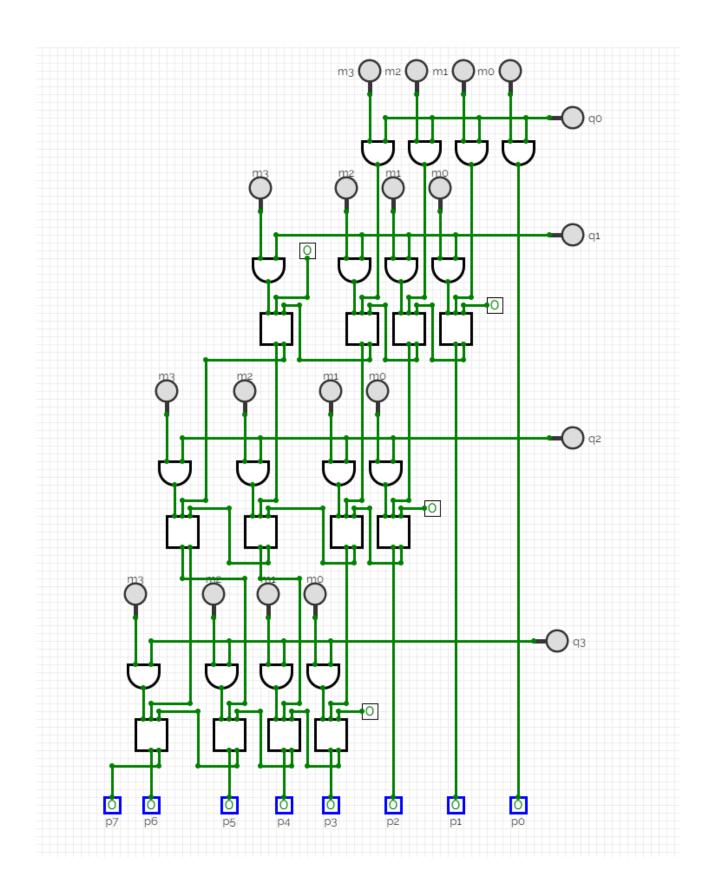

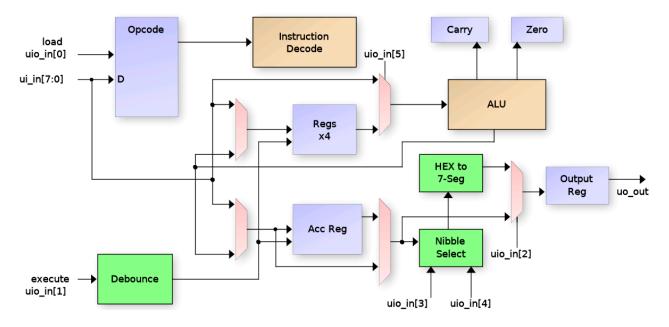

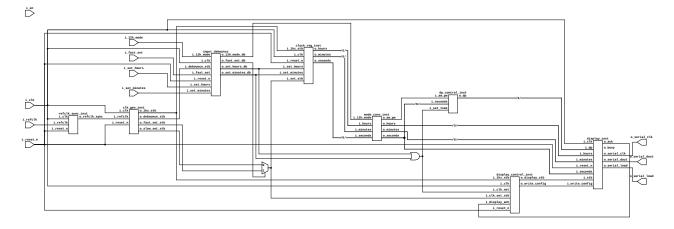

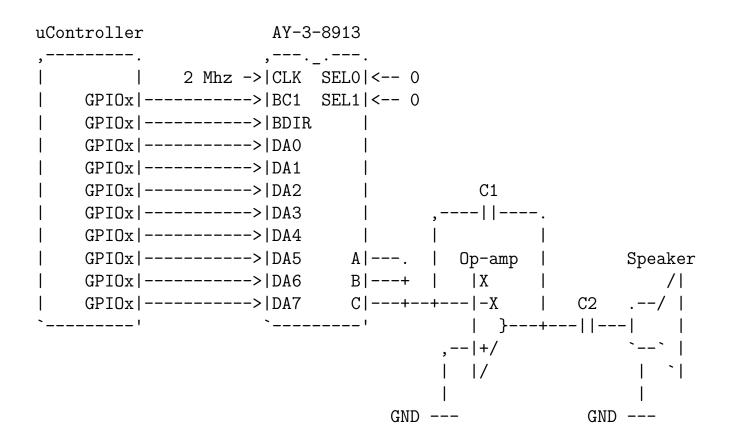

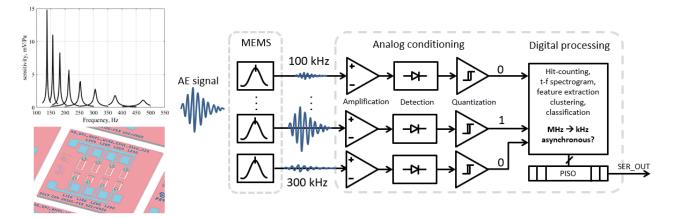

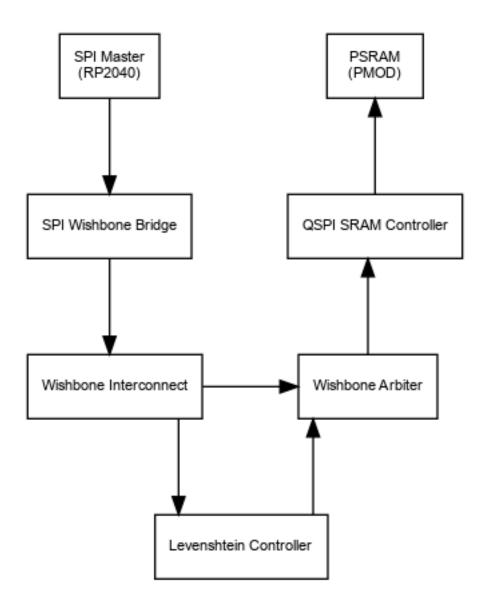

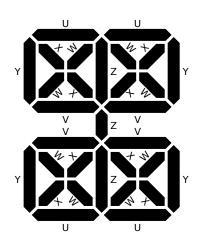

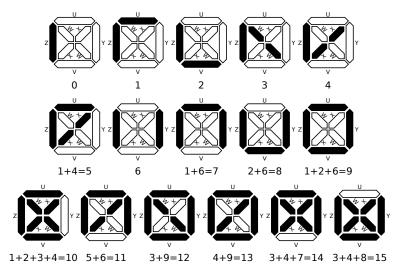

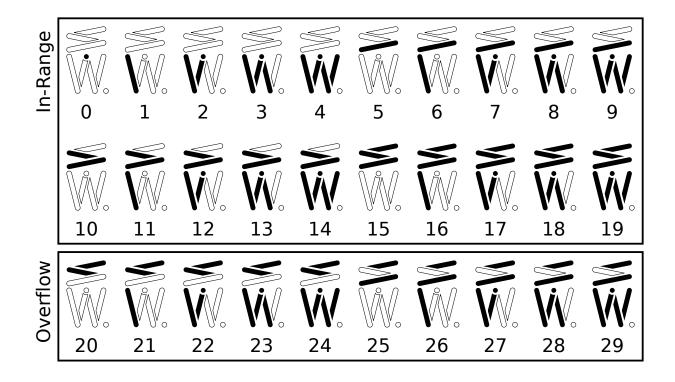

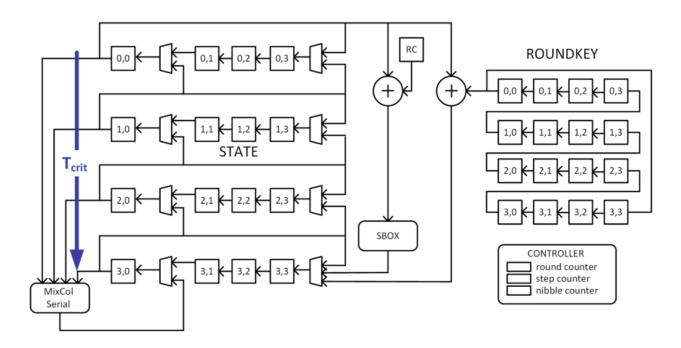

Figure 4: image

Above is a diagram that represents a 4-bit multiplier, which takes in two 4-bit integers and outputs a single 8-bit integer.

This was created using a manual structural design. We utilized a 1-bit full adder module in our implementation.

• AND-Gates are utilized to multiply each bit of input m with each bit of input q.

- We align partial products diagonally to mimic that of manual binary multiplication.

- We use 1-bit Full Adders to add products and handle carries.

- The outputs of the Full Adders eventually went to the bits of our output p which is an 8-bit integer.

#### How to test

Creating your own test cases:

- Go to the test folder and locate test.py.

- Edit test.py and add your own custom test cases.

```

# Example

# TEST CASE #0 -> 0 * 1

dut.ui_in.value = 0b00000001

await ClockCycles(dut.clk, 1)

assert dut.uo_out.value = 0b0000000

```

- Run the test with make and check the tests passed.

- If you've forked the repository

- Commit and push your changes to your forked repository

- Check Github Actions to check if your tests have passed

### **External hardware**

N/A

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 0 | m[0]  | p[0]   |               |

| 1 | m1    | p1     |               |

| 2 | m2    | p2     |               |

| 3 | m[3]  | p[3]   |               |

| 4 | q[0]  | p[4]   |               |

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 5 | q1    | p[5]   |               |

| 6 | q2    | p[6]   |               |

| 7 | q[3]  | p[7]   |               |

### Yared Fente's Tiny Tapeout [14]

- Author: Yared Fente

- Description: Adder Circuit

- GitHub repository

- Wokwi project

- Mux address: 14

- Extra docs

- Clock: 0 Hz

### How it works

It performs addition of numbers.

### How to test

Use 7 on-switch material to test.

### External hardware

7-segment display.

| # | Input           | Output           | Bidirectional |

|---|-----------------|------------------|---------------|

| 0 | Input to an XOR | Output from xor2 |               |

| 1 | Input to an XOR | Output from or1  |               |

| 2 | Input to an AND |                  |               |

| 3 |                 |                  |               |

| 4 |                 |                  |               |

| 5 |                 |                  |               |

| 6 |                 |                  |               |

| 7 |                 |                  |               |

### Metastable Chip [15]

- Author: Patrick McDermott

- Description: Metastable Multiplier w/ 4 inputs

- GitHub repository

- Wokwi project

- Mux address: 15

- Extra docs

- Clock: 0 Hz

### How it works

The metastable multiplier violates the timing delay needed by logic gates to accurately manipulate binary bits the way they're supposed to which causes cases of logic gates outputting a 1 and a 0 at the same time.

### How to test

First set all inputs to logic 0 and then set all of them to 1. Observe the metastable of the circuit befure it resolves itself to either a logic 1 or 0.

### External hardware

4 switches are used to control the input along with an external clock and reset 4 Leds are used on the output to display which combination of binary you are using at the input

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 0 | A0    | Out0   |               |

| 1 | A1    | Out1   |               |

| 2 | B0    | Out2   |               |

| 3 | B1    | Out3   |               |

| 4 |       |        |               |

| 5 |       |        |               |

| 6 |       |        |               |

| 7 |       |        |               |

## Secret Initial [32]

- Author: Kiarash

- Description: A certain set of inputs will display a secret initial.

- GitHub repository

- Wokwi project

- Mux address: 32

- Extra docs

- Clock: 0 Hz

### How it works

Still to be decided, but I am planning on making a certain combination of inputs that will spell the letter F.

#### How to test

will fill in.

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 0 | IN0   | OUT0   |               |

| 1 | IN1   | OUT1   |               |

| 2 | IN2   | OUT2   |               |

| 3 | IN3   | OUT3   |               |

| 4 | IN4   | OUT4   |               |

| 5 | IN5   | OUT5   |               |

| 6 | IN6   | OUT6   |               |

| 7 | IN7   | OUT7   |               |

## Binary to 7 Segment Display Decoder [33]

- Author: Robert McLintock

- Description: This is a binary to 7 segment display decoder

- GitHub repository

- Wokwi project

- Mux address: 33

- Extra docs

- Clock: 0 Hz

#### How it works

This decoder uses 4 inputs that represent a binary number determined by the switches. In turn the number will then be decoded into decimal and displayed on the 7 segment display.

### How to test

Play around, FLIP A SWITCH or 2, or 3, or 4:)

## External hardware

None :)

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 0 | IN0   | OUT0   |               |

| 1 | IN1   | OUT1   |               |

| 2 | IN2   | OUT2   |               |

| 3 | IN3   | OUT3   |               |

| 4 | IN4   | OUT4   |               |

| 5 | IN5   | OUT5   |               |

| 6 | IN6   | OUT6   |               |

| 7 | IN7   |        |               |

# Tahiti [34]

- Author: Harrison

- Description: Wokwi Design by Harrison

- GitHub repository

- Wokwi project

- Mux address: 34

- Extra docs

- Clock: 0 Hz

## How it works

Wokwi design

### How to test

Switch buttons on and off

## External hardware

Wokwi

| # | Input          | Output    | Bidirectional |

|---|----------------|-----------|---------------|

| 0 | NOTin0         | NOTout0   |               |

| 1 | ANDin1         | ANDout1   |               |

| 2 | ANDin2         |           |               |

| 3 | NOT2in3        | NOT2out3  |               |

| 4 | HALF ADDER in4 |           |               |

| 5 |                | SUMout5   |               |

| 6 |                | CARRYout6 |               |

| 7 | HALF ADDER in7 |           |               |

## Letter H [35]

- Author: Hannah Thoreson

- Description: Letter H

- GitHub repository

- Wokwi project

- Mux address: 35

- Extra docs

- Clock: 0 Hz

#### How it works

turning on all switches draws the letter H

#### How to test

turning on all switches draws the letter H

#### External hardware

List external hardware used in your project (e.g. PMOD, LED display, etc), if any

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 0 | IN0   | OUT0   |               |

| 1 | IN1   | OUT1   |               |

| 2 | IN2   | OUT2   |               |

| 3 | IN3   | OUT3   |               |

| 4 | IN4   | OUT4   |               |

| 5 | IN5   | OUT5   |               |

| 6 | IN6   | OUT6   |               |

| 7 | IN7   | OUT7   |               |

|   |       |        |               |

# APTT [36]

- Author: Andy

- Description: lights up depending on action

- GitHub repository

- Wokwi project

- Mux address: 36

- Extra docs

- Clock: 0 Hz

## How it works

My project works by, allowing the user to turn on or off switches to turn on lights

### How to test

To use my project,

### External hardware

I used logic gates and LED'S

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 0 |       |        |               |

| 1 | IN1   | Out1   |               |

| 2 | IN2   |        |               |

| 3 | IN3   |        |               |

| 4 | IN4   | Out5   |               |

| 5 | IN5   |        |               |

| 6 | IN6   |        |               |

| 7 | IN7   | Out7   |               |

# Two PFD [37]

- Author: Soumobrata Ghosh

- Description: A zero Dead zone PFD and a basic PFD

- GitHub repository

- Wokwi project

- Mux address: 37

- Extra docs

- Clock: 0 Hz

A zero blind spot phase frequency Detector

#### How it works

A basic phase frequency Dtector

#### How to test

If VCO is leading DN would be high and if REF is leading UP would be high

#### **External hardware**

List external hardware used in your project (e.g. PMOD, LED display, etc), if any

| # | Input   | Output | Bidirectional |

|---|---------|--------|---------------|

| 0 | REF     | UP     |               |

| 1 | VCO     | DN     |               |

| 2 | Logic 1 | UP2    |               |

| 3 | Ref     | Reset  |               |

| 4 | VCO     | DN2    |               |

| 5 |         |        |               |

| 6 |         |        |               |

| 7 |         |        |               |

## Zero to Nine Display Count [38]

- Author: Mariano

- Description: First Design. Display numbers on seven segment display using flip flop counter.

- GitHub repository

- Wokwi project

- Mux address: 38

- Extra docs

- Clock: 0 Hz

### How it works

Binary counter using flip flops connected to clock line. Displays numbers on the seven segment display.

### How to test

Use the step button to count from zero to nine.

## External hardware

number led array and step button

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 0 |       | OUT0   |               |

| 1 |       | OUT1   |               |

| 2 |       | OUT2   |               |

| 3 |       | OUT3   |               |

| 4 |       | OUT4   |               |

| 5 |       | OUT5   |               |

| 6 |       | OUT6   |               |

| 7 |       | OUT7   |               |

# Redco [39]

- Author: Shrikrishna Kaje

- Description: Reconfigurable DCO

- GitHub repository

- Wokwi project

- Mux address: 39

- Extra docs

- Clock: 0 Hz

## How it works

This design is targetted to be used as

- 1. Ring oscillator

- 2. Clock divider

- 3. Digitally controlled oscillator

Basically it is a ring oscillator which is connected clock divider ckt. The clock divider can be muxed out for different frequencies

- 1. Ring oscillator Five inverters are used in chain. By shorting out0 pin to in0 and in4, the design can be configured as a ring oscillator Frequency =  $1/(5^*$ inverter cell delay)

- 2. Clock divider network Dff chain is used to introduce clock division. By using combination between s0(in1), s1(in2), s2(in3) below we can different division at out1 fs frequency of the clock signal

## How to test

Pin description

- 1. clk (in4) clock input, input the clock signal to this pin if the chip is to be used as a clock divider, out1 is the output of the clock divider. Short it to in0 and out0 if used as a Oscillator

- 2. in(in0) Short it with clk pin and out0 if used as a ring oscillator

- 3. s0(in1) LSB of the binary input (DCO input or clock divider select)

- 4. s1(in2) second binary input (DCO input or clock divider select)

- 5. s2(in3) MSB of the binary input (DCO input or clock divider select )

- 6. out0 ring oscillator output

- 7. out1 clock divider and DCO

## External hardware

List external hardware used in your project (e.g. PMOD, LED display, etc), if any

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 0 | in    | out0   |               |

| 1 | s0    | out1   |               |

| 2 | s1    |        |               |

| 3 | s2    |        |               |

| 4 | clk   |        |               |

| 5 |       |        |               |

| 6 |       |        |               |

| 7 |       |        |               |

# Light LED [40]

- Author: Baruas

- Description: Set the switches to get the last led to light up

- GitHub repository

- Wokwi project

- Mux address: 40

- Extra docs

- Clock: 0 Hz

#### How it works

-> Tiny Tapeout Puzzles

In this puzzle you have to work out how to set the switches to get the last led to light up.

Your friend has been working hard to plan a vacation. (Un)fortunately, they love digital logic, so rather than print you an itinerary, they drew you the following digital circuit.

#### How to test

Two vacations are possible: can you use the switches to figure out where you'll go, what you'll eat, and what souvenir you'll return with?

#### **External hardware**

| Switch $\#$ |           |

|-------------|-----------|

| 1           | Beach     |

| 2           | Mountains |

| 3           | Ski       |

| 4           | Swim      |

| 5           | Ice Cream |

| 6           | Fondue    |

| 7           | Tacos     |

| 8           | Sun Burn  |

|             |           |

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 0 | IN0   | OUT0   |               |

| 1 | IN1   |        |               |

| 2 | IN2   |        |               |

| 3 | IN3   |        |               |

| 4 | IN4   |        |               |

| 5 | IN5   |        |               |

| 6 | IN6   |        |               |

| 7 | IN7   |        |               |

## Matmul System [41]

- Author: Abarajithan

- Description: Matmul System

- GitHub repository

- HDL project

- Mux address: 41

- Extra docs

- Clock: 0 Hz

### How it works

This is a simple system that performs matrix-vector multiplication. The matrix K[R,C] and vector X[R] is sent from outside through UART. They are decoded by a UART RX module, and sent into the matrix-vector multiplication core as AXI-Stream. The core performs the multiplication and outputs the result as AXI-Stream. The result is then packed into UART format by the UART TX module and sent outside.

#### How to test

iverilog -g2012 -o compiled src/mvm\_uart\_system.v src/uart\_rx.v src/uart\_

## External hardware

None

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 0 | RX    | ТХ     |               |

| 1 |       |        |               |

| 2 |       |        |               |

| 3 |       |        |               |

| 4 |       |        |               |

| 5 |       |        |               |

| 6 |       |        |               |

| 7 |       |        |               |

## Tiny Tapeout-Huerta [42]

- Author: Fernando Huerta

- Description: My project displays my initials on a seven segment display

- GitHub repository

- Wokwi project

- Mux address: 42

- Extra docs

- Clock: 0 Hz

#### How it works

Create and edit a code for the seven segment dislay to create my initials

#### How to test

Trouble shoot on and of switches in order to utilize seven segment display

#### External hardware

seven segment display, AND/OR Gates, input an output connections

| _ |       |        |               |

|---|-------|--------|---------------|

| # | Input | Output | Bidirectional |

| 0 | IN0   | OUT0   |               |

| 1 | IN1   | OUT1   |               |

| 2 | IN2   | OUT2   |               |

| 3 | IN3   | OUT3   |               |

| 4 | IN4   | OUT4   |               |

| 5 | IN5   | OUT5   |               |

| 6 | IN6   | OUT6   |               |

| 7 | IN7   | OUT7   |               |

|   |       |        |               |

# Light [43]

- Author: Natnael Atnafu

- Description: Enables the light when the correct combination of switches are on

- GitHub repository

- Wokwi project

- Mux address: 43

- Extra docs

- Clock: 0 Hz

### How it works

Put the correct combination of switches to make the light turn on

### How to test

Turn some switches on or off to see which ones make the light turn on

## External hardware

LED light, 7 segment display

| # | Input         | Output        | Bidirectional |

|---|---------------|---------------|---------------|

| 0 | goes to       | comes from    |               |

|   | output w      | input w same  |               |

|   | same number   | number        |               |

| 1 | goes to       | comes from    |               |

|   | output w      | input w same  |               |

|   | same number   | number        |               |

| 2 | goes to       | comes from    |               |

|   | output w      | input w same  |               |

|   | same number   | number        |               |

| 3 | goes to or    | comes from or |               |

|   | gate, goes to | gate, from 3  |               |

|   | output 3 and  | or 4          |               |

|   | 4             |               |               |

| # | Input                                            | Output                                  | Bidirectional |

|---|--------------------------------------------------|-----------------------------------------|---------------|

| 4 | goes to or<br>gate, goes to<br>output 3 and<br>4 | comes from or<br>gate, from 3<br>or 4   |               |

| 5 | goes to<br>output w<br>same number               | comes from<br>input w same<br>number    |               |

| 6 | goes to not<br>gate w same<br>number             | comes from<br>not gate w<br>same number |               |

| 7 |                                                  |                                         |               |

## TinyTapeOut [44]

- Author: Siyem Russom

- Description: Tiny Tapeout

- GitHub repository

- Wokwi project

- Mux address: 44

- Extra docs

- Clock: 0 Hz

#### How it works

If sel is high, then a counter is output on the output pins and the bidirectional pins  $(data_o = counter_o = counter)$ . If sel is low, the bidirectional pins are mirrored to the output pins  $(data_o = data_i)$ .

#### How to test

Set sel high and observe that the counter is output on the output pins (data\_o) and the bidirectional pins (counter\_o). Set sel low and observe that the bidirectional pins are mirrored to the output pins (data\_o = data\_i)

## External hardware

No external hardware used in my project.

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 0 | IN0   | OUT0   |               |

| 1 | IN1   | OUT1   |               |

| 2 | IN2   | OUT2   |               |

| 3 | IN3   | OUT3   |               |

| 4 | IN4   | OUT4   |               |

| 5 | IN5   | OUT5   |               |

| 6 | IN6   | OUT6   |               |

| 7 | IN7   | OUT7   |               |

## Nathan's chip [45]

- Author: Nathineal

- Description: 1 0 outcome

- GitHub repository

- Wokwi project

- Mux address: 45

- Extra docs

- Clock: 0 Hz

### How it works

If sel is high, then a counter is output on the output pins and the bidirectional pins  $(data_o = counter_o = counter)$ . If sel is low, the bidirectional pins are mirrored to the output pins  $(data_o = data_i)$ .

#### How to test

Set sel high and observe that the counter is output on the output pins (data\_o) and the bidirectional pins (counter\_o). Set sel low and observe that the bidirectional pins are mirrored to the output pins (data\_o = data\_i).

## External hardware

sdfsf List external hardware used in your project (e.g. PMOD, LED display, etc), if any There is none

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 0 | IN0   | OUT0   |               |

| 1 | IN1   | OUT1   |               |

| 2 | IN2   | OUT2   |               |

| 3 | IN3   | OUT3   |               |

| 4 | IN4   | OUT4   |               |

| 5 | IN5   | OUT5   |               |

| 6 | IN6   | OUT6   |               |

| 7 | IN7   | OUT7   |               |

# OR gate [46]

- Author: Joe Merriam

- Description: makes seven segment spell J

- GitHub repository

- Wokwi project

- Mux address: 46

- Extra docs

- Clock: 10000 Hz

#### How it works

We use the OR gate to generate the letter J on the seven segment LED.

#### How to test

Flip the switches to generate the letter J

#### **External hardware**

List external hardware used in your project (e.g. PMOD, LED display, etc), if any

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 0 | IN0   | OUT0   |               |

| 1 | IN1   | OUT1   |               |

| 2 | IN2   | OUT2   |               |

| 3 | IN3   | OUT3   |               |

| 4 | IN4   | OUT4   |               |

| 5 | IN5   | OUT5   |               |

| 6 | IN6   | OUT6   |               |

| 7 | IN7   | OUT7   |               |

|   |       |        |               |

## project [47]

- Author: ahmad

- Description: diagram

- GitHub repository

- Wokwi project

- Mux address: 47

- Extra docs

- Clock: 0 Hz

### How it works

dsign contain four inverts .four inputs are directly connected to outputs and rest to outputs and rest of them are inverted.

#### How to test

just toggle the inputs.

### External hardware

no external hardware

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 0 | IN0   | OUT0   |               |

| 1 | IN1   | OUT1   |               |

| 2 | IN2   | OUT2   |               |

| 3 | IN3   | OUT3   |               |

| 4 | IN4   | OUT4   |               |

| 5 | IN5   | OUT5   |               |

| 6 | IN6   | OUT6   |               |

| 7 | IN7   | OUT7   |               |

## D\_flipflop\_hold\_test [64]

- Author: Nicole Ramirez

- Description: hold time violated for D Flip\_flop NAND Logic

- GitHub repository

- Wokwi project

- Mux address: 64

- Extra docs

- Clock: 0 Hz

#### How it works

NAND logic circuit for flipflop violates hold time and set time (theortically) with the resistor

#### How to test

flipping switches

#### External hardware

Switches List external hardware used in your project (e.g. PMOD, LED display, etc), if any LEDs(6)

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 0 | IN0   | OUT0   |               |

| 1 | IN1   | OUT1   |               |

| 2 | IN2   | OUT2   |               |

| 3 | IN3   | OUT3   |               |

| 4 | IN4   | OUT4   |               |

| 5 | IN5   | OUT5   |               |

| 6 | IN6   | OUT6   |               |

| 7 | IN7   |        |               |

## Dipankar's first Wowki design [65]