# Tiny Tapeout IHP 0p2 Datasheet

Project Repository https://github.com/TinyTapeout/tinytapeout-ihp-0p2

April 25, 2025

Contents

| Chip renders                                                                                                                |      |    |   |   |     | 5   |

|-----------------------------------------------------------------------------------------------------------------------------|------|----|---|---|-----|-----|

| Full chip render                                                                                                            |      |    |   |   |     | 5   |

| Top Metal $1/2$                                                                                                             |      |    |   |   |     | 6   |

| Logic density view                                                                                                          | •••  |    |   | • | • • | 7   |

| Projects                                                                                                                    |      |    |   |   |     | 8   |

| Chip ROM [0]                                                                                                                |      |    |   |   |     | 8   |

| TinyTapeout Factory Test 1                                                                                                  |      |    |   |   |     | 10  |

| $ROTFPGA v2a 2 \dots \dots$ |      |    |   |   |     | 12  |

| VGA Screensaver with Tiny Tapeout Logo [3]                                                                                  |      |    |   |   |     | 20  |

| KianV RISC-V RV32E Baremetal SoC [10]                                                                                       |      |    |   |   |     | 22  |

| Game of Life 8x32 (siLife) [11]                                                                                             |      |    |   |   |     | 24  |

| simon_cipher [32]                                                                                                           |      |    |   |   |     | 26  |

| ROTFPGA v2b [33]                                                                                                            |      |    |   |   |     | 28  |

| Asynchronous Multiplier [35]                                                                                                |      |    |   |   |     | 30  |

| SRAM (1024x8) test [39]                                                                                                     |      |    |   |   |     | 33  |

| Zilog Z80 [43]                                                                                                              |      |    |   |   |     | 35  |

| Minilogix [70]                                                                                                              |      |    |   |   |     | 39  |

| VGA donut [74]                                                                                                              |      |    |   |   |     | 40  |

| VC 16-bit CPU [75]                                                                                                          |      |    |   |   |     | 42  |

| VGA Pong with NES Controllers [97]                                                                                          |      |    |   |   |     | 43  |

| DemoSiine [99]                                                                                                              |      |    |   |   |     | 45  |

| Rounding error [101]                                                                                                        |      |    |   |   |     | 54  |

| VGA Pride [103]                                                                                                             |      |    |   |   |     | 60  |

| VGA Nyan Cat [105]                                                                                                          |      |    |   |   |     | 64  |

| Flame demo [107]                                                                                                            |      |    |   |   |     | 66  |

| INTERCAL ALU [128]                                                                                                          |      |    |   |   |     | 68  |

| Classic 8-bit era Programmable Sound Generator AY-3-8913                                                                    | [161 | [] |   |   |     | 73  |

| Digital Desk Clock v2.0 [163]                                                                                               |      |    |   |   |     | 82  |

| Giant Ring Oscillator (3853 inverters) [165]                                                                                |      |    |   |   |     | 84  |

| DDR throughput and flop aperature test [167]                                                                                |      |    |   |   |     | 86  |

| Example of Bad Synchronizer [169]                                                                                           | • •  |    |   | • |     | 88  |

| Gray scale and Sobel filter [171]                                                                                           |      |    |   |   |     |     |

| Snow [225]                                                                                                                  |      |    | • |   | • • | 92  |

| 8-bit ALU based on 2x 74181 [227]                                                                                           |      |    |   |   |     |     |

| VGA Tiny Logo (1 tile) [229]                                                                                                |      |    |   |   |     |     |

| SkyKing Demo [231]                                                                                                          |      |    |   |   |     |     |

| Cell mux [233]                                                                                                              |      |    |   |   |     |     |

| Power gating test $(1\times 1)$ [235]                                                                                       |      |    |   |   |     |     |

| Simon's Caterpillar [256]                                                                                                   |      |    |   |   |     |     |

| TT08 Pachelbel's Canon demo [258]                                                                                           |      |    |   |   |     |     |

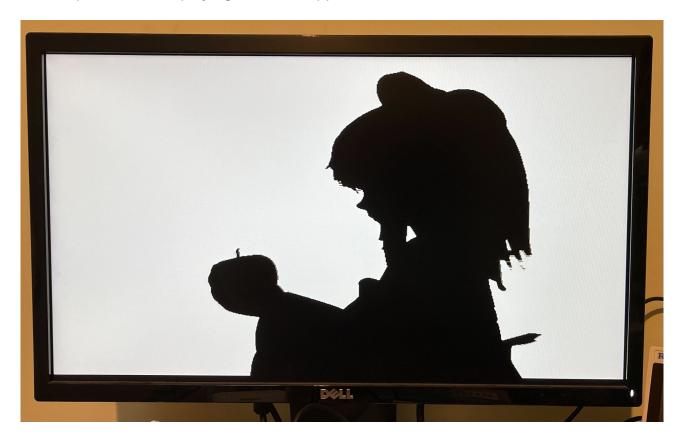

| Demo by a1k0n [260]                                                                                                         |      |    |   |   |     | 105 |

| VGA Drop (audio/visual demo) [262]          | 108 |

|---------------------------------------------|-----|

|                                             | 109 |

|                                             | 111 |

| Glyph Mode [288]                            | 112 |

| cfib Demoscene Entry [290]                  | 114 |

|                                             | 116 |

| Pulse Width Counter [294]                   | 117 |

| Ring Oscillator (5 inverter) [296]          | 118 |

|                                             | 119 |

|                                             | 121 |

| Frequency Counter SSD1306 OLED [324]        | 124 |

|                                             | 126 |

| Collatz conjecture brute-forcer [328]       | 128 |

| Power gating test (1x2) [330]               | 130 |

|                                             | 131 |

| TTL Pulse Generator [354]                   | 132 |

|                                             | 133 |

|                                             | 135 |

|                                             | 136 |

|                                             | 138 |

| Conway's Game of Life on UART and VGA [388] | 140 |

|                                             | 142 |

| 2048 sliding tile puzzle game (VGA) [421]   | 174 |

|                                             | 176 |

|                                             | 181 |

| Experiment Number Six: Laplace LUT [450]    | 185 |

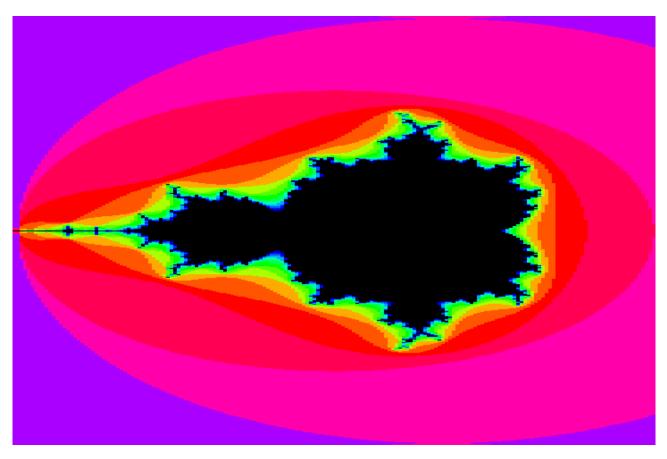

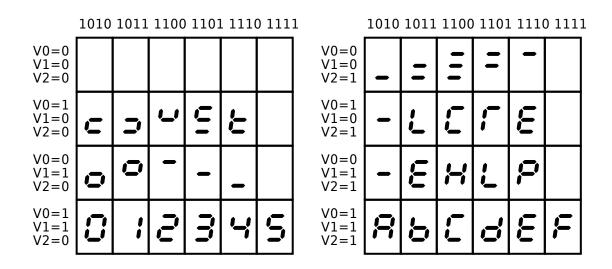

| VGA Mandelbrot [454]                        | 188 |

| mulmul [458]                                | 191 |

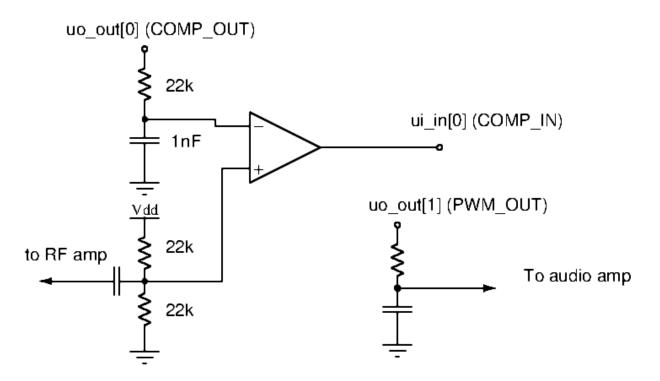

| 1bit_am_sdr [485]                           | 193 |

| Goldcrest RISC-V [490]                      |     |

| Chess [491]                                 | 199 |

| VGA clock [513]                             | 202 |

| TinyQV Risc-V SoC [514]                     | 204 |

| RGB Mixer demo [515]                        | 208 |

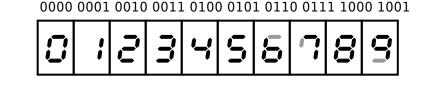

| Universal Binary to Segment Decoder [517]   |     |

| Hardware UTF Encoder/Decoder [519]          | 218 |

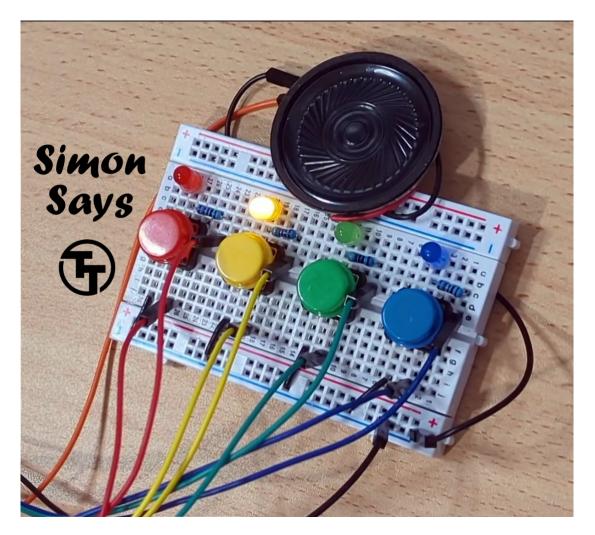

| Simon Says memory game [521]                | 224 |

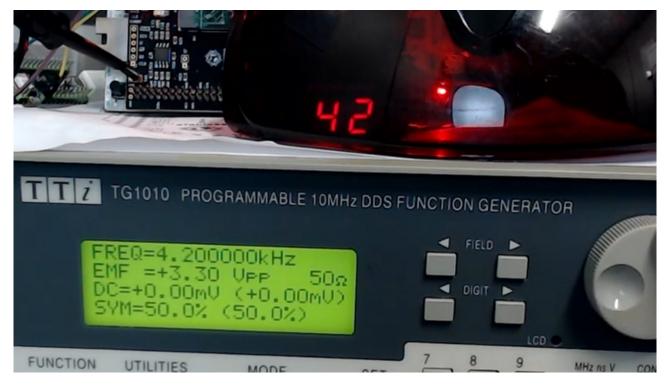

| No Time For Squares, IHP edition [522]      | 227 |

| Latch test [523]                            |     |

| Transmit UART [545]                         |     |

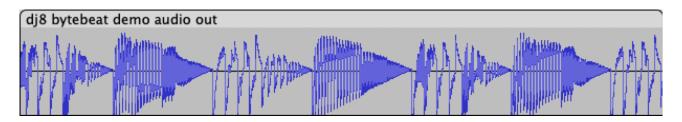

| DJ8 8-bit CPU [547]                         | 231 |

|                                             | 237 |

| RLE Video Player [551]VGA Experiments in Tennis [553]8 bit RSA encryption [555]Frequency counter [577]SPI Test [579]One Sprite Pony [581]raybox-zero TTIHP0p2 edition [582]I2C EEPROM Project Selection [583]Color Bars [585]Sequential Shadows Deluxe [TT08 demo competition] [586]Crispy VGA [587]Stochastic Multiplier, Adder and Self-Multiplier [609]8 Bit Digital QIF [611]CEJMU Beers and Adders [613]Classic 8-bit era Programmable Sound Generator SN76489 [615]MULDIV unit (8-bit signed/unsigned) [617]IHP loopback tile with input skew measurement [619] | 242<br>244<br>249<br>251<br>253<br>255<br>258<br>260<br>262<br>265<br>267<br>272<br>273<br>273<br>275<br>283 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

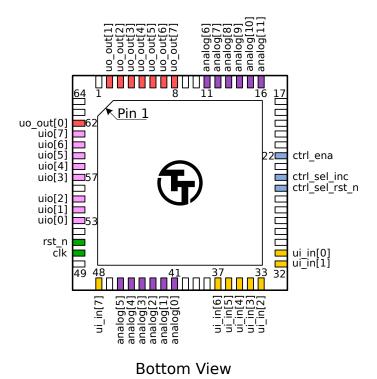

| Pinout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 289                                                                                                          |

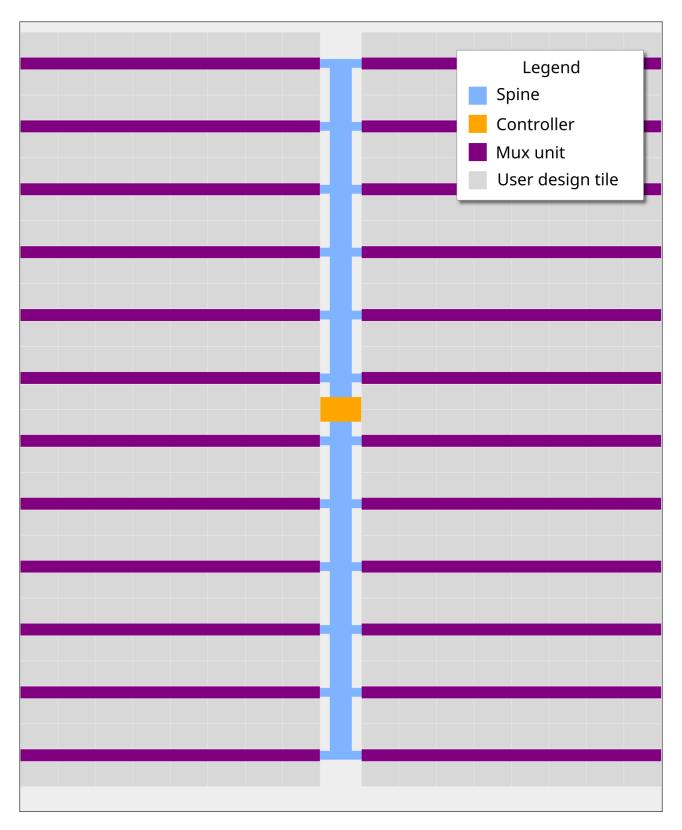

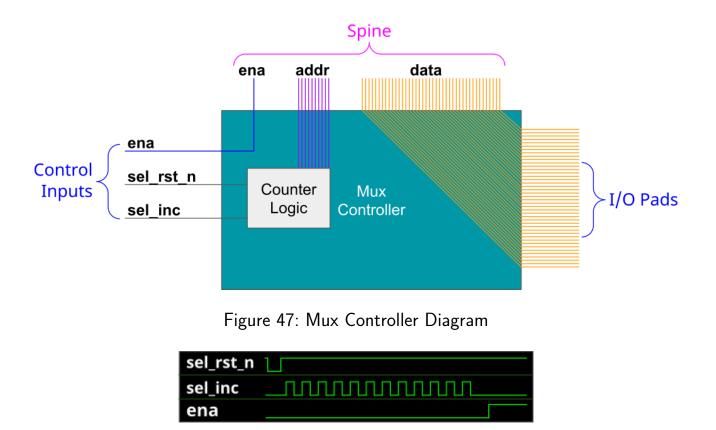

| The Tiny Tapeout Multiplexer       2         Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 290                                                                                                          |

| Funding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 296                                                                                                          |

| Team 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 296                                                                                                          |

# **Chip renders**

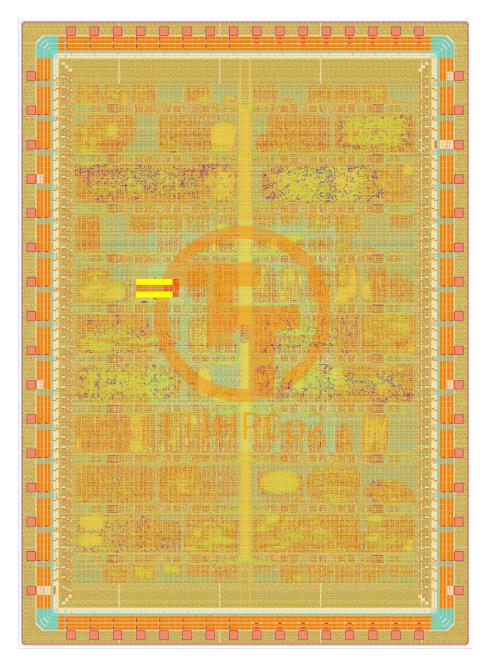

# Full chip render

Figure 1: GDS render

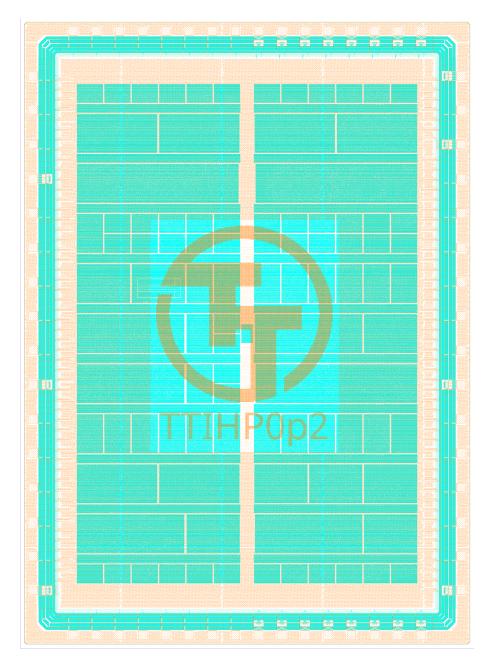

# Top Metal 1/2

Figure 2: TopMetal1/2 render

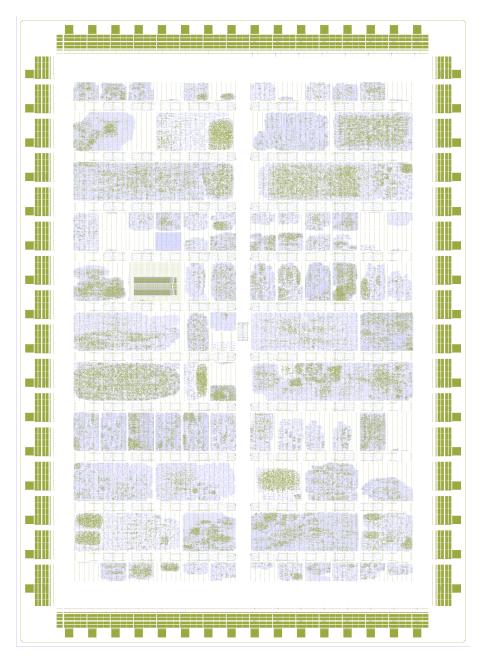

# Logic density view

Figure 3: Logic density

# Projects

### Chip ROM [0]

- Author: Uri Shaked

- Description: ROM with information about the chip

- GitHub repository

- HDL project

- Mux address: 0

- Extra docs

- Clock: 0 Hz

#### How it works

ROM memory that contains information about the Tiny Tapeout chip. The ROM is 8-bit wide and 256 bytes long.

| Address | Length | Encoding  | Description                               |

|---------|--------|-----------|-------------------------------------------|

| 0       | 8      | 7-segment | Shuttle name (e.g. ''tt07''), null-padded |

| 8       | 8      | 7-segment | Git commit hash                           |

| 32      | 96     | ASCII     | Chip descriptor (see below)               |

| 248     | 4      | binary    | Magic value: "TT $xFAxBB$ "               |

| 252     | 4      | binary    | CRC32 of the ROM contents, little-endian  |

**The ROM layout** The ROM layout is as follows:

**The chip descriptor** The chip descriptor is a simple null-terminated string that describes the chip. Each line is a key-value pair, separated by an equals sign. It contains the following keys:

| Key  | Description                                                                      | Example value                                  |

|------|----------------------------------------------------------------------------------|------------------------------------------------|

| repo | The identifier of the shuttle<br>The name of the repository<br>The commit hash * | tt07<br>TinyTapeout/tinytapeout-07<br>a1b2c3d4 |

• The commit hash is only included for Tiny Tapeout 5 and later.

Here is a complete example of a chip descriptor:

```

shuttle=tt07

repo=TinyTapeout/tinytapeout-07

commit=a1b2c3d4

```

**How the ROM is generated** The ROM is automatically generated by tt-supporttools while building the final GDS file of the chip. Look at the rom.py file in the repository for more details.

#### How to test

Read the ROM contents by setting the address pins and reading the data pins. The first 16 bytes of the ROM are 7-segment encoded and contain the shuttle name and commit hash. You can read them by toggling the first four DIP switches and observing the on-board 7-segment display.

| # | Input   | Output  | Bidirectional |

|---|---------|---------|---------------|

| 0 | addr[0] | data[0] |               |

| 1 | addr1   | data1   |               |

| 2 | addr2   | data2   |               |

| 3 | addr[3] | data[3] |               |

| 4 | addr[4] | data[4] |               |

| 5 | addr[5] | data[5] |               |

| 6 | addr[6] | data[6] |               |

| 7 | addr[7] | data[7] |               |

### TinyTapeout Factory Test 1

- Author: Tiny Tapeout

- Description: Factory test module

- GitHub repository

- HDL project

- Mux address: 1

- Extra docs

- Clock: 0 Hz

### How it works

The factory test module is a simple module that can be used to test all the  $\rm I/O$  pins of the ASIC.

It has three modes of operation:

- 1. Mirroring the input pins to the output pins (when rst\_n is low).

- 2. Mirroring the bidirectional pins to the output pins (when rst\_n is high sel is low).

- 3. Outputing a counter on the output pins and the bidirectional pins (when rst\_n is high and sel is high).

The following table summarizes the modes:

| rst_n | sel | Mode                        | uo_out value | uio pins |

|-------|-----|-----------------------------|--------------|----------|

| 0     | Х   | Input mirror                | ui_in        | High-Z   |

| 1     | 0   | <b>Bidirectional mirror</b> | uio_in       | High-Z   |

| 1     | 1   | Counter                     | counter      | counter  |

The counter is an 8-bit counter that increments on every clock cycle, and resets when rst\_n is low.

#### How to test

- 1. Set rst\_n low and observe that the input pins (ui\_in) are output on the output pins (uo\_out).

- 2. Set rst\_n high and sel low and observe that the bidirectional pins (uio\_in) are output on the output pins (uo\_out).

- 3. Set sel high and observe that the counter is output on both the output pins (uo\_out) and the bidirectional pins (uio).

| # | Input         | Output                    | Bidirectional        |

|---|---------------|---------------------------|----------------------|

| 0 | sel / in_a[0] | output[0] /<br>counter[0] | in_b[0] / counter[0] |

| 1 | in_a1         | output1 / counter1        | in_b1 / counter1     |

| 2 | in_a2         | output2 /<br>counter2     | in_b2 / counter2     |

| 3 | in_a[3]       | output[3] /<br>counter[3] | in_b[3] / counter[3] |

| 4 | in_a[4]       | output[4] /<br>counter[4] | in_b[4] / counter[4] |

| 5 | in_a[5]       | output[5] /<br>counter[5] | in_b[5] / counter[5] |

| 6 | in_a[6]       | output[6] /<br>counter[6] | in_b[6] / counter[6] |

| 7 | in_a[7]       | output[7] /<br>counter[7] | in_b[7] / counter[7] |

### ROTFPGA v2a 2

- Author: htfab

- Description: A reconfigurable logic circuit made of identical rotatable tiles

- GitHub repository

- HDL project

- Mux address: 2

- Extra docs

- Clock: 10000000 Hz

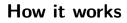

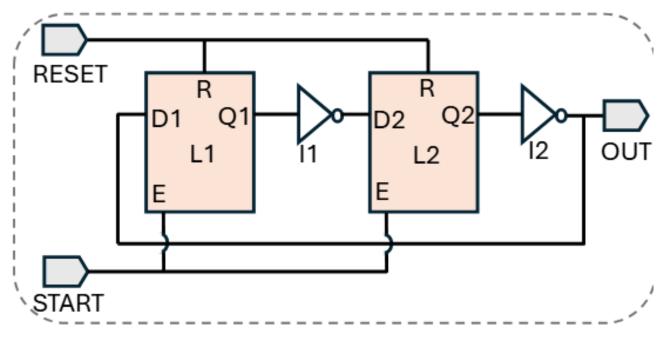

#### How it works

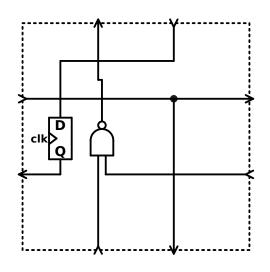

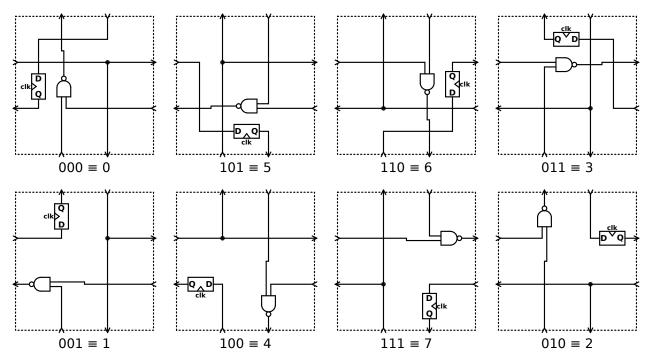

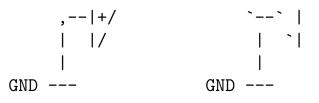

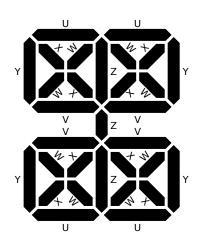

Figure 4: Logic tile

A reconfigurable logic circuit built from identical copies of the tile above containing a NAND gate, a D flip-flop and a buffer, with each tile individually rotated or reflected as described by the FPGA configuration. Port of the original ROTFPGA from Caravel to TinyTapeout.

Porting the design required a 50-fold decrease in chip area which was achieved using a combination of cutting corners, heavy optimization and a few design changes. In particular:

- The FPGA was reduced from 24×24 to 8×8 tiles. There are 8 inputs and 8 outputs instead of 12 each.

- To compensate for smaller size, tiles can also be mirrored in addition to rotation.

- Tiles (being the most repeated part of the design) were rewritten as handoptimized gate-level Verilog.

- Each tile only contains 1 flip-flop (the one exposed to the user). Configuration is now stored in latches.

- Configuration and reset are performed using a routing-efficient scan chain, so the design is no longer routing constrained. This allows standard cells to be placed with >80% density.

- Openlane and its components are 2 years more mature, hardening the same HDL more efficiently.

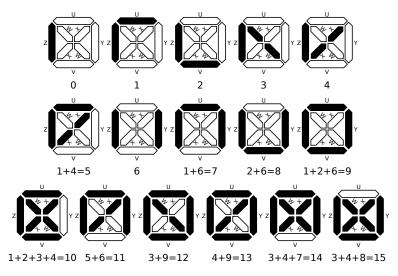

**Configuration** Each tile can be configured in 8 possible orientations. Bits 0, 1 and 2 correspond to a diagonal, horizontal and vertical flip respectively. Any rotation or reflection can be described as a combination:

(The bottom row looks somewhat different, but we just rearranged the wires so that the inputs and outputs line up with the unmirrored tiles.)

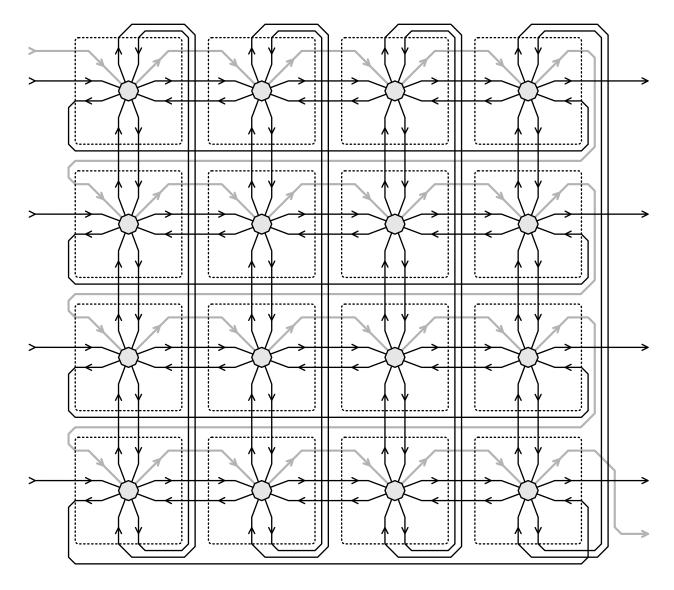

Tiles are arranged in an  $8 \times 8$  grid:

- Top, bottom, left and right inputs and outputs are connected to the tile in the respective direction.

- Tiles mostly wrap around, e.g. the bottom output of a cell in the last line connects to the top input of the cell in the first line.

- As an exception to the wrapping rules, left inputs in the first column correspond to chip inputs and right outputs in the last column correspond to chip outputs.

- There is a scan chain meandering through all the tiles, visiting lines from top to bottom and within each line going from left to right.

This is a  $4 \times 4$  model of the tile grid, showing regular i/o as black and the scan chain as grey:

Figure 5: Grid model

When the *scan enable* input is 0, the FPGA operates normally and each tile sets its flipflop to the input it receives from one of the neighboring tiles according to its current rotation/reflection. When *scan enable* is 1, it sets the flip-flop to the value received through the scan chain instead. This allows us to set the initial state of each flip-flop and also to query their state later for debugging. With some extra machinery it also allows us to change the rotations/reflections.

When the 2-bit *configuration* input is is 01, each cell updates its *vertical flip* bit to the current value of its flip-flop. Similarly, for 10 it sets the *horizontal flip* and for 11 it sets the *diagonal flip*. When *configuration* is 00, all three flip bits are latched and the orientation doesn't change.

One can thus configure the FPGA by sending the sequence of all diagonal flip bits

through the scan chain, then setting *configuration* to 11 and back to 00, then sending all *horizontal flip* bits, setting *configuration* to 10 and back to 00, and finally sending the *vertical flip* bits and setting *configuration* to 01 and back to 00.

Note that in order to save space the flip bits are stored in latches, not registers. Changing the *configuration* input from 00 to 11 or vice versa can cause a race condition where it is temporarily 01 or 10, overwriting the horizontal or vertical flip bits. Therefore one should configure the diagonal flips first.

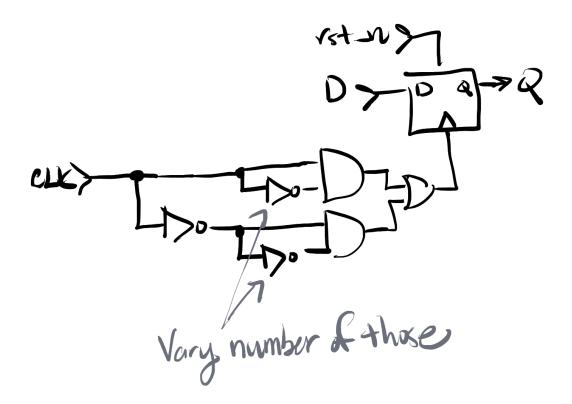

**Loop breaker** The user design may intentionally or inadvertantly contain combinational loops such as ring oscillators. To help debug such designs, the chip has a loop breaker mechanism using a *loop breaker enable* input as well as a 2-bit *loop breaker class* input.

Tiles are assigned to loop breaker classes:

| 00 |    | 11 |    | 00 |    | 11 |    |

|----|----|----|----|----|----|----|----|

|    | 10 |    | 01 |    | 10 |    | 01 |

| 11 |    | 00 |    | 11 |    | 00 |    |

|    | 01 |    | 10 |    | 01 |    | 10 |

| 00 |    | 11 |    | 00 |    | 11 |    |

|    | 10 |    | 01 |    | 10 |    | 01 |

| 11 |    | 00 |    | 11 |    | 00 |    |

|    | 01 |    | 10 |    | 01 |    | 10 |

Figure 6: Loop breaker tile classes

The loop breaker latches a tile output if and only if the following conditions are all met:

- The *loop breaker enable* input is 1.

- The current tile has a non-empty class that is different from the *loop breaker class* input.

- The output doesn't come from the tile's flip-flop.

The loop breaker has the following properties:

- If *loop breaker enable* is 1 and *loop breaker class* is constant, there are no combinational loops running. If we also pause the clock, the circuit keeps a steady state.

- If *loop breaker enable* is 1 and we cycle *loop breaker class* through all possible values repeatedly while the clock is paused, everything will eventually propagate. If we also assume that the design has no race conditions, it will behave in the same way as if *loop breaker enable* was 0.

**Reset** Setting the *active-low reset* input to 0 has the following effect:

- Override scan enable to 1, scan chain input to 0 and disengage the latches for vertical, horizontal and diagonal flips. When kept low for 64 clock cycles this will reset the state and configuration in every tile.

- Override *loop breaker enable* to 1 and *loop breaker class* to 00. This ensures that we play nice with other designs on TinyTapeout and keep a steady state while our design is not selected.

**Pin mapping** Input pins:

- clk provides a clock signal for the flip-flops

- rst\_n is the active-low reset described above

- ui\_in[7:0] are passed to the leftmost column of tiles as inputs from the left

Output pins:

• uo\_out [7:0] come from the rightwards output of the rightmost column of tiles

Bidirectional pins:

- uio\_in[0] is the scan enable input

- uio\_in[1] is the *scan chain* input

- uio\_in[3:2] are the *configuration* input bits

- uio\_in[4] is the loop breaker enable input

- uio\_in[6:5] are the *loop breaker class* input bits

- uio\_out[7] is the scan chain output

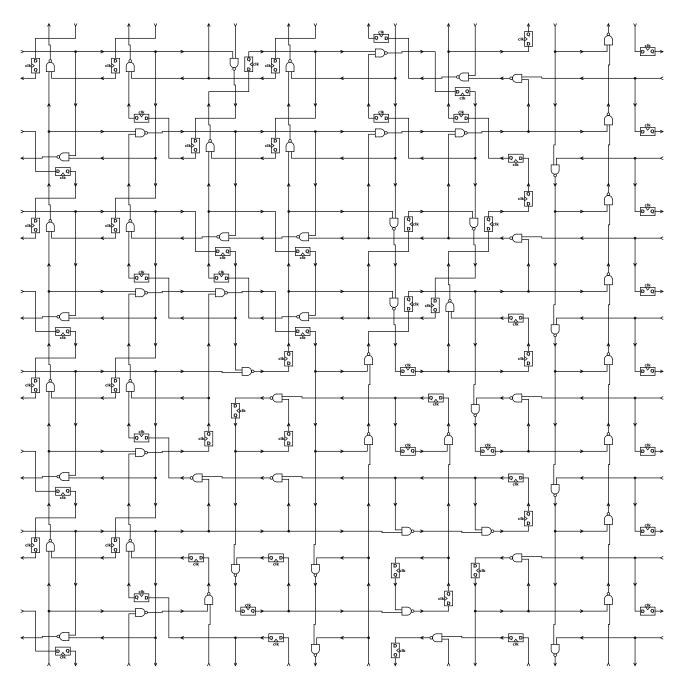

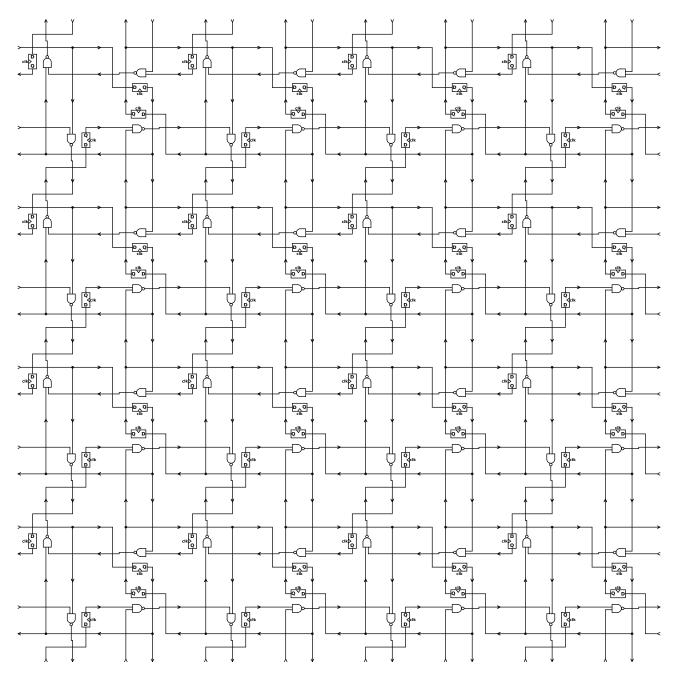

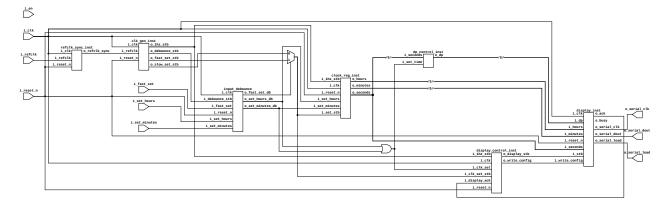

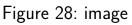

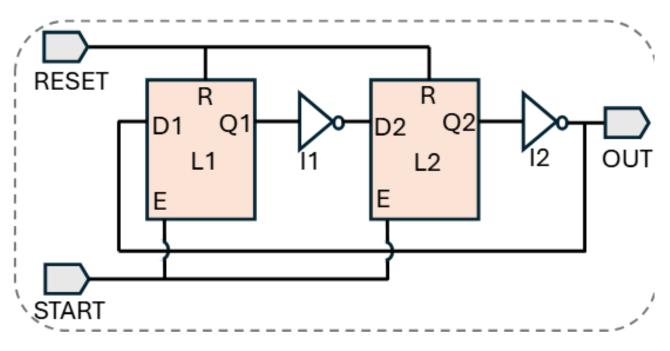

Figure 7: Diagram corresponding to  $fpga\_config$  in test.py

### How to test

Follow the test suite the test directory. It sets up the FPGA with the following two configurations and runs a battery of tests on each.

Test configuration 1 used for upload, download, single-step and propagation tests:

Test configuration 2 used for testing the loop breaker with manual and automatic cycles:

Figure 8: Diagram corresponding to cfg from the loop breaker test in test.py

### External hardware

None

| # | Input             | Output          | Bidirectional                    |

|---|-------------------|-----------------|----------------------------------|

| 0 | tile(0,0) left    | tile(7,0) right | scan enable input                |

|   | in                | out             |                                  |

| 1 | tile $(0,1)$ left | tile(7,1) right | <i>scan chain</i> input          |

|   | in                | out             |                                  |

| 2 | tile(0,2) left    | tile(7,2) right | configuration input bit 0        |

|   | in                | out             |                                  |

| 3 | tile(0,3) left    | tile(7,3) right | configuration input bit 1        |

|   | in                | out             |                                  |

| 4 | tile(0,4) left    | tile(7,4) right | <i>loop breaker enable</i> input |

|   | in                | out             |                                  |

| 5 | tile(0,5) left    | tile(7,5) right | loop breaker class input bit     |

|   | in                | out             | 0                                |

| 6 | tile(0,6) left    | tile(7,6) right | loop breaker class input bit     |

|   | in                | out             | 1                                |

| 7 | tile(0,7) left    | tile(7,7) right | <i>scan chain</i> output         |

|   | in                | out             |                                  |

### VGA Screensaver with Tiny Tapeout Logo [3]

- Author: Uri Shaked

- Description: Tiny Tapeout Logo bouncing around the screen (640x480, TinyVGA Pmod)

- GitHub repository

- HDL project

- Mux address: 3

- Extra docs

- Clock: 25175000 Hz

### How it works

Displays a bouncing Tiny Tapeout logo on the screen, with animated color gradient.

Figure 9: Tiny Tapeout screensaver

### How to test

Connect to a VGA monitor. Set the following inputs to configure the design:

- tile (ui\_in[0]) to repeat the logo and tile it across the screen,

- solid\_color (ui\_in1) to use a solid color instead of an animated gradient.

### External hardware

### TinyVGA PMOD

| # | Input       | Output | Bidirectional |

|---|-------------|--------|---------------|

| 0 | tile        | R1     |               |

| 1 | solid_color | G1     |               |

| 2 |             | B1     |               |

| 3 |             | VSync  |               |

| 4 |             | R0     |               |

| 5 |             | G0     |               |

| 6 |             | B0     |               |

| 7 |             | HSync  |               |

### KianV RISC-V RV32E Baremetal SoC [10]

- Author: Dipl.-Ing. Hirosh Dabui

- Description: A baremetal RISC-V RV32E ASIC with audio, spi, uart

- GitHub repository

- HDL project

- Mux address: 10

- Extra docs

- Clock: 50000000 Hz

### How it works

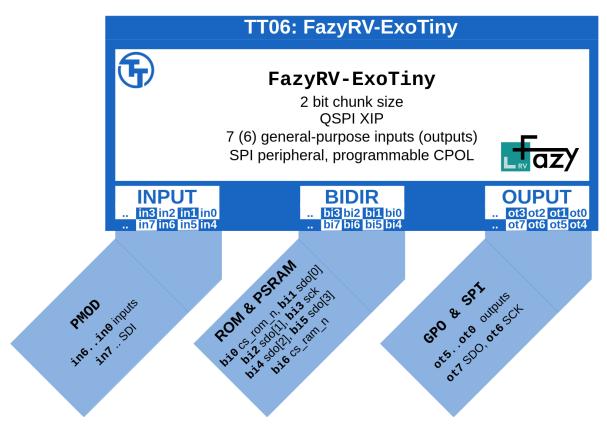

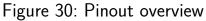

After implementing a KianV uLinux TT06, I felt like implementing a KianV bare metal edition, which is an RV32E RISC-V32 SoC. This SoC is equipped with a UART, qspi memory controller (psram/flash), a generic SPI interface, and a sigma-delta emulator for playing audio files. In the firmware folder, the kernelboot.c and crt0.S files display all hardware registers and their initialization in the code.

#### How to test

First, one must build the toolchain for an RV32E, as you can see here:

```

sudo apt-get update

sudo apt-get install autoconf automake autotools-dev curl python3 libmpc-

git clone --recursive https://github.com/riscv/riscv-gnu-toolchain.git

cd riscv-gnu-toolchain

./configure --prefix=/opt/riscv32e --with-arch=rv32e --with-abi=ilp32e

make

export PATH=/opt/riscv32e/bin:$PATH

```

The following hardware addresses are given:

```

#define LSR_DR 0x01

#define LSR_TEMT 0x40

#define LSR_THRE 0x20

#define PWM_ADDR (IO_BASE + 0x14)

#define REG_DIV (IO_BASE + 0x10)

#define SPI_DIV (IO_BASE + 0x500010)

#define UART_LSR (IO_BASE + 0x5)

```

#define UART\_RX (IO\_BASE)

#define UART\_TX (IO\_BASE)

The use of the registers can be determined from the C, linker script and assembly program. The CPU starts to execute the instruction stored in the NOR Flash at an offset of 1MiB. When the chip comes into my hands, I will provide demos that I test on the chip, including audio playback with appropriate documentation.

### External hardware

It's very important to use the PMOD Flash + PSRAM. We only use 8MB of PSRAM address space.

| # | Input             | Output            | Bidirectional |

|---|-------------------|-------------------|---------------|

| 0 | uart_rx           | spi_cen0          | ce0 flash     |

| 1 | spi_sio1_so_miso0 | spi_sclk0         | sio0          |

| 2 |                   | spi_sio0_si_mosi0 | sio1          |

| 3 |                   | pwm_o             | sck           |

| 4 |                   | uart_tx           | sd2           |

| 5 |                   | led[0]            | sd3           |

| 6 |                   | led1              | cs1 psram     |

| 7 |                   | led2              | always high   |

|   |                   |                   |               |

# Game of Life 8x32 (siLife) [11]

- Author: Uri Shaked

- Description: Silicon implementation of Conway's Game of Life with LED Dot Matrix Output

- GitHub repository

- HDL project

- Mux address: 11

- Extra docs

- Clock: 10000000 Hz

### How it works

It is a silicon implementation of Conway's Game of Life. The game is played on a 8x32 grid, and the rules are as follows:

- Any live cell with fewer than two live neighbours dies, as if by underpopulation.

- Any live cell with two or three live neighbours lives on to the next generation.

- Any live cell with more than three live neighbours dies, as if by overpopulation.

- Any dead cell with exactly three live neighbours becomes a live cell, as if by reproduction.

### How to test

Demo mode: The demo mode loads a pre-defined game into the grid and advances it automatically. To enter the demo mode, wr\_en high while reseting the design (rst\_n low). Use the pattern\_sel inputs to select the desired demo pattern. Set en to 1 to automatically advance one generation every 0.4 seconds (assuming a 10MHz clock). To pause the game, set en to 0.

Manual mode: Load the initial grid row by row. Each row is loaded by selecting the row number (using the row\_sel[4:0] inputs), setting the cell\_in[7:0] inputs to the desired state, and pulsing the wr\_en input.

Once the grid is loaded, set the en input to 1 to start the game. The game will advance one step in each clock cycle. To pause the game, set the en input to 0.

To view the current state of the grid, set the row\_sel[4:0] inputs to the desired row number, max7219\_en to 0, and read the cell\_out[7:0] outputs.

Alternatively, set max7129\_en to 1 to display the grid on a MAX7219 LED Matrix (FC-16 module).

### External Hardware

MAX7219 LED Matrix (FC-16 module)

| # | Input                       | Output                      | Bidirectional |

|---|-----------------------------|-----------------------------|---------------|

| 0 | row_sel[0] /<br>pattern_sel | cell_out[0] /<br>max7129_cs | cell_in[0]    |

| 1 | row_sel1                    | cell_out1 /<br>max7129_clk  | cell_in1      |

| 2 | rol_sel2                    | cell_out2 /<br>max7129_din  | cell_in2      |

| 3 | rol_sel[3]                  | cell_out[3]                 | cell_in[3]    |

| 4 | rol_sel[4]                  | cell_out[4]                 | cell_in[4]    |

| 5 | max7129_en                  | cell_out[5]                 | cell_in[5]    |

| 6 | en                          | cell_out[6]                 | cell_in[6]    |

| 7 | wr_en                       | cell_out[7]                 | cell_in[7]    |

### simon\_cipher [32]

- Author: Simon Cipher

- Description: Bitserial implementation of Simon-128

- GitHub repository

- HDL project

- Mux address: 32

- Extra docs

- Clock: 0 Hz

#### How it works

This is a bitserial implementation of the SIMON Block Cipher. SIMON is a 128-bit block cipher, see The SIMON and SPECK families of Lightweight Block Ciphers. A bit-serial implementation exchanges throughput for area, thereby creating a compact cipher that is dominated by flip-flops and multiplexer cells. However, the overal design size becomes minimal. A detailed description of the bitserial implementation technique for SIMON is available in SIMON Says, Break the Area Records for Symmetric Key Block Ciphers on FPGAs.

| Cell        | Count |

|-------------|-------|

| flip-flop   | 281   |

| mux         | 588   |

| other logic | 199   |

| TOTAL       | 1068  |

The design uses a 3-bit input and a 2-bit output, in addition to clock and reset.

| Port    | Function              |

|---------|-----------------------|

| ui[0]   | Bitserial Data Input  |

| ui[7:6] | Control Word          |

| uo[0]   | Bitserial Data Output |

| uo[7]   | Data Output Valid     |

The data input is asserted by the control word, and must be valid when the control word indicates a plaintext-loading or key-loading operation.

The data output is asserted by the valid bit, and should be ignored when the data valid bit is 0. The output ciphertext is produced in 128 consecutive clock cycles.

The 2-bit control word defines the operation of the cipher. The LSB is a debug bit study to key-loading process and to verify that the key register was correctly loaded.

| Control | Function                           |

|---------|------------------------------------|

| 00      | Idle                               |

| 01      | Load 128-bit plaintext             |

| 10      | Load 128-bit key (see LIMITATIONS) |

| 11      | Encrypt and return ciphertext      |

### LIMITATIONS

This design forces the key bits to 0 upon loading, so that the effective key value of the cipher is always hardcoded to 00000000\_00000000\_00000000\_00000000. This disables the use of the design as a cipher, yet it still demonstrates how a bit-serial architecture can be designed.

#### How to test

Study the testbench for example test vectors.

#### **External hardware**

No external hardware is needed for this project.

| # | Input    | Output    | Bidirectional |

|---|----------|-----------|---------------|

| 0 | ui_in[0] | uo_out[0] |               |

| 1 | ui_in1   | uo_out1   |               |

| 2 | ui_in2   | uo_out2   |               |

| 3 | ui_in[3] | uo_out[3] |               |

| 4 | ui_in[4] | uo_out[4] |               |

| 5 | ui_in[5] | uo_out[5] |               |

| 6 | ui_in[6] | uo_out[6] |               |

| 7 | ui_in[7] | uo_out[7] |               |

# ROTFPGA v2b [33]

- Author: htfab

- Description: A reconfigurable logic circuit made of identical rotatable tiles

- GitHub repository

- HDL project

- Mux address: 33

- Extra docs

- Clock: 10000000 Hz

### How it works

This design is a minor modification of ROTFPGA v2a, intended as a "control group" for testing latches on IHP. If ROTFPGA v2b works but v2a doesn't, it indicates an issue with latches. Otherwise it might be a problem with the design itself.

Most of the documentation carries over from ROTFPGA v2a and is not repeated here. The differences are:

- Latches are simulated using flip-flops

- Some inputs are combined to make room for two extra inputs

**Simulation of latches** Latches are replaced with flip-flops that operate on the "latch clock" whereas original flip-flops are modified to act on the "flop-flop clock".

In practice the "latch clock" and the "flip-flop clock" are gated versions of clk, enabled by in\_l\_gate and in\_ff\_gate respectively.

**Input reshuffling** To add in\_l\_gate and in\_ff\_gate to the inputs, the number of existing inputs had to be reduced. Since in\_cfg is typically only used when in\_se is high and in\_lbc is typically only used when in\_se is low, they were combined into in\_cfg\_lbc.

#### How to test

The changes above were incorporated into the test suite. Every clock tick in the original test was replaced by 50 "latch clocks" followed by a single "latch and flip-flop clock" and then by 50 more "latch clocks".

### External hardware

None

| # | Input          | Output          | Bidirectional                    |

|---|----------------|-----------------|----------------------------------|

| 0 | tile(0,0) left | tile(7,0) right | scan enable input                |

|   | in             | out             |                                  |

| 1 | tile(0,1) left | tile(7,1) right | <i>scan chain</i> input          |

|   | in             | out             |                                  |

| 2 | tile(0,2) left | tile(7,2) right | configuration / loop             |

|   | in             | out             | breaker class input bit 0        |

| 3 | tile(0,3) left | tile(7,3) right | configuration / loop             |

|   | in             | out             | <i>breaker class</i> input bit 1 |

| 4 | tile(0,4) left | tile(7,4) right | <i>loop breaker enable</i> input |

|   | in             | out             |                                  |

| 5 | tile(0,5) left | tile(7,5) right | clock gating for flip-flops      |

|   | in             | out             |                                  |

| 6 | tile(0,6) left | tile(7,6) right | clock gating for simulated       |

|   | in             | out             | latches                          |

| 7 | tile(0,7) left | tile(7,7) right | <i>scan chain</i> output         |

|   | in             | out             |                                  |

### Asynchronous Multiplier [35]

- Author: Tommy Thorn

- Description: An asynchronous multiplier

- GitHub repository

- HDL project

- Mux address: 35

- Extra docs

- Clock: 50000000 Hz

### How it works

This design emits a sequence of  $r = x^2+x$ , for x=0,1,2,... on the outputs using the handshake protocol (tie ack to req to get free running sequence). Well, in truth, we use 26-bits of internal precision, but we only have 15-bits for outputs, we what is actually emitted is  $r \uparrow (r >> 15)$ .

The very naive algorithm (with the body unrolled once) is

```

x = 0

loop:

x = x + 1

a = b = c = x

while b != 0:

if (b & 1) == 1:

c += a

a *= 2

b /= 2

if (b & 1) == 1:

c += a

a *= 2

b /= 2

b /= 2

output (c)

```

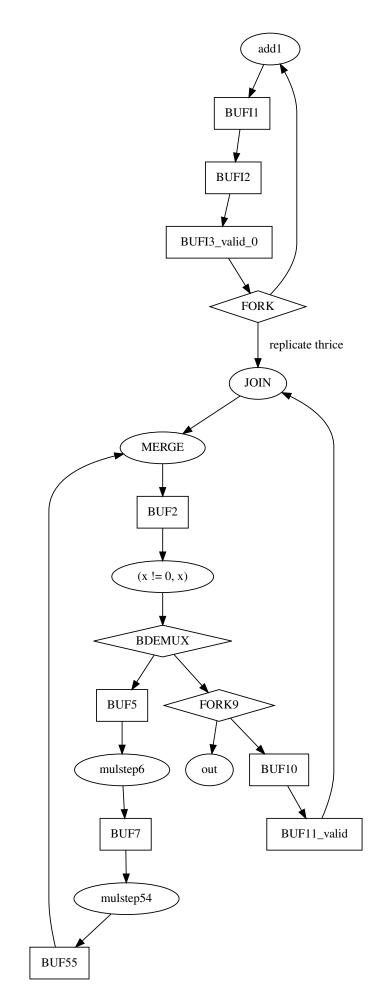

which was hand translated (roughly following Introduction to Asynchronous Circuit Design ) into a token flow graph:

Note, I use a simpler, less expensive, construction for the conditional iteration as having independent control-flow for the trivial condition is overkill.

The graph was realized using four-phase bundled data. Alas, I'm still working on the timing analysis, so the inserted delays are (hopefully) way oversized.

Figure 10: token-flow graph

#### How to test

The data is presented using the standard 4-phase (RTZ) protocol (idle, Req, Req+Ack, Ack, idle, …). To get a continuous stream, simply tie ack to req. The values expected are 0, 2, 6, …, x(x+1)

### **External hardware**

A logic analyzer is convenient to pick up the values on the outputs, but default RP2040 works fine.

| # | Input | Output   | Bidirectional |

|---|-------|----------|---------------|

| 0 | ack   | req      | result_7      |

| 1 |       | result_0 | result_8      |

| 2 |       | result_1 | result_9      |

| 3 |       | result_2 | result_10     |

| 4 |       | result_3 | result_11     |

| 5 |       | result_4 | result_12     |

| 6 |       | result_5 | result_13     |

| 7 |       | result_6 | result_14     |

# SRAM (1024x8) test [39]

- Author: Uri Shaked

- Description: Tests the foundry provided SRAM macro

- GitHub repository

- HDL project

- Mux address: 39

- Extra docs

- Clock: 0 Hz

### How it works

This is a 1 kbyte SRAM controller module. It allows reading or writing a single byte at a time.

There are 10 address lines, 8 data lines, and 1 write enable line.

To read a byte, set the write enable line (wen) to 0, and the data lines (dout[7:0]) will be set to the value of the byte at the address specified by the address lines (addr[5:0]).

To write a byte, set the write enable line (wen) to 1, and set the data lines (din[7:0]) to the desired value. Writing is only possible when the bank\_sel line is 0.

The lower 6 address bits (addr[5:0]) are exposed as input pins.

The upper 4 address lines are stored in the address\_bank register. To change the upper address bits, set the bank\_sel line to 1, and set the data lines (addr[9:6] / uio[3:0]) to the desired value.

### How to test

- 1. Set addr[5:0] to the desired address, set din[7:0] to the desired value, set wen to 1, and set bank\_sel to 0, then pulse the clock line. The value at the specified address should be updated to the value of din[7:0].

- 2. Set addr[5:0] to the desired address, set wen to 0, and set bank\_sel to 0, then pulse the clock line. The value at the specified address should be output on dout[7:0].

- 3. Set addr[9:6] to the desired value, set bank\_sel to 1, then pulse the clock line. The upper address bits should be updated to the value of addr[9:6].

### External hardware

### None

| # | Input    | Output  | Bidirectional  |

|---|----------|---------|----------------|

| 0 | addr[0]  | dout[0] | din[0]/addr[6] |

| 1 | addr1    | dout1   | din1/addr[7]   |

| 2 | addr2    | dout2   | din2/addr[8]   |

| 3 | addr[3]  | dout[3] | din[3]/addr[9] |

| 4 | addr[4]  | dout[4] | din[4]         |

| 5 | addr[5]  | dout[5] | din[5]         |

| 6 | bank_sel | dout[6] | din[6]         |

| 7 | wen      | dout[7] | din[7]         |

# Zilog Z80 [43]

- Author: ReJ aka Renaldas Zioma

- Description: Z80 open-source silicon. Goal is to become a silicon proven, pin compatible, open-source replacement for classic Z80.

- GitHub repository

- HDL project

- Mux address: 43

- Extra docs

- Clock: 16000000 Hz

### How it works

On April 15 of 2024 Zilog has announced End-of-Life for Z80, one of the most famous 8bit CPUs of all time. It is a time for open-source and hardware preservation community to step in with a Free and Open Source Silicon (FOSS) replacement for Zilog Z80.

The implementation is based around Guy Hutchison's TV80 Verilog core.

### The future work

- Add thorough instruction (including 'illegal') execution tests ZEXALL to testbench

- Compare different implementations: Verilog core A-Z80, Netlist based Z80Explorer

- Create gate-level layouts that would resemble the original Z80 layout. Zilog designed Z80 by manually placing each transistor by hand.

- Tapeout QFN44 package

- Tapeout DIP40 package

### Z80 technical capabilities

- nMOS original frequency 4MHz. CMOS frequency up to 20 MHz. This tapeout on 130 nm is expected to support frequency up to 50 MHz.

- 158 instructions including support for Intel 8080A instruction set as a subset.

- Two sets of 6 general-purpose reigsters which may be used as either 8-bit or 16-bit register pairs.

- One maskable and one non-maskable interrupt.

- Instruction set derived from Datapoint 2200, Intel 8008 and Intel 8080A.

### Z80 registers

- AF: 8-bit accumulator (A) and flag bits (F)

- BC: 16-bit data/address register or two 8-bit registers

- DE: 16-bit data/address register or two 8-bit registers

- HL: 16-bit accumulator/address register or two 8-bit registers

- SP: stack pointer, 16 bits

- PC: program counter, 16 bits

- IX: 16-bit index or base register for 8-bit immediate offsets

- IY: 16-bit index or base register for 8-bit immediate offsets

- I: interrupt vector base register, 8 bits

- R: DRAM refresh counter, 8 bits (msb does not count)

- AF': alternate (or shadow) accumulator and flags (toggled in and out with EX AF, AF')

- BC', DE' and HL': alternate (or shadow) registers (toggled in and out with EXX)

### Z80 Pinout

|     |       | ,  | ··      |    |        |   |

|-----|-------|----|---------|----|--------|---|

| <   | A11   | 1  |         | 40 | A10    | > |

| <   | A12   | 2  |         | 39 | A9     | > |

| <   | A13   | 3  | Z80 CPU | 38 | A8     | > |

| <   | A14   | 4  |         | 37 | A7     | > |

| <   | A15   | 5  |         | 36 | A6     | > |

| >   | CLK   | 6  |         | 35 | A5     | > |

| <-> | D4    | 7  |         | 34 | A4     | > |

| <-> | D3    | 8  |         | 33 | AЗ     | > |

| <-> | D5    | 9  |         | 32 | A2     | > |

| <-> | D6    | 10 |         | 31 | A1     | > |

|     | VCC   | 11 |         | 30 | AO     | > |

| <-> | D2    | 12 |         | 29 | GND    |   |

| <-> | D7    | 13 |         | 28 | /RFSH  | > |

| <-> | DO    | 14 |         | 27 | /M1    | > |

| <-> | D1    | 15 |         | 26 | /RESET | < |

| >   | /INT  | 16 |         | 25 | /BUSRQ | < |

| >   | /NMI  | 17 |         | 24 | /WAIT  | < |

| <   | /HALT | 18 |         | 23 | /BUSAK | > |

| <   | /MREQ | 19 |         | 22 | /WR    | > |

| <   | /IORQ | 20 |         | 21 | /RD    | > |

|     |       | `  |         | '  |        |   |

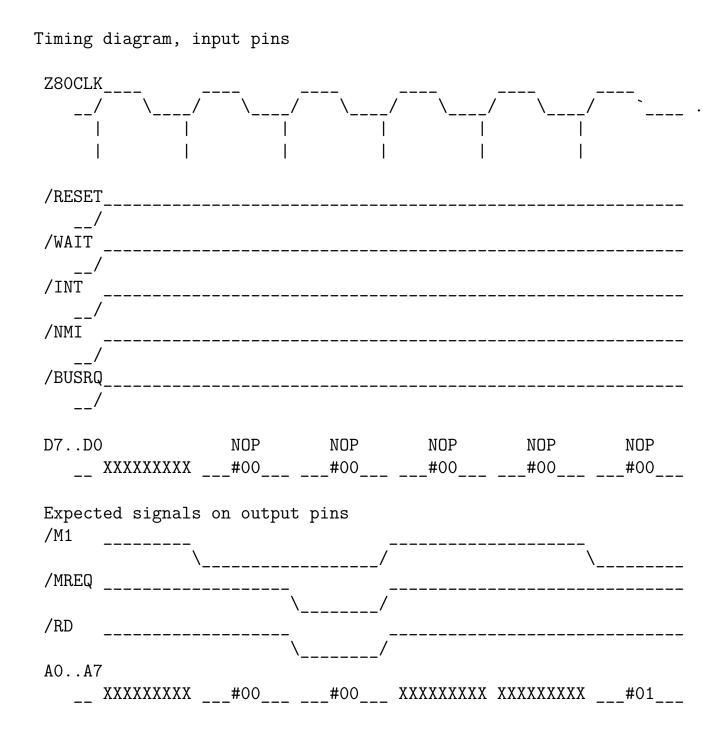

### How to test

Hold all bidirectional pins (**Data bus**) low to make CPU execute **NOP** instruction. **NOP** instruction opcode is 0. Hold all input pins high to disable interrupts and signal that data bus is ready. Every 4th cycle 8-bit value on output pins (Address bus low 8-bit) should monotonously increase.

### External hardware

Bus de-multiplexor, external memory, 8-bit computer such as ZX Spectrum.

Alternatively the RP2040 on the TinyTapeout test PCB can be used to simulate RAM and  $I/O. \label{eq:rescaled}$

| # | Input  | Output          | Bidirectional |

|---|--------|-----------------|---------------|

| 0 | /WAIT  | /M1, A0, A8     | D0            |

| 1 | /INT   | /MREQ, A1, A9   | D1            |

| 2 | /NMI   | /IORQ, A2, A10  | D2            |

| 3 | /BUSRQ | /RD, A3, A11    | D3            |

| 4 |        | /WR, A4, A12    | D4            |

| 5 |        | /RFSH, A5, A13  | D5            |

| 6 |        | /HALT, A6, A14  | D6            |

| 7 |        | /BUSAK, A7, A15 | D7            |

## Minilogix [70]

- Author: Harald Pretl

- Description: A configurable 8b in, 8b out logic block with optional feedback

- GitHub repository

- HDL project

- Mux address: 70

- Extra docs

- Clock: 20000000 Hz

### How it works

A programmable 8b input, 8b output freely programmable logic block with optional internal feedback. This can serve many purposes, once an FPGA-style configuration SW is available.

### How to test

- Load the logic block in serial mode.

- Test the logic functionality by applying different digital inputs.

### External hardware

Just a way to set digital inputs is needed, plus a way to check the digital outputs.

| # | Input    | Output    | Bidirectional |

|---|----------|-----------|---------------|

| 0 | data in0 | data out0 | load enable   |

| 1 | data in1 | data out1 | load clk      |

| 2 | data in2 | data out2 | load data     |

| 3 | data in3 | data out3 |               |

| 4 | data in4 | data out4 |               |

| 5 | data in5 | data out5 | dbg out0      |

| 6 | data in6 | data out6 | dbg out1      |

| 7 | data in7 | data out7 | dbg out2      |

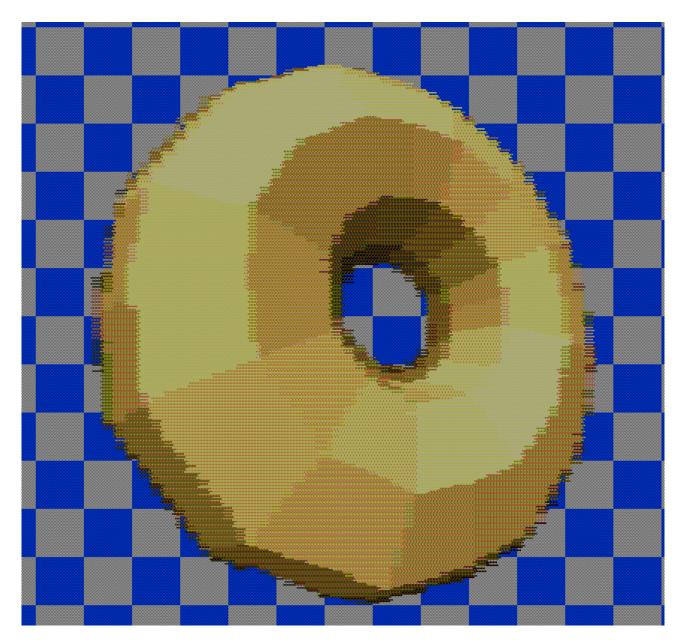

## VGA donut [74]

- Author: Andy Sloane

- Description: Renders a 3D torus on a VGA display

- GitHub repository

- HDL project

- Mux address: 74

- Extra docs

- Clock: 48000000 Hz

### VGA Donut

Figure 11: preview

How it works Renders a faceted donut to a VGA monitor.

Like my other demo on tt08, this runs in a weird VGA resolution: 1220x480, but still 4:3 aspect ratio like 640x480.

Interestingly, it is not actually rendering any polygons; this is sphere traced (AKA raymarched), using a CORDIC unit to calculate the distance between a point and the surface of the torus. But, because we don't have much time (we're racing the VGA beam!), we do just two or three CORDIC iterations, which causes the donut surface to actually become polyhedral. This trick was accidentally discovered by Bruno Levy while playing with a C version of my original donut code and I had to try it out in Verilog – so here we are.

The reason it has such low horizontal resolution is because it's doing 16 ray marching steps per "pixel", with five CORDIC iterations unrolled into one clock cycle (three iterations for the major axis, and two for the minor axis).

In order to fit this into 2x2 TinyTapeout tiles, a lot of sacrifices were made; for one, it doesn't have a multiplier so the ray steps are by approximate orders of magnitude. New donut "pixels" are rendered every 16 clock cycles, so the demo makes heavy use of dithering in both space and time – the video looks much better than the screenshot above.

**How to test** Connect VGA Pmod to output, set clock to 48MHz, and give it a reset pulse.

**External hardware** TinyVGA Pmod for video on o[7:0].

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 0 |       | R1     |               |

| 1 |       | G1     |               |

| 2 |       | B1     |               |

| 3 |       | VSync  |               |

| 4 |       | R0     |               |

| 5 |       | G0     |               |

| 6 |       | B0     |               |

| 7 |       | HSync  |               |

## VC 16-bit CPU [75]

- Author: Paul Campbell

- Description: VC 16-bit CPU RISV-C cpu

- GitHub repository

- HDL project

- Mux address: 75

- Extra docs

- Clock: 0 Hz

### How it works

CPU plus MMU

### How to test

needs external RAM system

### **External hardware**

external RAM

| # | Input     | Output       | Bidirectional  |

|---|-----------|--------------|----------------|

| 0 | ReadData0 | AddressData0 | AddressLSB     |

| 1 | ReadData1 | AddressData1 | WriteStrobe    |

| 2 | ReadData2 | AddressData2 | AddressLatchHi |

| 3 | ReadData3 | AddressData3 | AddressLatchLo |

| 4 | ReadData4 | AddressData4 | unused4        |

| 5 | ReadData5 | AddressData5 | unused5        |

| 6 | ReadData6 | AddressData6 | unused6        |

| 7 | ReadData7 | AddressData7 | InterruptIn    |

## VGA Pong with NES Controllers [97]

- Author: Brandon S. Ramos

- Description: Pong using 2 NES Controllers with a VGA display

- GitHub repository

- HDL project

- Mux address: 97

- Extra docs

- Clock: 25175000 Hz

### How it works

This project is designed to play Pong with two players using NES controllers which output to a VGA compatible monitor.

### How to test

You will need two NES controllers which will take in 3 wires (not including power and ground). Hook up the connections as shown in the bidirectional I/O.

Bidirectional:

- 1. NES\_Controller\_Left[0] data

- 2. NES\_Controller\_Left1 clock

- 3. NES\_Controller\_Left2 latch

- 4. NES\_Controller\_Right[0] data

- 5. NES\_Controller\_Right1 clock

- 6. NES\_Controller\_Right2 latch

- 7. NC

- 8. NC You will also need the hook up the output to a VGA breakout board. I created my own using a perfboard and some resistors but you can use the TinyTapeout VGA PMOD, just ensure that you hook up r0,r1 on the VGA PMOD both to r from the output as my design only uses 1 bit for each signal.

### Output:

- 1. h\_sync

- 2. v\_sync

- 3. r

- 4. g

- 5. b

- 6.

- 7.

- 8.

### External hardware

- VGA PMOD or your own VGA breakout board

- 2 NES controllers

- VGA compatible monitor

| # | Input | Output | Bidirectional           |

|---|-------|--------|-------------------------|

| 0 |       | h_sync | NES_Controller_Left[0]  |

| 1 |       | v_sync | NES_Controller_Left1    |

| 2 |       | r      | NES_Controller_Left2    |

| 3 |       | g      | NES_Controller_Right[0] |

| 4 |       | b      | NES_Controller_Right1   |

| 5 |       |        | NES_Controller_Right2   |

| 6 |       |        |                         |

| 7 |       |        |                         |

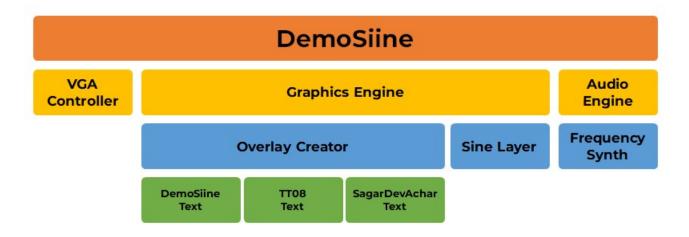

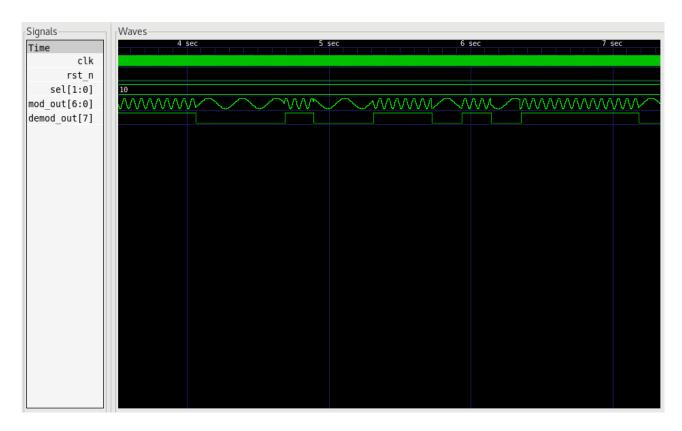

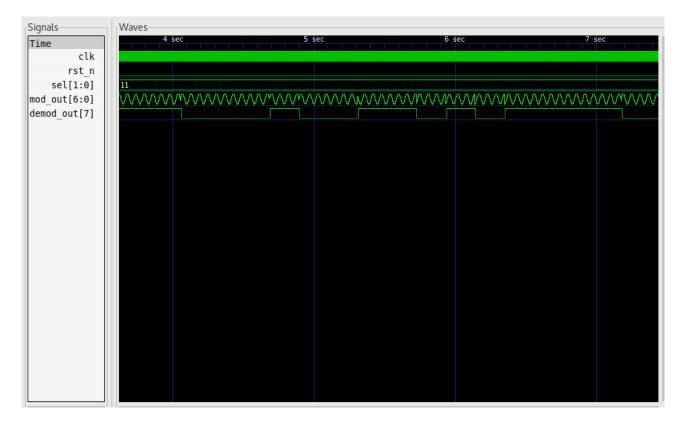

## DemoSiine [99]

- Author: SagarDevAchar

- Description: A Wavy and Rainbowy TT08 Demoscene Submission

- GitHub repository

- HDL project

- Mux address: 99

- Extra docs

- Clock: 25000000 Hz

### How it works

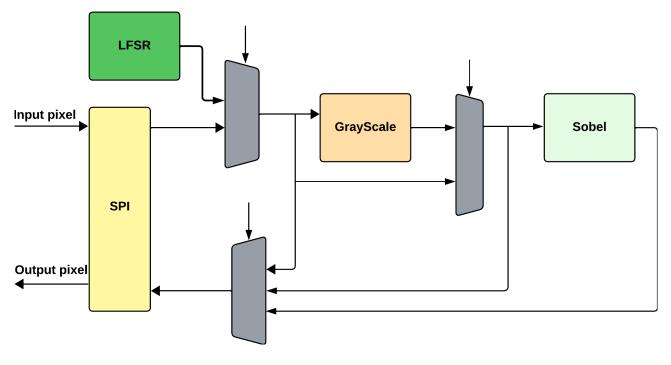

The project structure is as shown below:

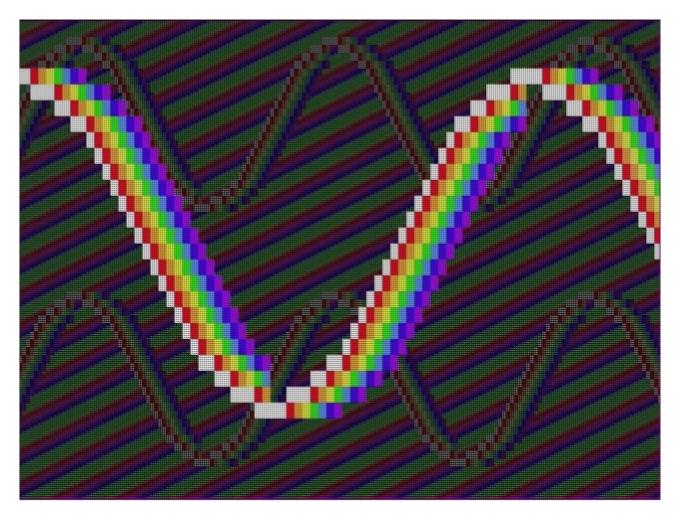

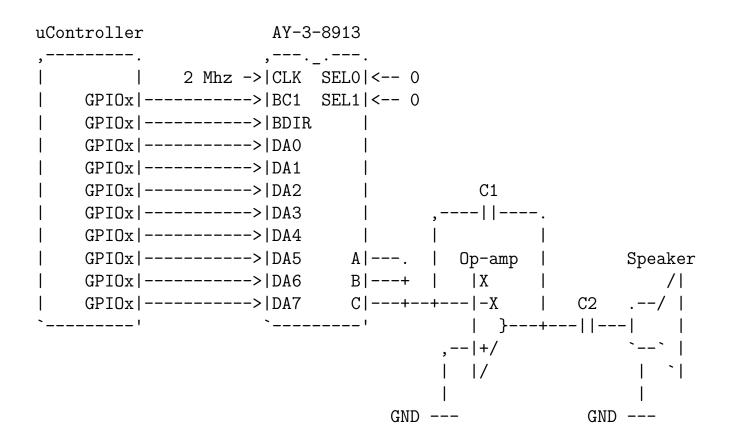

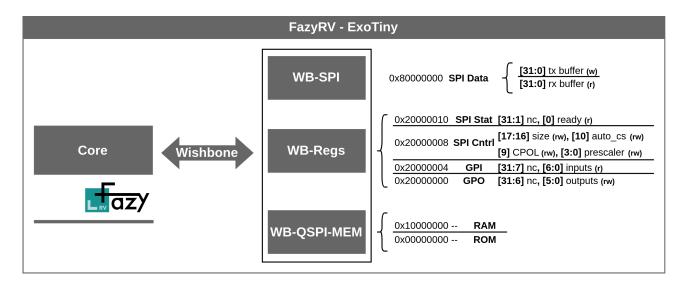

Figure 12: DemoSiine Project Structure

The **Graphics Engine** (driven by the **VGA Controller**, 640x480 @ 60Hz) is an ondemand RGB display pixel generator whose output can be altered using a few input pins. Previews of the different possible display outputs are provided in the last section of this documentation.

The **Audio Engine** drives the **Frequency Synth** to produce a  $\sim$ 28 second looping sound track @ 140 BPM at the output.

### External hardware

- Leo's TinyVGA Pmod connected to OUTPUT terminal (uo\_out)

- Mike's TT Audio Pmod connected to BIDIR terminal (uio\_out)

- Some switches to the INPUT terminal (ui\_in)

### How to test

- Connect the necessary peripherals

- Provide a 25MHz clock to the top module tt\_um\_demosiine\_sda

- Reset the design (if necessary)

- Enjoy the show :)

- Tweak the inputs to customize your show!

### **Input Configurations**

The design takes in 8 digital inputs from the INPUT terminal to modify the on-screen graphics (and audio) to create funky visual effects. All inputs are expected to be LOW to render the output as shown in the default preview as shown below.

| Input Pin | Parameter         | When LOW  | When HIGH   |

|-----------|-------------------|-----------|-------------|

| ui_in[7]  | Audio State       | Play      | Pause       |

| ui_in[6]  | Animation State   | Run       | Stop        |

| ui_in[5]  | Background Style  | Black     | Rolling RGB |

| ui_in[4]  | Overlay Style     | Cycle RGB | Rolling RGB |

| ui_in[3]  | Overlay State     | Enabled   | Disabled    |

| ui_in[2]  | Big Sine State    | Enabled   | Disabled    |

| ui_in[1]  | Little Sine State | Enabled   | Disabled    |

| ui_in[0]  | Colour Inversion  | Normal    | Negative    |

The effect of each input pin is presented in the table below:

### Previews

Provided below are a some of my favourite previews generated from DemoSiine along with the INPUT configuration which generated them:

| # | Input                              | Output          | Bidirectional |

|---|------------------------------------|-----------------|---------------|

| 0 | Frame Positive / Negative          | Video Red MSB   |               |

| 1 | Enable / Disable Little Sine Layer | Video Green MSB |               |

| 2 | Enable / Disable Big Sine Layer    | Video Blue MSB  |               |

| 3 | Enable / Disable Overlay           | Video V-Sync    |               |

| 4 | Toggle Overlay Style               | Video Red LSB   |               |

| # | Input                   | Output          | Bidirectional |

|---|-------------------------|-----------------|---------------|

| 5 | Toggle Background Style | Video Green LSB |               |

| 6 | Run / Stop Animation    | Video Blue LSB  |               |

| 7 | Play / Pause Audio      | Video H-Sync    | Audio Output  |

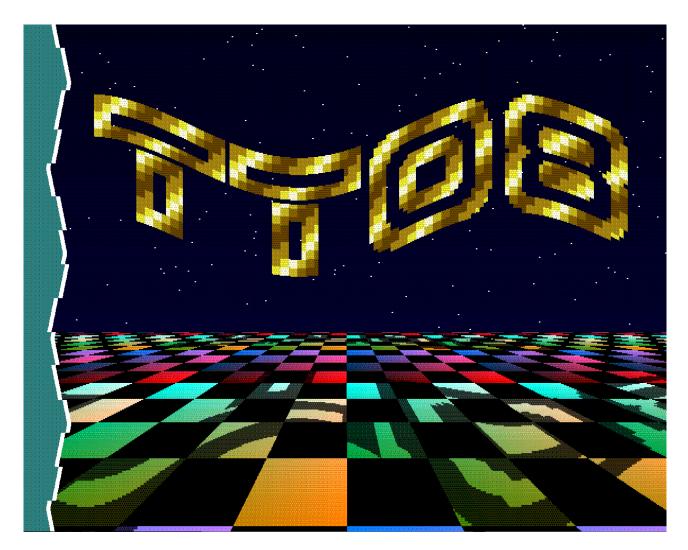

# INPUT = xx000000 (Default)

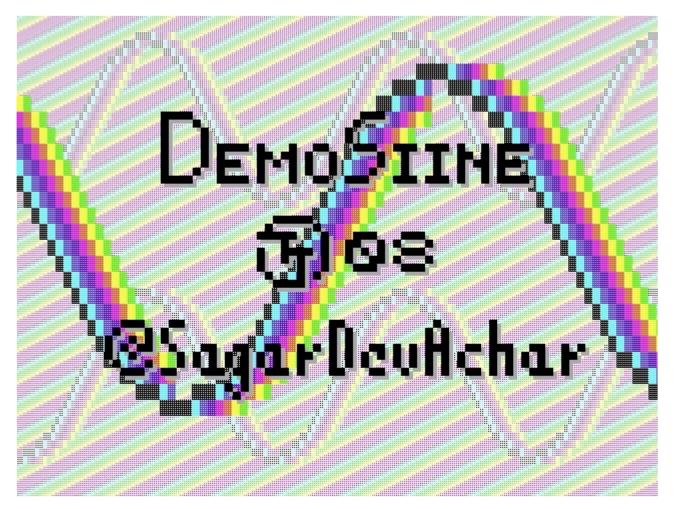

Figure 13: DemoSiine Default Video Output Preview

# INPUT = xx1x1000

Figure 14: DemoSiine Video Output Preview 2

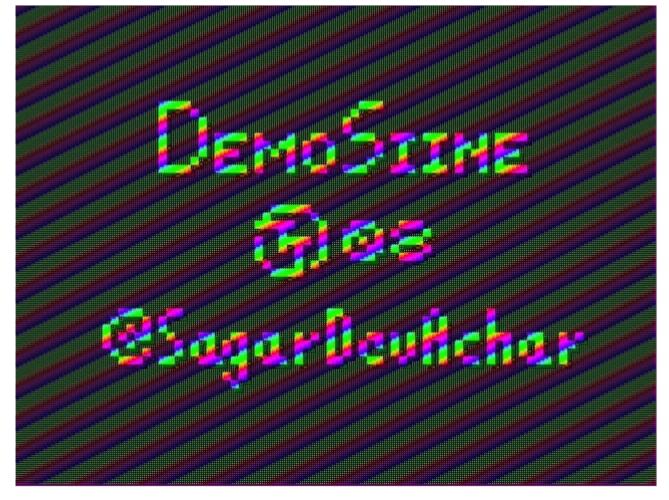

# INPUT = xx100001

Figure 15: DemoSiine Video Output Preview 3

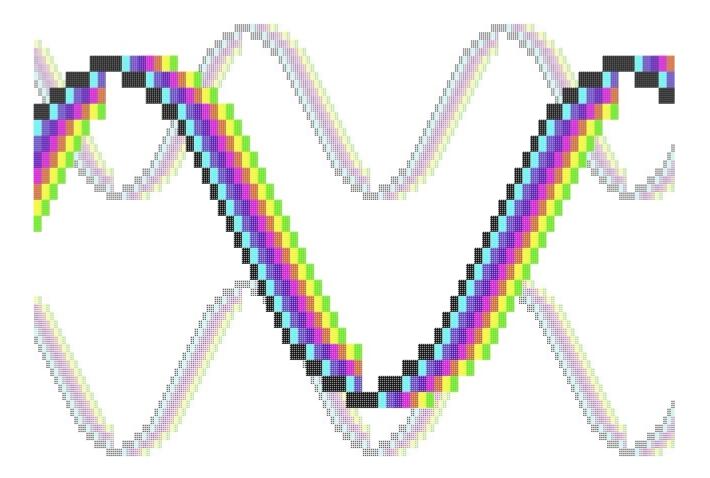

# INPUT = xx110110

Figure 16: DemoSiine Video Output Preview 4

# INPUT = xx0x1001

Figure 17: DemoSiine Video Output Preview 5

## INPUT = xx010110

Figure 18: DemoSiine Video Output Preview 6

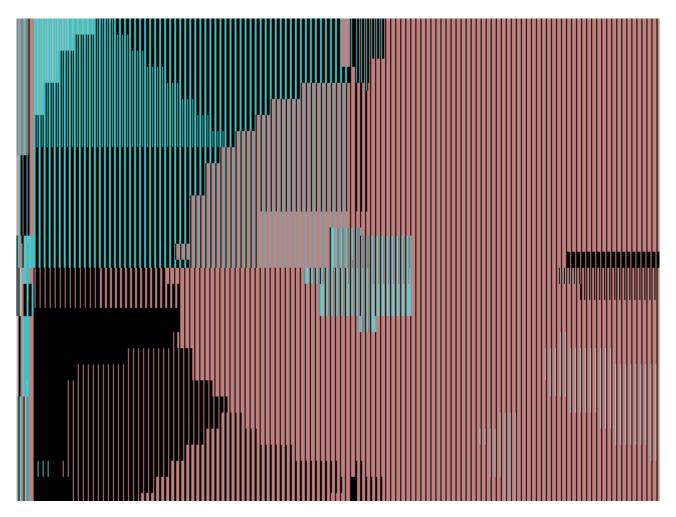

### Rounding error [101]

- Author: Edwin Török

- Description: Competition entry

- GitHub repository

- HDL project

- Mux address: 101

- Extra docs

- Clock: 25250000 Hz

### How it works

**Idea** This started out as an attempt to implement a ray tracer in 2 TT tiles. However, there isn't enough room for a proper one, precision has to be limited, which leads to unavoidable rounding errors.

So embrace rounding errors, and make them the primary feature!

The end result doesn't resemble a 3D scene, or a sphere, or in fact not even a properly rounded circle, but it has rounding errors! And that is the goal of this project now!

**HardCaml** The RTL was written using HardCaml, an OCaml DSL that emits Verilog. For convenience the generated Verilog is committed into the source tree, so no additional tools are needed.

I used registers with asynchronous reset, in theory it should be better for an area constrained design.

### VGA signal generation

**ModeLine** VGA signal timing is described in "3. DMT Video Timing Parameter Definitions" in "VESA Display Monitor Timing Standard Version 1.0, Rev. 13", and is implemented in src/generator/modeline.ml. Examples on how to implement them on an FPGA are available in several places.

The code supports several resolutions, however to conserve area for the demo l've chosen only 640x480@59.94Hz, which has negative hsync/vsync polarities. This resolution would need a 25.175 MHz pixel clock, however that can't be produced exactly by the TT08 board, it can only approximate it using a PWM. Therefore, the design is configured to run at the nearest frequency that can be exactly generated:

25.25 MHz, which should be within the 0.5% acceptable by the standard. The ModeLine implemented is: ModeLine "640x480\_59.94" 25.175 640 656 752 800 480 490 492 525 -hsync -vsync. (This has 59.94 refresh rate and not 60Hz due to the standard preferring NTSC and its 1.001 adjustment).

The design itself runs off the VGA pixel clock, as I didn't want to deal with potential clock domain crossing issues.

**Counters** There are 2 counters: one for H, and one for V synchronization pulses. When the H counter overflows it enables and increments the V counter for 1 cycle. This is implemented in generator/vga.ml, together with waveform expectation tests.

Both H and V counters start out in the visible area for convenience (we can directly use these counters as x/y coordinates, without needing to perform arithmetic in the circuit), then blank the colour signals for the duration of the front porch, synchronization signal and back porch. Although the monitor would recognize the hsync+vsync low as the start of a frame, this is equivalent, but offset by a few clocks.

**R**, **G**, **B** colours The demo supports 2-bit colours, and as usual these would be sRGB colours, not a linear scale. So we define an internal table indexed by 3 bits representing a linear RGB value, mapping to the sRGB bits.

A register is used for the output, both to avoid logic glitches becoming visible to the monitor, and to provide a reg to reg path that OpenSTA can use to compute setup/hold times.

**Generating the colours** When test mode is used (pin ui[0] set to 1) the design outputs vertical colour bars with a white-black-white border. This doesn't have rounding errors, everything is sharp.

In normal mode (pin ui [0] is 0) the "rounding error graphics" is rendered, see below.

**Ray marching** For an explanation of how ray marching works, see this ray marching tutorial. The "scene" is represented using signed distance functions. The "eye" Z coordinate is animated between 3.5 and 4.5 in 256 steps, where each frame is one step.

**CORDIC** Fixed point arithmetic with 9 bits of precision is used in the HDL, with the exponent tracked by the generator code to reduce register width (though this is not as good as tracking it in hardware, but that'd require more area). Vector normalization is implemented using the CORDIC implementation provided by HardCaml, configured to use 10 bits, and a limited number of iterations (4) to fit into the desired area. This works by rotating the vector until its angle is 0, and then rotating a second unit vector to match the rotation of the original. Or equivalently transform the original from rectangular to polar coordinates, overwrite the length with 1, and convert back from polar to rectangular. CORDIC is defined for 2D in the library, and I define a 3D wrapper based on rectangular to spheric coordinate conversions, although there would be ways to directly compute a 3D version of CORDIC, that is not implemented here.

This is implemented in src/vecmath.

**GLSL ES "emulation"** The low level operations are wrapped by a higher level embedded DSL that allows writing code quite similar to GLSL ES, with a very small number of operators: arithmetic (+, -, \*, /), comparison (==, <>), abs, min, max, clamp, length, distance, dot, normalize, reflect.

Unfortunately the full renderer didn't fit into 2 tiles, so had to comment out quite a lot of the "GLSL" code (only 1 step of ray marching, no clamping, very simple gradient approximation), what is remaining does not resemble a sphere, or in fact it doesn't even look 3D.

**OpenLane configuration** The target density had to be increased to 98% to fit, and the setup slack margin setting had to be increased, see config.json. There are max slew and max fanout violations at 100C and 1.6V, but that shouldn't prevent the design from working at 25C and 1.8V.

The design was simulated using both tt-vgaviz and vgasim, although had to adjust the modeline for vgasim to recognize the standard one. A simple cocotb test which checked vsync/hsync generation was added post submission.

**Simulating** There is a src/sim/vgasim.ml, which generates a demo.v compatible with vgasim, this uses a different resolution though. vgasim has to be called with -g 640x480, and videomode.h needs to be edited to use 480 490 492 525 (don't know why it wants 521, that doesn't seem to be the standard timing).

Alternatively the cocotb test in test/ can be run with make -B WAVES=1, and then tt-vgaviz can be used: tt-vgaviz tb.vcd (actually in FST format).

### How to test

### Configuration

- Provide a 25.25 MHz clock on the clk pin (RP2040 should be able to provide this with no jitter). Or if you can try 25.175 MHz instead, but this will have some jitter. YMMV.

- Power the design with at least 1.8V

### Main demo

- Set pin ui [0] to 0 to run the default demo.

- Reset the design

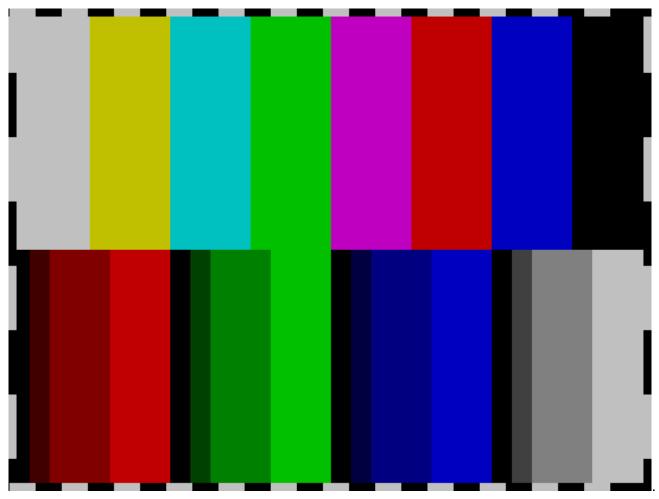

- You should see circles moving slowly and large rounding errors:

Figure 19: circles

### Test mode

- Set pin ui [0] to 1 to show a test image with color bars.

- Reset the design again if desired

- You should see:

### External hardware

Connect according to the Demoscene rules

VGA output using Leo's VGA PMOD on pins uo [0-7], connected to a monitor supporting 640x480 resolution.

| # | Input                   | Output | Bidirectional |

|---|-------------------------|--------|---------------|

| 0 | test mode (0=no, 1=yes) | r1     |               |

| 1 |                         | g1     |               |

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 2 |       | b1     |               |

| 3 |       | vsync  |               |

| 4 |       | r0     |               |

| 5 |       | g0     |               |

| 6 |       | b0     |               |

| 7 |       | hsync  | PWM output    |

## VGA Pride [103]

- Author: Rebecca G. Bettencourt

- Description: A VGA demo for showing pride flags

- GitHub repository

- HDL project

- Mux address: 103

- Extra docs

- Clock: 0 Hz

### How it works

Displays pride flags on the screen.

To add another flag, create a flag.v file and add it to src/flag\_index.v, test/Makefile, and info.yaml, using the existing flags as examples.

### How to test

Connect to a VGA monitor. Set the following inputs to change the displayed flag:

- ui\_in[7] to display the first flag

- ui\_in[6] to display the next flag

- ui\_in[5] to display the previous flag

- ui\_in[4] to display the flag whose index is on uio\_in

| Index | Flag                               |  |

|-------|------------------------------------|--|

| 0     | Rainbow flag, 6 stripes            |  |

| 1     | Rainbow flag, 7 stripes            |  |

| 2     | Rainbow flag, 8 stripes            |  |

| 3     | Rainbow flag, 9 stripes            |  |

| 4     | Philadelphia rainbow flag          |  |

| 5     | Progress rainbow flag              |  |

| 6     | Progress rainbow flag 2021 version |  |

| 7     | Trans pride flag                   |  |

| 8     | Abrosexual pride flag              |  |

| 9     | Aceflux pride flag                 |  |

| 10    | Aegosexual pride flag              |  |

| 11    | Agender pride flag                 |  |

| 12    | Androgyne pride flag               |  |

| 13    | Androsexual pride flag             |  |

| Index | Flag                                                               |

|-------|--------------------------------------------------------------------|

| 14    | Aporagender pride flag                                             |

| 15    | Aroace pride flag                                                  |

| 16    | Aroflux pride flag                                                 |

| 17    | Aromantic pride flag                                               |

| 18    | Asexual pride flag                                                 |

| 19    | Aspec pride flag                                                   |

| 20    | Bigender pride flag (pink purple white purple blue)                |

| 21    | Bigender pride flag (blue white purple white pink)                 |

| 22    | Bigender pride flag (pink yellow white purple blue)                |

| 23    | Bisexual pride flag                                                |

| 24    | Ceterosexual pride flag                                            |

| 25    | Demiandrogyne pride flag (pink purple blue)                        |

| 26    | Demiandrogyne pride flag (green white green)                       |

| 27    | Demiboy pride flag                                                 |

| 28    | Demifluid pride flag                                               |

| 29    | Demiflux pride flag                                                |

| 30    | Demigender pride flag                                              |

| 31    | Demigirl pride flag                                                |

| 32    | Demiromantic pride flag                                            |

| 33    | Demisexual pride flag                                              |

| 34    | Disability rights flag (gold silver bronze tricolor)               |

| 35    | Disability rainbow flag                                            |

| 36    | Gender-neutral pride flag                                          |

| 37    | Genderfluid pride flag                                             |

| 38    | Genderflux pride flag                                              |

| 39    | Genderqueer pride flag                                             |

| 40    | Greygender pride flag                                              |

| 41    | Greysexual pride flag                                              |

| 42    | Gynosexual pride flag                                              |

| 43    | Intersex pride flag (purple circle)                                |

| 44    | Intersex pride flag (blue/pink gradient)                           |

| 45    | Thislesbianlife lesbian pride flag (pink and red)                  |

| 46    | Sadlesbeandisaster lesbian pride flag, 7 stripes (orange and pink) |

| 47    | Sadlesbeandisaster lesbian pride flag, 5 stripes (orange and pink) |

| 48    | Lydiandragon lesbian pride flag (violet crocus dill rose)          |

| 49    | Maya Kern lesbian pride flag (violet rose crocus dill)             |

| 50    | RebeccaRGB femme lesbian pride flag (violet lavender pink rose)    |

| 51    | Littleender pride flag                                             |

| 52    | Maverique pride flag                                               |

| 53    | Leonis Ignis MLM pride flag (brown and blue)                       |

| Index | Flag                                                                |

|-------|---------------------------------------------------------------------|

| 54    | Vincian MLM pride flag, 7 stripes (green and blue)                  |

| 55    | Vincian MLM pride flag, 5 stripes (green and blue)                  |

| 56    | Vincian MLM pride flag (light blue and light green)                 |

| 57    | Multigender pride flag                                              |

| 58    | Multisexual pride flag                                              |

| 59    | Neptunic pride flag                                                 |

| 60    | Neutrois pride flag                                                 |

| 61    | Nonbinary pride flag                                                |

| 62    | Objectum pride flag                                                 |

| 63    | Omnisexual pride flag                                               |

| 64    | Pangender pride flag                                                |

| 65    | Pansexual pride flag                                                |

| 66    | Polyamory pride flag (blue, red, black with yellow pi)              |

| 67    | Polyamory pride flag (blue, magenta, purple with yellow heart)      |

| 68    | Polygender pride flag                                               |

| 69    | Polysexual pride flag                                               |

| 70    | Pomosexual pride flag                                               |

| 71    | Proculsexual pride flag                                             |

| 72    | IBM PS/2 pride flag                                                 |

| 73    | Queer pride flag                                                    |

| 74    | Trains pride flag ( <i>Train Landscape</i> , Ellsworth Kelly, 1953) |

| 75    | Transfeminine pride flag                                            |

| 76    | Transmasculine pride flag                                           |

| 77    | Transneutral pride flag                                             |

| 78    | Trigender pride flag                                                |

| 79    | Unlabeled pride flag                                                |

| 80    | Uranic pride flag                                                   |

| 81    | Voidpunk pride flag                                                 |

### External hardware

TinyVGA PMOD

| # | Input        | Output | Bidirectional |

|---|--------------|--------|---------------|

| 0 | address mode | R1     | A0            |

| 1 |              | G1     | A1            |

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 2 |       | B1     | A2            |

| 3 |       | VSync  | A3            |

| 4 | set   | R0     | A4            |

| 5 | prev  | G0     | A5            |

| 6 | next  | B0     | A6            |

| 7 | reset | HSync  | A7            |

## VGA Nyan Cat [105]

- Author: Andy Sloane

- Description: Displays the classic nyan.cat animation

- GitHub repository

- HDL project

- Mux address: 105

- Extra docs

- Clock: 25175000 Hz

### VGA nyan cat

Figure 20: nyancat preview

How it works Outputs nyancat on VGA with music!

Colors and animation are all from the original nyan.cat site, using a 2x2 Bayer dithering matrix which inverts on alternate frames for better color rendition on the Tiny VGA Pmod.

Sound is generated from a MIDI file, split into melody and bass parts. Melody and bass are each square waves mixed with a simple exponential decay envelope, which is then fed to a low-pass filter and then a sigma-delta DAC.

This was designed to fit into 1 tile, and it *almost* did – the cells take up about 93% of 1 tile, but detailed routing doesn't finish. With the deadline approaching I was forced to grow it to 1x2, so I threw in a little easter egg.

**How to test** Set clock to 25.175MHz or thereabouts, give reset pulse, and enjoy

### **External hardware** TinyVGA Pmod for video on o[7:0].

1-bit sound on io[7], compatible with Tiny Tapeout Audio Pmod, or any basic  $\sim$ 20kHz RC filter on io7 to an amplifier will work.

| # | Input | Output | Bidirectional |

|---|-------|--------|---------------|

| 0 |       | R1     |               |

| 1 |       | G1     |               |

| 2 |       | B1     |               |

| 3 |       | VSync  |               |

| 4 |       | R0     |               |

| 5 |       | G0     |               |

| 6 |       | B0     |               |

| 7 |       | HSync  | AudioPWM      |

## Flame demo [107]

- Author: Konrad Beckmann & Linus Mårtensson

- Description: Flame demo

- GitHub repository

- HDL project

- Mux address: 107

- Extra docs

- Clock: 25000000 Hz

### Flame - Konrad & Linus tinytapeout08 demo compo entry

Figure 21: preview

**How it works** It shows a flame and plays audio. The VGA output is standard 640x480@60Hz, audio is simple 1 bit PWM.

**How to test** Run clock at 25MHz, connect VGA and sound Pmods, and give it a reset pulse.

**External hardware** Follows the democompo hardware rules:

TinyVGA Pmod for video on o[7:0].

1-bit sound on io[7], compatible with Tiny Tapeout Audio Pmod, or any basic  ${\sim}20 kHz$  RC filter on io7 to an amplifier will work.

| # | Input    | Output    | Bidirectional |

|---|----------|-----------|---------------|

| 0 | ui_in[0] | ui_out[0] | uio_out[0]    |

| 1 | ui_in1   | ui_out1   | uio_out1      |

| 2 | ui_in2   | ui_out2   | uio_out2      |

| 3 | ui_in[3] | ui_out[3] | uio_out[3]    |

| 4 | ui_in[4] | ui_out[4] | uio_out[4]    |

| 5 | ui_in[5] | ui_out[5] | uio_out[5]    |

| 6 | ui_in[6] | ui_out[6] | uio_out[6]    |

| 7 | ui_in[7] | ui_out[7] | uio_out[7]    |

## **INTERCAL ALU [128]**

- Author: Rebecca G. Bettencourt

- Description: An ALU for the five operators of the INTERCAL programming language.

- GitHub repository

- HDL project

- Mux address: 128

- Extra docs

- Clock: 0 Hz

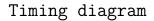

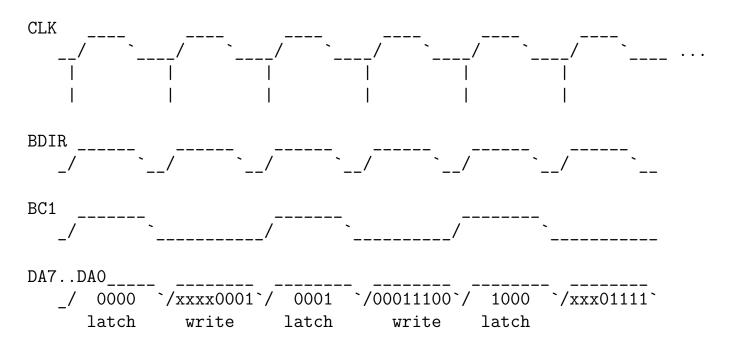

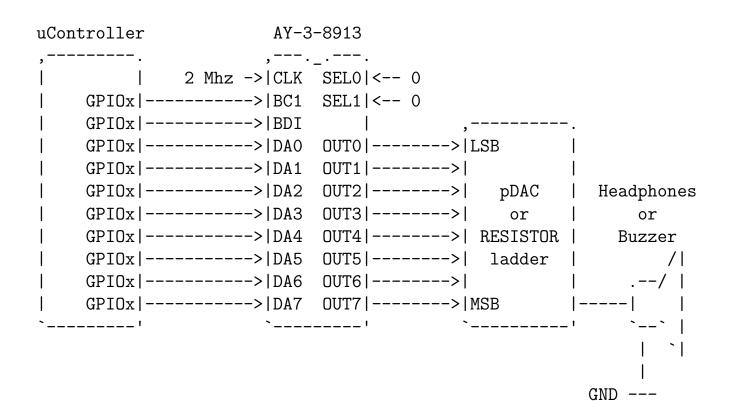

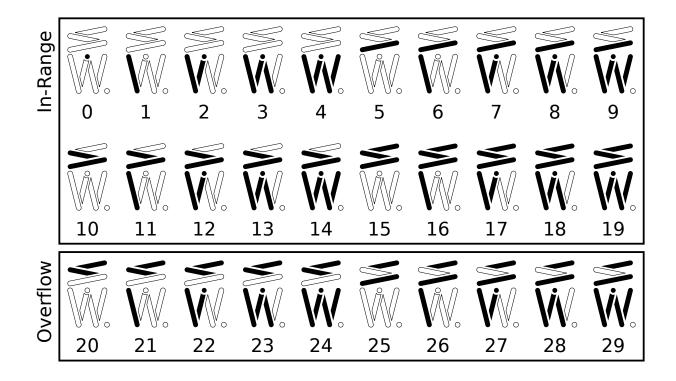

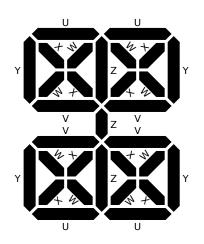

### How it works