# **Tiny Tapeout IHP 25a Datasheet**

Project Repository https://github.com/TinyTapeout/tinytapeout-ihp-25a

April 4, 2025

Contents

| Chip renders                                                              | 11 |

|---------------------------------------------------------------------------|----|

| Full chip render                                                          | 11 |

| Top Metal $1/2$                                                           | 12 |

| Logic density view                                                        | 13 |

| Projects                                                                  | 14 |

| Chip ROM [0]                                                              | 14 |

| Tiny Tapeout Factory Test 1                                               | 16 |

| Verilog ring oscillator V3 2                                              | 18 |

| Matmul System [3]                                                         | 19 |

| 4-Bit Toy CPU [4]                                                         | 20 |

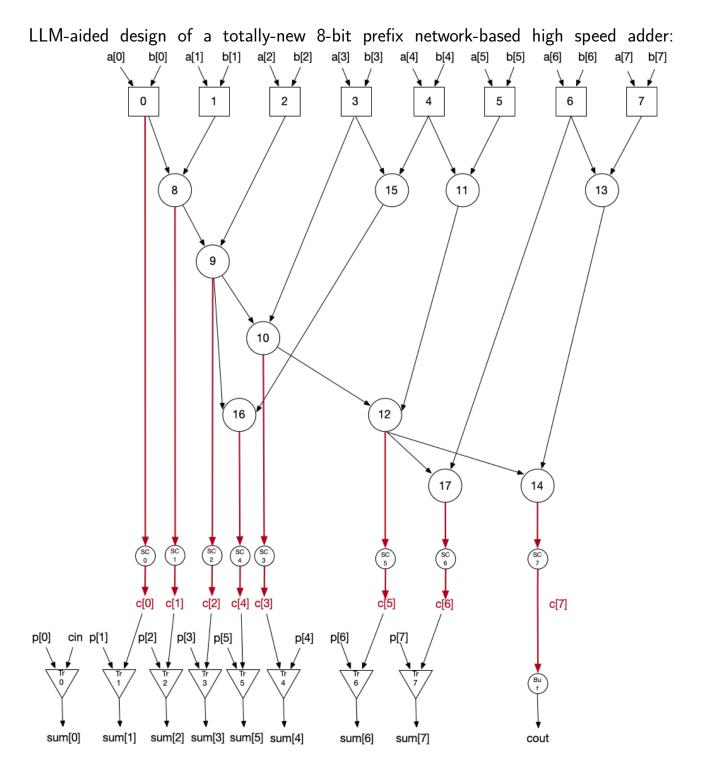

| Hybrid_Adder_8bit [5]                                                     | 22 |

| Dynamic Threshold Leaky Integrate-and-Fire [6]                            | 24 |

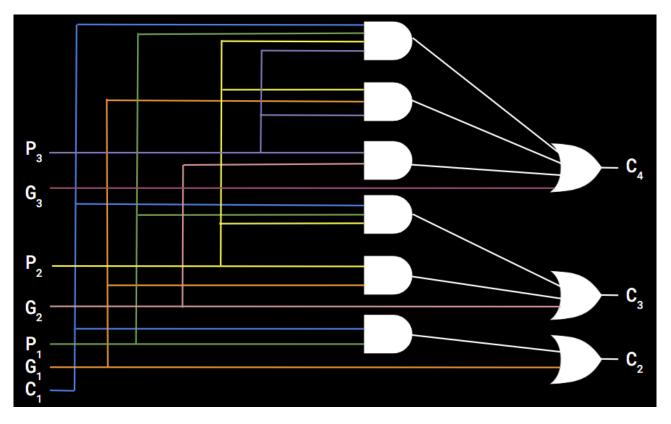

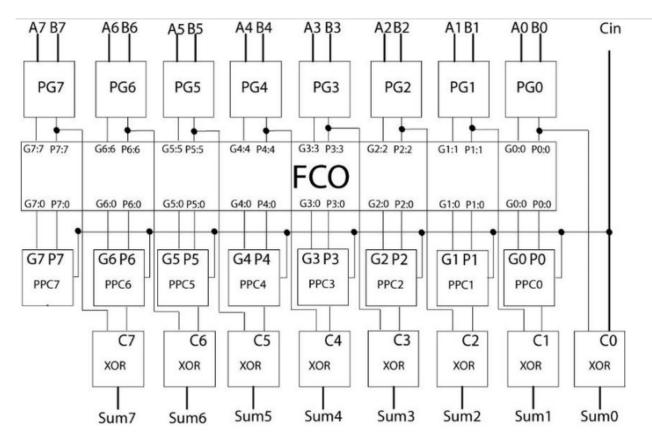

| 8-bit Carry Look-Ahead Adder [7]                                          | 25 |

| ternary, E1M0, E2M0 decoders [8]                                          | 28 |

| RISC-V Mini [9]                                                           | 29 |

| eksdee [10]                                                               | 32 |

| 8-bit carry-skip [11]                                                     | 33 |

| Cgates [12]                                                               | 35 |

| T3 (Tiny Ternary Tapeout) [13]                                            | 37 |

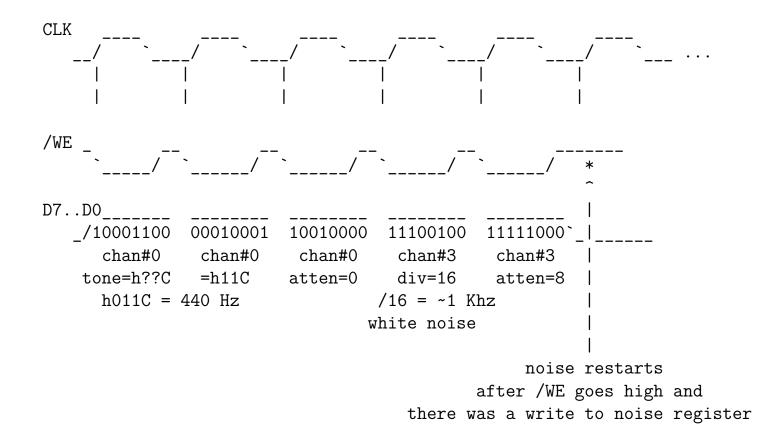

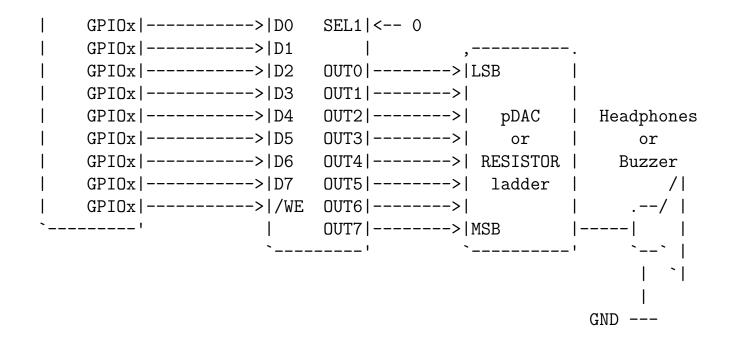

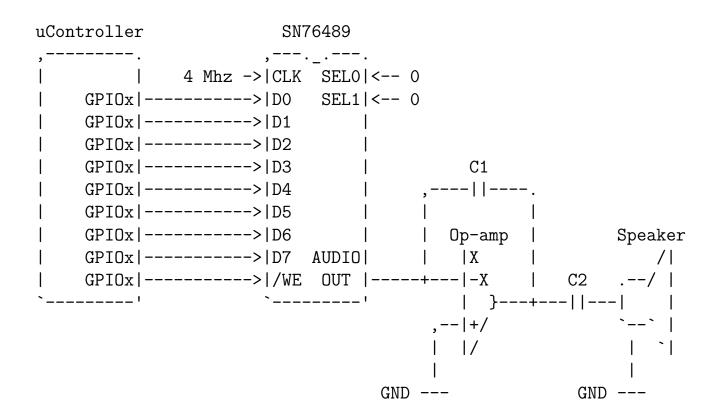

| Classic 8-bit era Programmable Sound Generator SN76489 [14]               | 41 |

| 3 Neuron ALIF [15]                                                        | 49 |

| Giant Ring Oscillator (3853 inverters) [16]                               | 51 |

| STDP Circuit [17]                                                         | 53 |

| TwoChannelSquareWaveGenerator [18]                                        | 55 |

| instrumented_ring_oscillator [19]                                         | 57 |

| Linear Timecode (LTC) generator [32]                                      | 59 |

| Tiny Shader [34]                                                          | 61 |

| Sine Synth [36]                                                           | 66 |

| DRUM [38]                                                                 | 68 |

| Tiny Hash Table [40]                                                      | 70 |

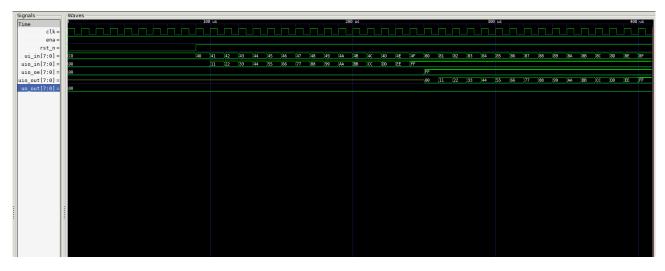

| Asynchronous FIFO [42]                                                    | 72 |

| Synchronous FIFO [44]                                                     | 74 |

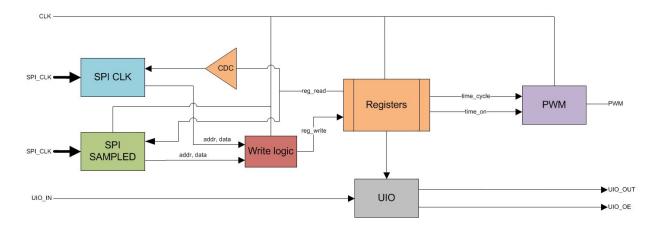

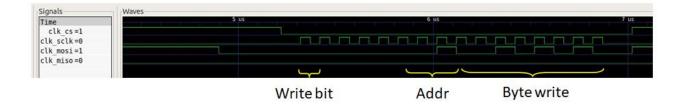

| Pulse Width Modulation [46]                                               | 75 |

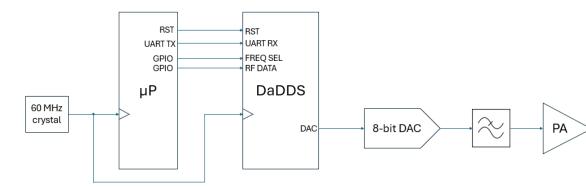

| DaDDS [48]                                                                | 78 |

| Simple shift Reg [50]                                                     | 80 |

| 2-bit 2x2 Matrix Multiplier [64]                                          | 81 |

| 8b10b decoder and multiplier [65]                                         | 83 |

| VGA Tiny Logo (1 tile) [66]                                               | 85 |

| Test Design 1 [67]                                                        | 86 |

| A simple leaky integrate and fire neuron [68]                             | 88 |

| Decimation Filter for Incremental and Regular Delta-Sigma Modulators [69] | 89 |

| Leaky Neuron Network [70]                                 | 92  |

|-----------------------------------------------------------|-----|

| adder-accumulator [71]                                    | 94  |

|                                                           | 99  |

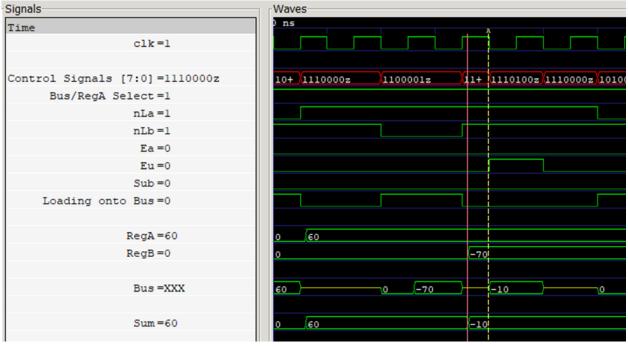

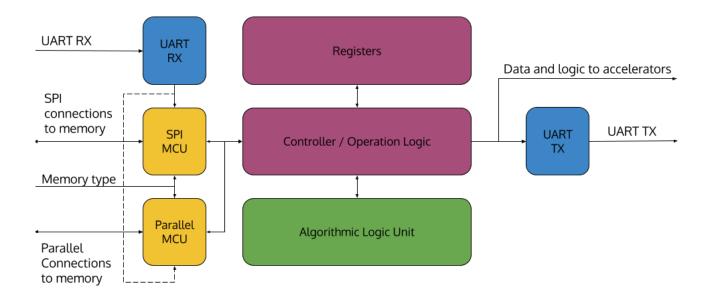

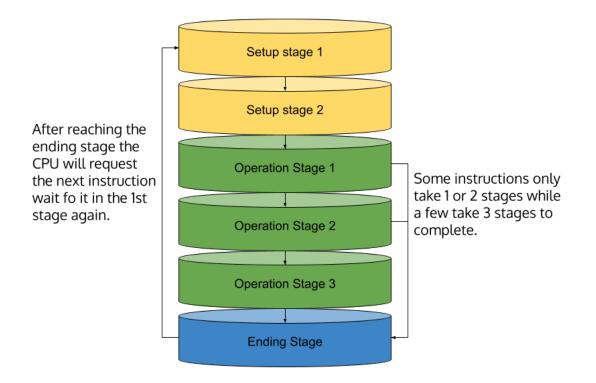

| ECE 298A 8-Bit CPU Control Block [73]                     | 101 |

| RISCV Processor Design [74]                               |     |

|                                                           | 107 |

|                                                           | 108 |

|                                                           | 110 |

|                                                           | 111 |

| Two LIF Neurons with STDP Learning [79]                   | 112 |

| Tutorial: Simple LIF Neuron [80]                          |     |

| 7-Segment Byte Display [81]                               |     |

| RGB Mixer demo [82]                                       |     |

| Forward Pass Network for Simple ANN [83]                  |     |

|                                                           | 121 |

| UltraTiny-CPU [98]                                        | 122 |

|                                                           | 124 |

|                                                           | 126 |

|                                                           | 127 |

|                                                           | 129 |

|                                                           | 130 |

|                                                           | 137 |

|                                                           | 140 |

|                                                           | 145 |

| pulse_add [128]                                           | 146 |

| nyan [130]                                                | 147 |

| Brailliance [132]                                         | 148 |

| Adder with Flow Control [134]                             | 149 |

| i2c peripherals: leading zero count and fnv-1a hash [136] | 152 |

| Rotary Encoder WS2812B Control [138]                      | 154 |

| Alarm Clock [140]                                         | 156 |

| TSAL_TT [142]                                             | 158 |

| Divided Ring Oscillator [144]                             | 160 |

| HACK CPU [146]                                            | 163 |

| simon_cipher [161]                                        | 167 |

| Wirecube [163]                                            | 169 |

| TT08 Pachelbel's Canon demo [165]                         | 170 |

| Neural Net ASIC [166]                                     |     |

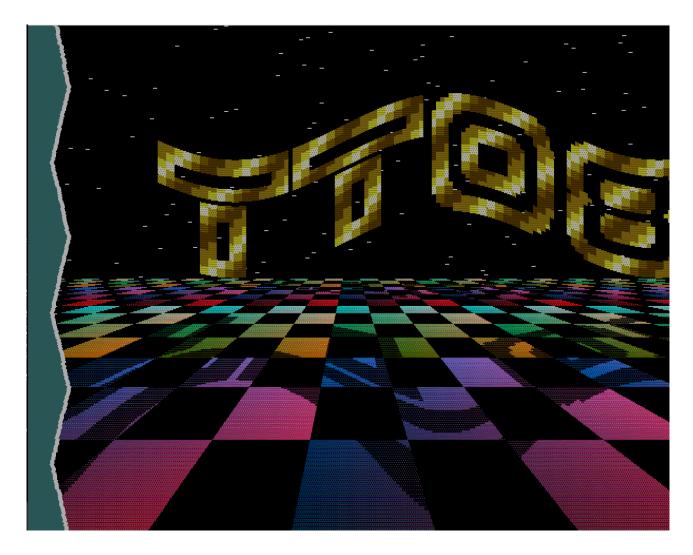

| Sequential Shadows [TT08 demo competition] [167]          | 172 |

| CYCLIPSONIC [171]                                         | 178 |

|                                                           | 179 |

| Atari 2600 [178]                                          | 180 |

| MAC [192]       184         DPMU [194]       187         7 Segment Decode [196]       190         PS2 Decoder [198]       194         Super Mario Tune on A Piezo Speaker [200]       196         AES Inverse S-box [202]       199         TT08 - experiments with latch-based shift registers [204]       200         Obstacle Detection [206]       202         resfuzzy [208]       204         CEJMU Beers and Adders [210]       206         RGBW Color Processor [225]       208         Stochastic Multiplier, Adder and Self-Multiplier [227]       214         DL float MAC [229]       219         schoolRISCV CPU with Fibonacci program [231]       222         Rounding error [233]       224         SIC-1 8-bit SUBLEQ Single Instruction Computer [234]       226         Sea Battle [235]       229         Comm_IC [237]       231         16 Mic Beamformer [239]       233         PDM Pitch Filter [241]       234         Zoom Zoon [242]       236         PDM Orrelator [243]       244         Sequential Shadows Deluxe [TT08 demo competition] [262]       244         Sequential Shadows Deluxe [TT08 demo competition] [262]       244         Supermic [275]       255                       | SPI FPU [179]                                             | 181 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-----|

| DPMU [194]       187         7 Segment Decode [196]       190         PS2 Decoder [198]       194         Super Mario Tune on A Piezo Speaker [200]       196         AES Inverse S-box [202]       199         TT08 - experiments with latch-based shift registers [204]       200         Obstacle Detection [206]       202         resfuzzy [208]       204         CEJMU Beers and Adders [210]       206         RGBW Color Processor [225]       208         Stochastic Multiplier, Adder and Self-Multiplier [227]       214         DL float MAC [229]       219         schoolRISCV CPU with Fibonacci program [231]       222         Rounding error [233]       224         SIC-1 8-bit SUBLEQ Single Instruction Computer [234]       226         Sea Battle [235]       229         Comm_LC [237]       231         16 Mic Beamformer [239]       233         PDM Pitch Filter [241]       234         Zoom Zoom [242]       236         PDM Correlator [243]       244         Sequential Shadows Deluxe [TT08 demo competition] [262]       244         Supermic [275]       254         DPM_Unit [289]       255         Generate VGA output for Color Blindness Test [291]       255                      |                                                           | 184 |

| 7 Segment Decode [196]       190         PS2 Decoder [198]       194         Super Mario Tune on A Piezo Speaker [200]       196         AES Inverse S-box [202]       199         TO8 – experiments with latch-based shift registers [204]       200         Obstacle Detection [206]       202         resfuzzy [208]       204         CEJMU Beers and Adders [210]       206         RGBW Color Processor [225]       208         Stochastic Multiplier, Adder and Self-Multiplier [227]       214         DL float MAC [229]       219         schoolRISCV CPU with Fibonacci program [231]       222         Rounding error [233]       224         SIC-1 8-bit SUBLEQ Single Instruction Computer [234]       226         Sea Battle [235]       229         Comm_LC [237]       231         Obm Correlator [243]       234         Zoom Zoom [242]       236         PDM Orrelator [243]       244         Sequential Shadows Deluxe [TT08 demo competition] [262]       244         Sequential Shadows Deluxe [TT08 demo competition] [262]       244         DDC [266]       249         mulmul [270]       250         Warp [274]       252         Supermic [275]       254 <tr< td=""><td></td><td></td></tr<> |                                                           |     |

| PS2 Decoder [198]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                           | 190 |

| Super Mario Tune on A Piezo Speaker [200]       196         AES Inverse S-box [202]       199         TT08 - experiments with latch-based shift registers [204]       200         Obstacle Detection [206]       202         resfuzzy [208]       204         CEJMU Beers and Adders [210]       206         RGBW Color Processor [225]       208         Stochastic Multiplier, Adder and Self-Multiplier [227]       214         DL float MAC [229]       219         schoolRISCV CPU with Fibonacci program [231]       222         Rounding error [233]       224         SIC-1 8-bit SUBLEQ Single Instruction Computer [234]       226         Sea Battle [235]       229         Comm_IC [237]       231         16 Mic Beamformer [239]       233         PDM Pitch Filter [241]       234         Zoom Zoom [242]       236         PDM Correlator [243]       241         SPI Logic Analyzer with Charlieplexed Display [258]       242         Find The Damn Issue [259]       244         Sequential Shadows Deluxe [TT08 demo competition] [262]       246         DDC [266]       249         mulmul [270]       255         Generate VGA output for Color Blindness Test [291]       258         4-bit C     | · · ·                                                     | 194 |

| AES Inverse S-box [202]       199         TT08 - experiments with latch-based shift registers [204]       200         Obstacle Detection [206]       202         resfuzzy [208]       204         CEJMU Beers and Adders [210]       206         RGBW Color Processor [225]       208         Stochastic Multiplier, Adder and Self-Multiplier [227]       214         DL float MAC [229]       219         schoolRISCV CPU with Fibonacci program [231]       222         Rounding error [233]       224         SIC-1 8-bit SUBLEQ Single Instruction Computer [234]       226         Sea Battle [235]       229         Comm_IC [237]       231         16 Mic Beamformer [239]       233         PDM Pitch Filter [241]       234         Zoom Zoom [242]       236         PDM Correlator [243]       241         SPI Logic Analyzer with Charlieplexed Display [258]       242         Find The Dann Issue [259]       244         Sequential Shadows Deluxe [TT08 demo competition] [262]       246         DDC [266]       249         mulmul [270]       250         Warp [274]       252         Supermic [275]       254         DPM_Unit [289]       255         Genera                                        |                                                           | 196 |

| Obstacle Detection [206]       202         resfuzzy [208]       204         CEJMU Beers and Adders [210]       206         RGBW Color Processor [225]       208         Stochastic Multiplier, Adder and Self-Multiplier [227]       214         DL float MAC [229]       219         schoolRISCV CPU with Fibonacci program [231]       222         Rounding error [233]       224         SIC-1 8-bit SUBLEQ Single Instruction Computer [234]       226         Sea Battle [235]       229         Comm_IC [237]       231         16 Mic Beamformer [239]       233         PDM Pitch Filter [241]       234         Zoom Zoom [242]       236         PDM Orrelator [243]       241         SPI Logic Analyzer with Charlieplexed Display [258]       242         Find The Damn Issue [259]       244         Sequential Shadows Deluxe [TT08 demo competition] [262]       246         DDC [266]       249         mulmul [270]       255         Generate VGA output for Color Blindness Test [291]       258         4-bit CLA [293]       259         SkyKing Demo [295]       260         Flame demo [297]       261         Metaballs [299]       263         Simple Stop                                        |                                                           | 199 |

| resfuzzy [208]       204         CEJMU Beers and Adders [210]       206         RGBW Color Processor [225]       208         Stochastic Multiplier, Adder and Self-Multiplier [227]       214         DL float MAC [229]       219         schoolRISCV CPU with Fibonacci program [231]       222         Rounding error [233]       224         SIC-1 8-bit SUBLEQ Single Instruction Computer [234]       226         Sea Battle [235]       229         Comm_IC [237]       231         16 Mic Beamformer [239]       233         PDM Pitch Filter [241]       234         Zoom Zoom [242]       236         PDM Ocrrelator [243]       241         SPI Logic Analyzer with Charlieplexed Display [258]       242         Find The Damn Issue [259]       244         Sequential Shadows Deluxe [TT08 demo competition] [262]       246         DDC [266]       249         mulmul [270]       250         Warp [274]       255         Generate VGA output for Color Blindness Test [291]       258         4-bit CLA [293]       259         SkyKing Demo [295]       260         Flame demo [297]       261         Metaballs [299]       261         Metaballs [299]                                                 | TT08 - experiments with latch-based shift registers [204] | 200 |

| CEJMU Beers and Adders [210]       206         RGBW Color Processor [225]       208         Stochastic Multiplier, Adder and Self-Multiplier [227]       214         DL float MAC [229]       219         schoolRISCV CPU with Fibonacci program [231]       222         Rounding error [233]       224         SIC-1 8-bit SUBLEQ Single Instruction Computer [234]       226         Sea Battle [235]       229         Comm_IC [237]       231         16 Mic Beamformer [239]       233         PDM Pitch Filter [241]       234         Zoom Zoom [242]       236         PDM Ocrrelator [243]       244         Sequential Shadows Deluxe [TT08 demo competition] [262]       246         DDC [266]       249         mulmul [270]       255         Supermic [275]       254         DPM_Unit [289]       255         Supermic [275]       254         DPM_Unit [289]       255         SkyKing Demo [295]       260         Flame demo [297]       261         Metaballs [299]       261         Metaballs [299]       261         Metaballs [291]       263         Simple Stopwatch [301]       264         PWM generator [303]                                                                                   | Obstacle Detection [206]                                  | 202 |

| RGBW Color Processor [225]       208         Stochastic Multiplier, Adder and Self-Multiplier [227]       214         DL float MAC [229]       219         schoolRISCV CPU with Fibonacci program [231]       222         Rounding error [233]       224         SIC-1 8-bit SUBLEQ Single Instruction Computer [234]       226         Sea Battle [235]       229         Comm_IC [237]       231         16 Mic Beamformer [239]       233         PDM Pitch Filter [241]       234         Zoom Zoom [242]       236         PDM Correlator [243]       244         SPI Logic Analyzer with Charlieplexed Display [258]       242         Find The Damn Issue [259]       244         Sequential Shadows Deluxe [TT08 demo competition] [262]       246         DDC [266]       249         mulmul [270]       250         Warp [274]       252         Supermic [275]       254         DPM_Unit [289]       255         Generate VGA output for Color Blindness Test [291]       258         4-bit CLA [293]       250         SkyKing Demo [297]       261         Metaballs [299]       261         Metaballs [299]       263         Simple Stopwatch [301]       2                                                 |                                                           | 204 |

| Stochastic Multiplier, Adder and Self-Multiplier [227]       214         DL float MAC [229]       219         schoolRISCV CPU with Fibonacci program [231]       222         Rounding error [233]       224         SIC-1 8-bit SUBLEQ Single Instruction Computer [234]       226         Sea Battle [235]       229         Comm_IC [237]       231         16 Mic Beamformer [239]       233         PDM Pitch Filter [241]       234         Zoom Zoom [242]       236         PDM Correlator [243]       241         SPI Logic Analyzer with Charlieplexed Display [258]       242         Find The Damn Issue [259]       244         Sequential Shadows Deluxe [TT08 demo competition] [262]       246         DDC [266]       249         mulmul [270]       250         Warp [274]       252         Supermic [275]       254         DPM_Unit [289]       255         Generate VGA output for Color Blindness Test [291]       258         4-bit CLA [293]       250         SkyKing Demo [297]       261         Metaballs [299]       263         Simple Stopwatch [301]       264         PWM generator [303]       266         DMTD [305]       268                                                           | CEJMU Beers and Adders [210]                              | 206 |

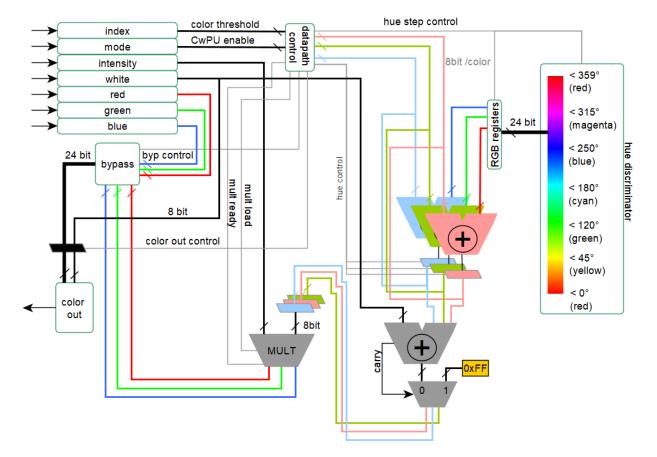

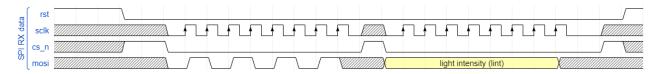

| DL float MAC [229]       219         schoolRISCV CPU with Fibonacci program [231]       222         Rounding error [233]       224         SIC-1 8-bit SUBLEQ Single Instruction Computer [234]       226         Sea Battle [235]       229         Comm_IC [237]       231         16 Mic Beamformer [239]       233         PDM Pitch Filter [241]       234         Zoom Zoom [242]       236         PDM Correlator [243]       244         SPI Logic Analyzer with Charlieplexed Display [258]       242         Find The Damn Issue [259]       244         Sequential Shadows Deluxe [TT08 demo competition] [262]       246         DDC [266]       249         mulmul [270]       250         Warp [274]       255         Generate VGA output for Color Blindness Test [291]       258         4-bit CLA [293]       259         SkyKing Demo [295]       260         Flame demo [297]       261         Metaballs [299]       263         Simple Stopwatch [301]       264         PWM generator [303]       266                                                                                                                                                                                                |                                                           | 208 |

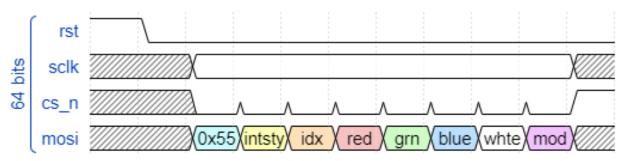

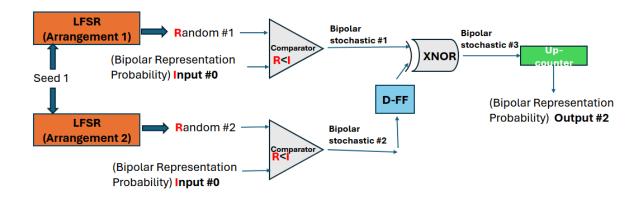

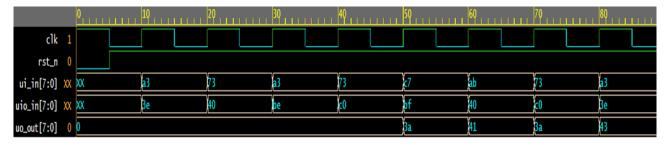

| schoolRISCV CPU with Fibonacci program [231]       222         Rounding error [233]       224         SIC-1 8-bit SUBLEQ Single Instruction Computer [234]       226         Sea Battle [235]       229         Comm_IC [237]       231         16 Mic Beamformer [239]       233         PDM Pitch Filter [241]       234         Zoom Zoom [242]       236         PDM Correlator [243]       241         SPI Logic Analyzer with Charlieplexed Display [258]       242         Find The Damn Issue [259]       244         Sequential Shadows Deluxe [TT08 demo competition] [262]       246         DDC [266]       249         mulmul [270]       255         Supermic [275]       255         Generate VGA output for Color Blindness Test [291]       258         4-bit CLA [293]       259         SkyKing Demo [295]       260         Flame demo [297]       261         Metaballs [299]       263         Simple Stopwatch [301]       264         PWM generator [303]       266                                                                                                                                                                                                                                 | Stochastic Multiplier, Adder and Self-Multiplier [227]    | 214 |

| Rounding error [233]       224         SIC-1 8-bit SUBLEQ Single Instruction Computer [234]       226         Sea Battle [235]       229         Comm_IC [237]       231         16 Mic Beamformer [239]       233         PDM Pitch Filter [241]       234         Zoom Zoom [242]       236         PDM Orrelator [243]       241         SPI Logic Analyzer with Charlieplexed Display [258]       242         Find The Damn Issue [259]       244         Sequential Shadows Deluxe [TT08 demo competition] [262]       246         DDC [266]       249         mulmul [270]       250         Warp [274]       252         Supermic [275]       254         DPM_Unit [289]       255         Generate VGA output for Color Blindness Test [291]       258         4-bit CLA [293]       250         SkyKing Demo [295]       260         Flame demo [297]       261         Metaballs [299]       261         Metaballs [299]       263         Simple Stopwatch [301]       264         PWM generator [303]       266         DMTD [305]       268                                                                                                                                                                    | DL float MAC [229]                                        | 219 |

| SIC-1 8-bit SUBLEQ Single Instruction Computer [234]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | schoolRISCV CPU with Fibonacci program [231]              | 222 |

| Sea Battle [235]       229         Comm_IC [237]       231         16 Mic Beamformer [239]       233         PDM Pitch Filter [241]       234         Zoom Zoom [242]       236         PDM Correlator [243]       241         SPI Logic Analyzer with Charlieplexed Display [258]       242         Find The Damn Issue [259]       244         Sequential Shadows Deluxe [TT08 demo competition] [262]       246         DDC [266]       249         mulmul [270]       250         Warp [274]       252         Supermic [275]       254         DPM_Unit [289]       255         Generate VGA output for Color Blindness Test [291]       258         4-bit CLA [293]       259         SkyKing Demo [295]       260         Flame demo [297]       261         Metaballs [299]       263         Simple Stopwatch [301]       264         PWM generator [303]       266         DMTD [305]       268                                                                                                                                                                                                                                                                                                                   | Rounding error [233]                                      | 224 |

| Comm_IC [237]       231         16 Mic Beamformer [239]       233         PDM Pitch Filter [241]       234         Zoom Zoom [242]       236         PDM Correlator [243]       241         SPI Logic Analyzer with Charlieplexed Display [258]       242         Find The Damn Issue [259]       244         Sequential Shadows Deluxe [TT08 demo competition] [262]       246         DDC [266]       249         mulmul [270]       250         Warp [274]       252         Supermic [275]       254         DPM_Unit [289]       255         Generate VGA output for Color Blindness Test [291]       258         4-bit CLA [293]       250         SkyKing Demo [295]       260         Flame demo [297]       261         Metaballs [299]       263         Simple Stopwatch [301]       264         PWM generator [303]       266         DMTD [305]       268                                                                                                                                                                                                                                                                                                                                                      | SIC-1 8-bit SUBLEQ Single Instruction Computer [234]      | 226 |

| Comm_IC [237]       231         16 Mic Beamformer [239]       233         PDM Pitch Filter [241]       234         Zoom Zoom [242]       236         PDM Correlator [243]       241         SPI Logic Analyzer with Charlieplexed Display [258]       242         Find The Damn Issue [259]       244         Sequential Shadows Deluxe [TT08 demo competition] [262]       246         DDC [266]       249         mulmul [270]       250         Warp [274]       252         Supermic [275]       254         DPM_Unit [289]       255         Generate VGA output for Color Blindness Test [291]       258         4-bit CLA [293]       250         SkyKing Demo [295]       260         Flame demo [297]       261         Metaballs [299]       263         Simple Stopwatch [301]       264         PWM generator [303]       266         DMTD [305]       268                                                                                                                                                                                                                                                                                                                                                      | Sea Battle [235]                                          | 229 |

| PDM Pitch Filter [241]       234         Zoom Zoom [242]       236         PDM Correlator [243]       241         SPI Logic Analyzer with Charlieplexed Display [258]       242         Find The Damn Issue [259]       244         Sequential Shadows Deluxe [TT08 demo competition] [262]       246         DDC [266]       249         mulmul [270]       250         Warp [274]       252         Supermic [275]       254         DPM_Unit [289]       255         Generate VGA output for Color Blindness Test [291]       258         4-bit CLA [293]       259         SkyKing Demo [295]       260         Flame demo [297]       261         Metaballs [299]       263         Simple Stopwatch [301]       264         PWM generator [303]       266         DMTD [305]       268                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                           | 231 |

| Zoom Zoom [242]       236         PDM Correlator [243]       241         SPI Logic Analyzer with Charlieplexed Display [258]       242         Find The Damn Issue [259]       244         Sequential Shadows Deluxe [TT08 demo competition] [262]       246         DDC [266]       249         mulmul [270]       250         Warp [274]       252         Supermic [275]       254         DPM_Unit [289]       255         Generate VGA output for Color Blindness Test [291]       258         4-bit CLA [293]       259         SkyKing Demo [295]       260         Flame demo [297]       261         Metaballs [299]       263         Simple Stopwatch [301]       264         PWM generator [303]       266         DMTD [305]       268                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                           | 233 |

| PDM Correlator [243]       241         SPI Logic Analyzer with Charlieplexed Display [258]       242         Find The Damn Issue [259]       244         Sequential Shadows Deluxe [TT08 demo competition] [262]       246         DDC [266]       249         mulmul [270]       250         Warp [274]       252         Supermic [275]       254         DPM_Unit [289]       255         Generate VGA output for Color Blindness Test [291]       258         4-bit CLA [293]       259         SkyKing Demo [295]       260         Flame demo [297]       261         Metaballs [299]       263         Simple Stopwatch [301]       264         PWM generator [303]       266         DMTD [305]       268                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                           | 234 |

| SPI Logic Analyzer with Charlieplexed Display [258]       242         Find The Damn Issue [259]       244         Sequential Shadows Deluxe [TT08 demo competition] [262]       246         DDC [266]       249         mulmul [270]       250         Warp [274]       252         Supermic [275]       254         DPM_Unit [289]       255         Generate VGA output for Color Blindness Test [291]       259         SkyKing Demo [295]       260         Flame demo [297]       261         Metaballs [299]       263         Simple Stopwatch [301]       264         PWM generator [303]       266         DMTD [305]       268                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Zoom Zoom [242]                                           | 236 |

| Find The Damn Issue [259]       244         Sequential Shadows Deluxe [TT08 demo competition] [262]       246         DDC [266]       249         mulmul [270]       250         Warp [274]       252         Supermic [275]       254         DPM_Unit [289]       255         Generate VGA output for Color Blindness Test [291]       258         4-bit CLA [293]       259         SkyKing Demo [295]       260         Flame demo [297]       261         Metaballs [299]       263         Simple Stopwatch [301]       264         PWM generator [303]       268                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                           | 241 |

| Sequential Shadows Deluxe [TT08 demo competition] [262]       246         DDC [266]       249         mulmul [270]       250         Warp [274]       252         Supermic [275]       254         DPM_Unit [289]       255         Generate VGA output for Color Blindness Test [291]       258         4-bit CLA [293]       259         SkyKing Demo [295]       260         Flame demo [297]       261         Metaballs [299]       263         Simple Stopwatch [301]       264         PWM generator [303]       266         DMTD [305]       268                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SPI Logic Analyzer with Charlieplexed Display [258]       | 242 |

| Sequential Shadows Deluxe [TT08 demo competition] [262]       246         DDC [266]       249         mulmul [270]       250         Warp [274]       252         Supermic [275]       254         DPM_Unit [289]       255         Generate VGA output for Color Blindness Test [291]       258         4-bit CLA [293]       259         SkyKing Demo [295]       260         Flame demo [297]       261         Metaballs [299]       263         Simple Stopwatch [301]       264         PWM generator [303]       266         DMTD [305]       268                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Find The Damn Issue [259]                                 | 244 |

| mulmul [270]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                           | 246 |

| Warp [274]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DDC [266]                                                 | 249 |

| Supermic [275]       254         DPM_Unit [289]       255         Generate VGA output for Color Blindness Test [291]       258         4-bit CLA [293]       259         SkyKing Demo [295]       260         Flame demo [297]       261         Metaballs [299]       263         Simple Stopwatch [301]       264         PWM generator [303]       266         DMTD [305]       268                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | mulmul [270]                                              | 250 |

| DPM_Unit [289]       255         Generate VGA output for Color Blindness Test [291]       258         4-bit CLA [293]       259         SkyKing Demo [295]       260         Flame demo [297]       261         Metaballs [299]       263         Simple Stopwatch [301]       264         PWM generator [303]       266         DMTD [305]       268                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Warp [274]                                                | 252 |

| Generate VGA output for Color Blindness Test [291]       258         4-bit CLA [293]       259         SkyKing Demo [295]       260         Flame demo [297]       261         Metaballs [299]       263         Simple Stopwatch [301]       264         PWM generator [303]       266         DMTD [305]       268                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Supermic [275]                                            | 254 |

| 4-bit CLA [293]       259         SkyKing Demo [295]       260         Flame demo [297]       261         Metaballs [299]       263         Simple Stopwatch [301]       264         PWM generator [303]       266         DMTD [305]       268                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DPM_Unit [289]                                            | 255 |

| SkyKing Demo [295]       260         Flame demo [297]       261         Metaballs [299]       263         Simple Stopwatch [301]       264         PWM generator [303]       266         DMTD [305]       268                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                           |     |

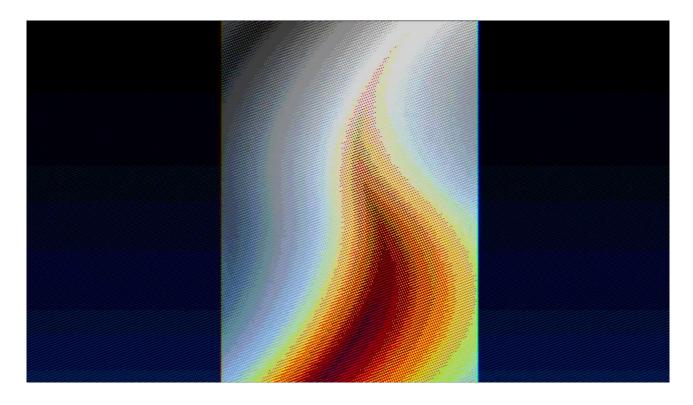

| Flame demo [297]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-bit CLA [293]                                           | 259 |

| Flame demo [297]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SkyKing Demo [295]                                        | 260 |

| Metaballs [299]       263         Simple Stopwatch [301]       264         PWM generator [303]       266         DMTD [305]       268                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                           |     |

| Simple Stopwatch [301]       264         PWM generator [303]       266         DMTD [305]       268                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                           |     |

| PWM generator [303]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                           |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                           |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | - • •                                                     |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | I2S to PWM [307]                                          |     |

| Basys 3 Over UART Link [322]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                           |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ITS-RISCV [326]                                           |     |

| 11.5-KL5UV 15/01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                           |     |

| Zilog Z80 [330]                           | 275 |

|-------------------------------------------|-----|

| 2048 sliding tile puzzle game (VGA) [334] | 279 |

|                                           | 281 |

| Space Invaders ASIC [338]                 | 283 |

|                                           | 284 |

|                                           | 286 |

|                                           | 287 |

|                                           | 288 |

|                                           | 289 |

|                                           | 290 |

|                                           | 292 |

|                                           | 294 |

|                                           | 296 |

|                                           | 301 |

|                                           | 306 |

|                                           | 309 |

|                                           | 311 |

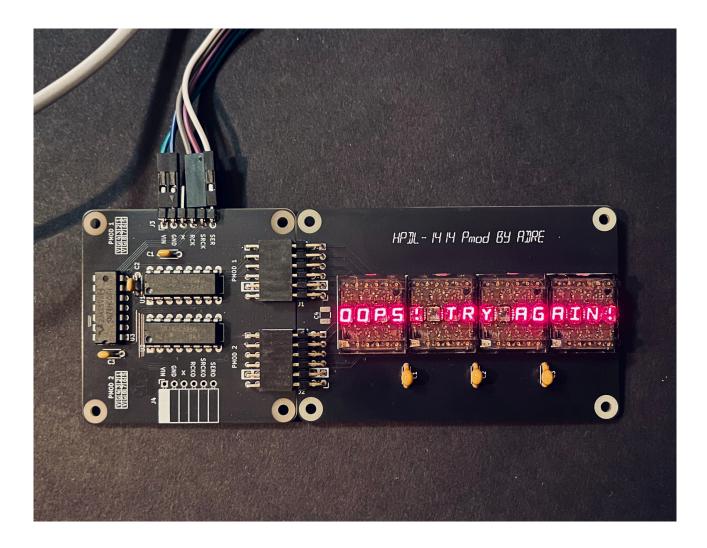

| TT10 HPDL 1414 Uart [389]                 | 314 |

|                                           | 317 |

|                                           | 319 |

|                                           | 320 |

|                                           | 321 |

|                                           | 323 |

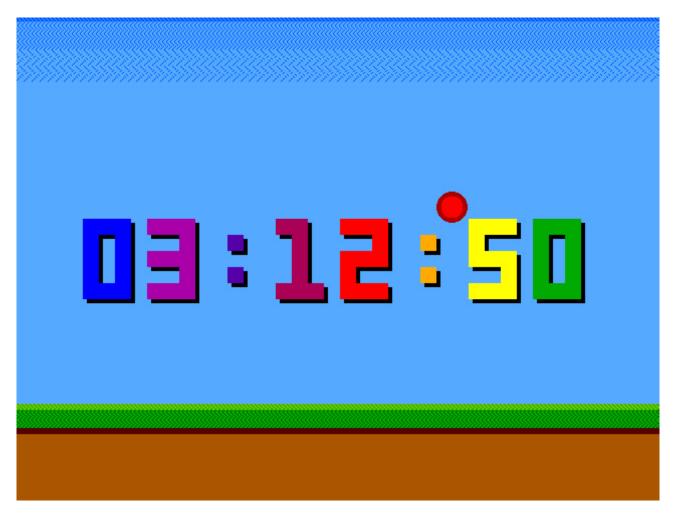

| TT10_Luke_Clock [401]                     | 324 |

| SSMCI [403]                               | 328 |

| Configurable Logic Block [416]            | 330 |

| Gamepad Pmod Demo [417]                   | 332 |

| 4-bit up/down binary counter [418]        | 334 |

| 6Digit7SegClock [419]                     | 336 |

| Team 17's 8 bit DAC [420]                 | 338 |

| MAC Operation [421]                       | 339 |

| Tiny Registers [422]                      | 340 |

| Xor-Logic [423]                           | 345 |

| Leaky Integrate Fire Neuron [424]         | 346 |

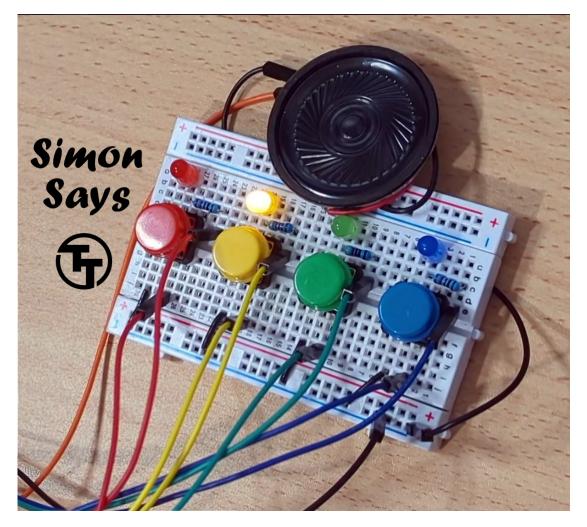

| Simon Says memory game [425]              | 348 |

| Tiny Tapeout Group 7 Lab D [426]          | 351 |

| SPI 7-segment display [427]               | 353 |

| 8-bit-CARRY_SKIP [428]                    | 355 |

| AtomNPU [429]                             | 357 |

| Semana UCU Verilog [430]                  | 361 |

| Enigma - 52-bit Key Length [431]          |     |

| Frequency Encoder and Decoder [432]       |     |

| synth_simple [433]                                             | 375 |

|----------------------------------------------------------------|-----|

| carry skip adder [434]                                         | 376 |

| VGA clock [435]                                                | 378 |

| Crossyroad [449]                                               | 380 |

| zc-sushi-demo [451]                                            | 381 |

| kch cd101 [453]                                                | 382 |

| SimpleSPIdev [455]                                             | 384 |

| RNG_test [457]                                                 | 385 |

| 15bit GCD [459]                                                | 386 |

| XY Spacewar [461]                                              | 388 |

| 16-bit Logarithmic Approximate Floating Point Multiplier [463] | 389 |

| TT_spiralPattern [465]                                         | 392 |

| ledtest [467]                                                  | 393 |

| I2C and SPI [480]                                              | 394 |

| VGA Screensaver with Tiny Tapeout Logo [481]                   | 395 |

| Perceptron Neuron [482]                                        | 397 |

| SPI test [483]                                                 | 398 |

| Histogramming [484]                                            | 399 |

| Huffmann_Coder [485]                                           | 402 |

| RLE Video Player [486]                                         | 403 |

| Vedic multiplier [487]                                         | 406 |

| 8-Bit CPU [488]                                                | 407 |

| Tiny piano [489]                                               | 422 |

| carry_select [490]                                             | 424 |

| Asynchronous I2C Registerfile Interface [491]                  | 426 |

| test_friday2 [492]                                             | 427 |

| Тарри [493]                                                    | 431 |

| Perceptron [494]                                               | 432 |

| mp_LIF_neuron [495]                                            | 433 |

| Hopfield Network with Izhikevich-type RS and FS Neurons [496]  | 434 |

| digital LIF Neuron [497]                                       | 435 |

| Tinysynth [498]                                                | 436 |

| Hero on Tape [499]                                             | 437 |

| 16 Bit Izhikevich Neuron [512]                                 | 438 |

| dff_mem [514]                                                  | 441 |

| Verilog ring oscillator V2 [516]                               | 444 |

| Basic model for Systollic array implementation of LIF [518]    | 446 |

| Leaky integrate and fire spiking neural network [520]          | 448 |

| tinydsp-lol [522]                                              | 449 |

| Shifter [524]                                                  | 450 |

| LRC - Longitudinal Redundancy Check generator [526]            | 451 |

| Workshop demo [528]                                            | 452 |

| A Tale of Two NCOs [530]                                       | 453 |

|----------------------------------------------------------------|-----|

| Wokwi Group #7 [544]                                           | 455 |

| Wokwi Group $\#6$ [546]                                        | 456 |

| Wokwi Group #5 [548]                                           | 457 |

| Wokwi Group #4 [550]                                           | 458 |

| Wokwi Group #3 [552]                                           | 459 |

| Wokwi Group #2 [554]                                           | 460 |

| Wokwi Group #1 [556]                                           | 461 |

| Will It NAND? [558]                                            | 462 |

| sphereinabox hello [560]                                       | 463 |

| L display [562]                                                | 464 |

| 7-Segment Digital Desk Clock [576]                             | 466 |

| Basic Perceptron + ReLU [578]                                  | 468 |

| Basic Matrix-Vector Multiplication [580]                       |     |

| 8 bit MAC Unit [582]                                           |     |

| Programmable PWM Generator [584]                               |     |

| Verilog test project [586]                                     |     |

| Basic LIF Neuron [588]                                         |     |

| Integrate-and-Fire Neuron Circuit [590]                        |     |

| Michaels Tiny Tapeout ALU [592]                                |     |

| 8-bit CBILBO [594]                                             |     |

| Wokwi Group $\frac{1}{48}$ [608]                               |     |

| Wokwi Group $\#9$ [610]                                        |     |

| Wokwi Group $\#10$ [612]                                       |     |

| Wokwi Group $\#11$ [614]                                       |     |

| Wokwi Group $\#12$ [616]                                       |     |

| triggerer [618]                                                |     |

| Wokwi Group #13 [620]                                          |     |

| Multiplier Group $\#1$ [622]                                   |     |

| Multiplier Group $\#2$ [624]                                   |     |

| Multiplier Group $\#3$ [626]                                   |     |

| Ternary 128-element Dot Product [640]                          |     |

| GUS16 CPU [642]                                                |     |

| Warp [644]                                                     |     |

| VGA Drop (audio/visual demo) [646]                             |     |

| Classic 8-bit era Programmable Sound Generator AY-3-8913 [648] |     |

| SoCET UART with FIFO buffers [650]                             |     |

| Simon's Caterpillar [652]                                      |     |

| Stochastic Integrator [654]                                    |     |

| $E2M0 \times INT8$ Systolic Array [656]                        |     |

| VGA Nyan Cat [658]                                             |     |

| Collatz conjecture brute-forcer [673]                          |     |

|                                                                | 911 |

| APA102 to WS2812 Translator [675]                              | 519  |

|----------------------------------------------------------------|------|

| pio-ram-emulator example: Julia fractal [677]                  | 521  |

| Tiny Neural Network Accelerator [678]                          | 524  |

| Fuzzy Search Engine [679]                                      | 527  |

| VGA Pride [681]                                                |      |

| donut [683]                                                    |      |

| UART [685]                                                     |      |

| Why not? [687]                                                 |      |

| FSK Modem + HDLC + UART (PoC) [689]                            |      |

| Spectrogram extractor, 2 channels [690]                        |      |

| Bouncy Capsule [691]                                           |      |

| TinyTapeout Minimal Branch Predictor [704]                     |      |

| Moody-mimosa [706]                                             |      |

| Classic 8-bit era Programmable Sound Generator AY-3-8913 [708] |      |

| Orion Iron Ion [TT10 demo competition] [710]                   |      |

| My Project [712]                                               |      |

| simple-viii [714]                                              |      |

| ttUART [716]                                                   |      |

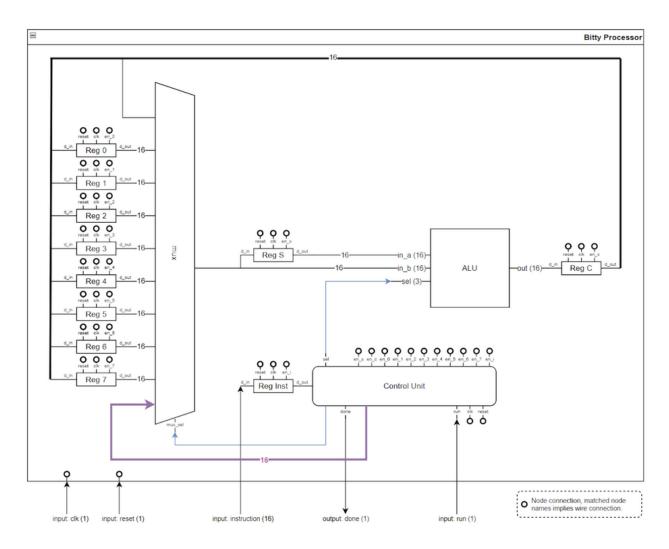

| Bitty [718]                                                    |      |

| IHP VGA demo [720]                                             |      |

| UW ASIC - Optimized Dino [722]                                 |      |

| PID Controller [737]                                           |      |

| Frequency Counter SSD1306 OLED [739]                           |      |

| Tiny 1-bit AM Radio [741]                                      |      |

| FIREngine [743]                                                |      |

| znah_vga_ca [745]                                              |      |

| TRNG [746]                                                     |      |

| CORA-16 [747]                                                  |      |

| T3 (Tiny Ternary Tapeout) CSA [749]                            |      |

| Basic Oszilloscope and Signal Generator [751]                  |      |

| 1bit_am_sdr [752]                                              |      |

| 15 channels emission counter [753]                             | 619  |

| VGA Pong with NES Controllers [754]                            |      |

| Tiny RAM DFF 2r1w [755]                                        |      |

| Sprite Bouncer with Looping Background Options [768]           |      |

| Glyph Mode [769]                                               |      |

| VGA Scroller [771]                                             |      |

| DDR throughput and flop aperature test [773]                   |      |

| Wildcat RISC-V [774]                                           |      |

| Calculator [775]                                               |      |

| Crispy VGA [777]                                               |      |

| asic design is my passion [779]                                |      |

|                                                                | 0.00 |

| TinyQV Risc-V SoC [780]                                                  | 639 |

|--------------------------------------------------------------------------|-----|

| Dice [781]                                                               | 643 |

| 4-bit minicomputer ALU [783]                                             | 644 |

| RGB Mixer demo5 [785]                                                    | 645 |

| AlphaOneSoC [786]                                                        | 646 |

| Asynchronous Multiplier [787]                                            | 647 |

| Hamming Code (7,4) [801]                                                 | 650 |

| Space Detective Maze Explorer [803]                                      | 655 |

| Senol Gulgonul tt09 [805]                                                | 657 |

| 4 bit ALU [807]                                                          | 658 |

| Elevator Design [809]                                                    | 660 |

| LED Bitserial Cipher [811]                                               | 661 |

| freqSweep [813]                                                          | 664 |

| Simple PWM Module [815]                                                  | 669 |

| INTERCAL ALU [817]                                                       | 670 |

| Universal Binary to Segment Decoder [819]                                | 674 |

| RO [833]                                                                 | 683 |

| CMOS design of 4-bit Signed Adder Subtractor [835]                       | 685 |

| LaRVa CPU [836]                                                          | 687 |

| Patater Demo Kit Waggling Rainbow on a Chip [837]                        | 689 |

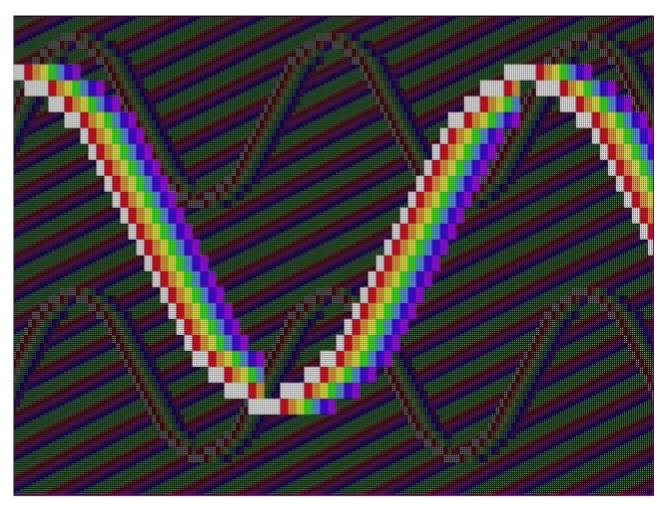

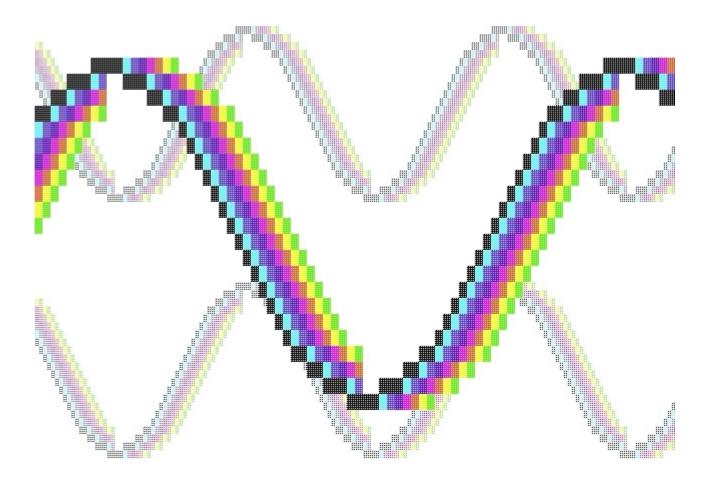

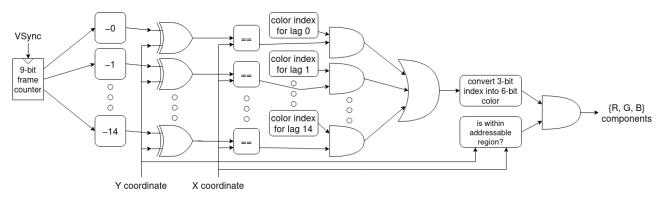

| DemoSiine [839]                                                          | 694 |

| "SQUARE-1": VGA/audio demo [840]                                         | 702 |

| Munch [841]                                                              | 706 |

| cfib Demoscene Entry [843]                                               | 709 |

| VGA donut [844]                                                          | 711 |

| 4-bit ALU [845]                                                          | 713 |

| Morse Code Keyer [847]                                                   | 716 |

| VGA Mandelbrot [848]                                                     |     |

| nVious Graphics [849]                                                    |     |

| TinyMandelbrot [850]                                                     |     |

| 8-Bit Calculator [851]                                                   |     |

| tiny-tapeout-8bit-GPTPrefixCircuit [865]                                 |     |

| LIF on a Ring Topology [867]                                             |     |

| Delta-Sigma ADC Decimation Filter [869]                                  |     |

| an lfsr with synaptic neurons (excitatory or inhibitatory) [871]         |     |

| Perceptron [873]                                                         | 735 |

| Matmul System [875]                                                      | 736 |

| Verilog ring oscillator [877]                                            | 737 |

| Delta RNN and Leaky Integrate-and-Fire Nueron Circuit [879]              | 738 |

| Generador PWM multiproposito con frecuencia y ciclo de trabajo modulable |     |

| [881]                                                                    | 739 |

| Linear Feedback Shift Register [883]                                     |     |

|                                                                          |     |

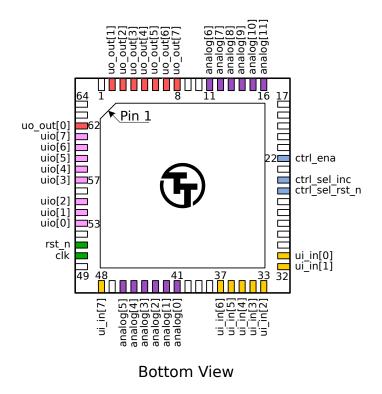

| Pinout                       |     |  |

|------------------------------|-----|--|

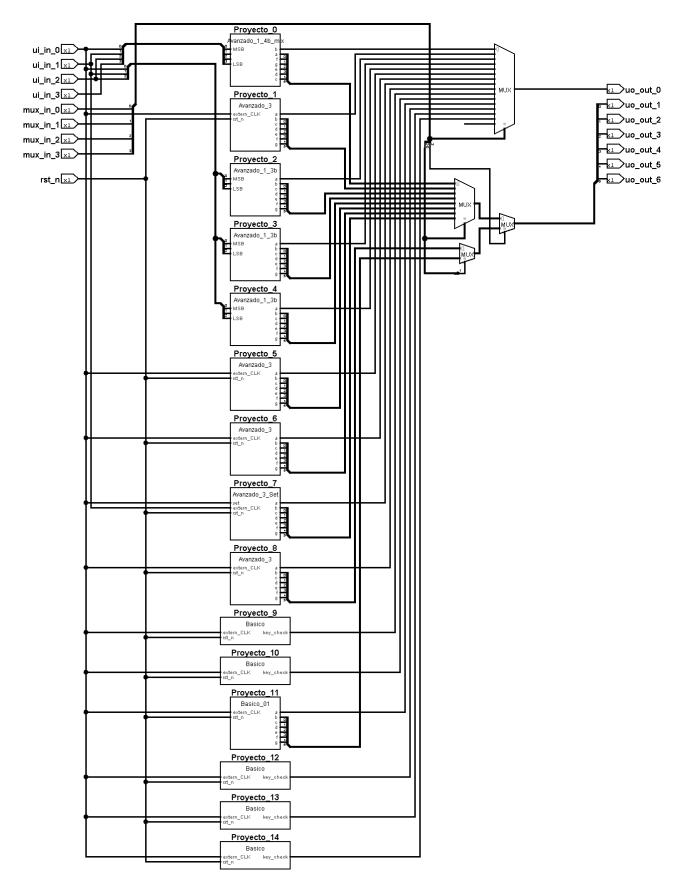

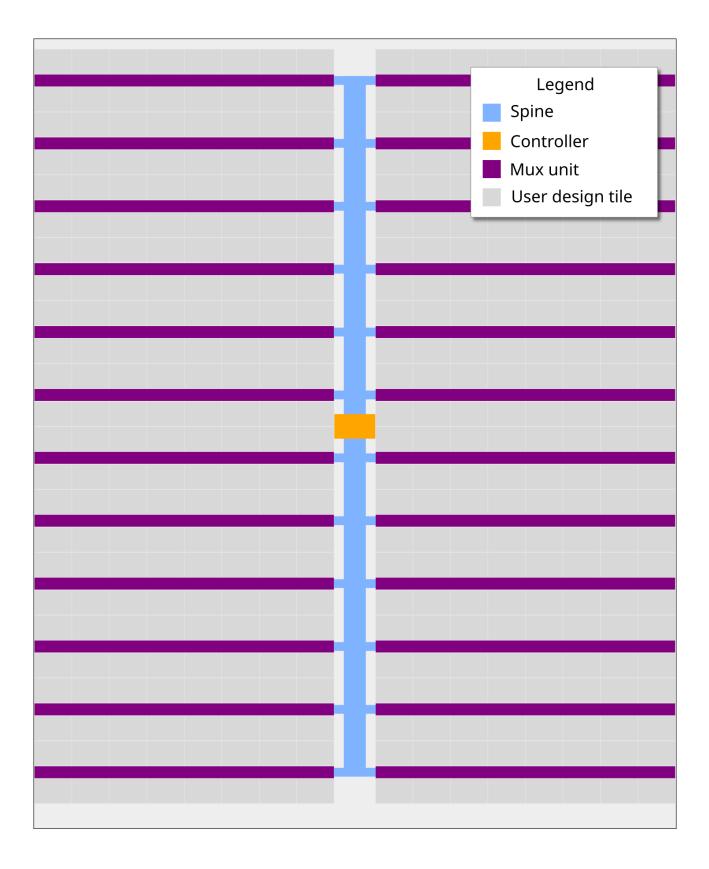

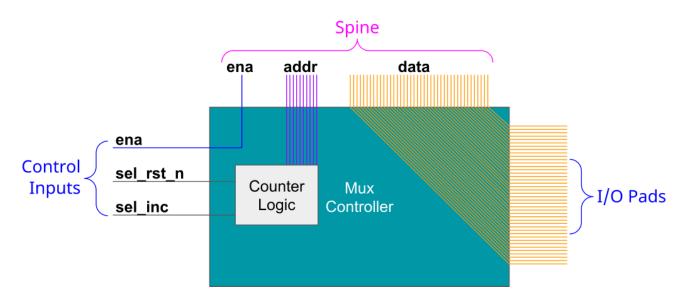

| The Tiny Tapeout Multiplexer | 743 |  |

| Overview                     | 743 |  |

| Operation                    | 743 |  |

| Pinout                       | 747 |  |

| Funding                      | 749 |  |

| Team                         | 749 |  |

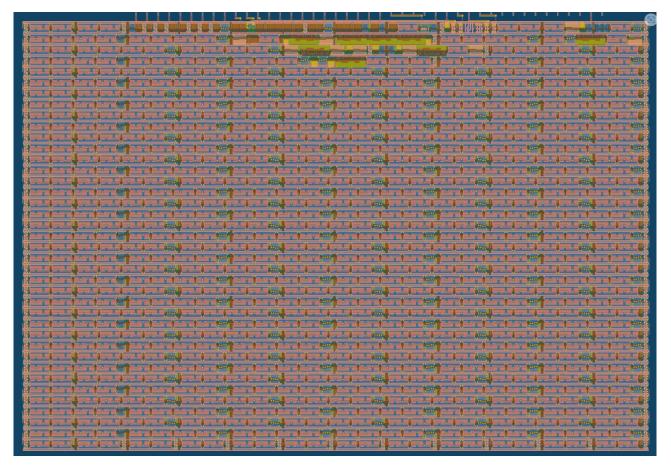

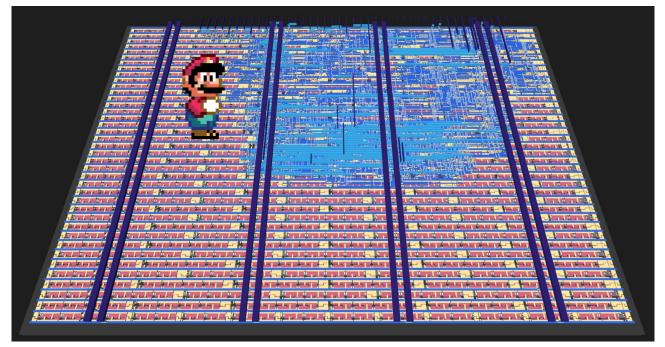

# **Chip renders**

# Full chip render

# Top Metal 1/2

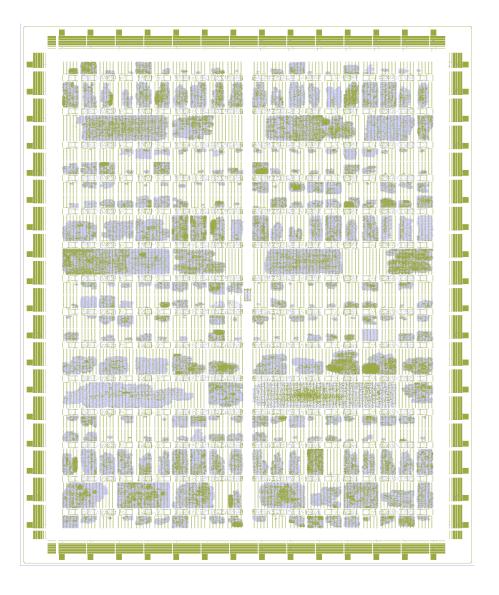

### Logic density view

# Projects

# Chip ROM [0]

- Author: Uri Shaked

- Description: ROM with information about the chip

- GitHub repository

- HDL project

- Mux address: 0

- Extra docs

- Clock: 0 Hz

#### How it works

ROM memory that contains information about the Tiny Tapeout chip. The ROM is 8-bit wide and 256 bytes long.

| Address | Length | Encoding  | Description                                            |